Поняття архітектури мікропроцесора визначає його складові частини, а також зв'язки та взаємодію між ними. Архітектура містить:

1) структурну схему самого МП;

2) програмну модель МП (опис функцій регістрів);

3) інформацію про організацію пам'яті (ємність пам'яті та способи її адресації);

4) опис організації процедур введення-виведення.

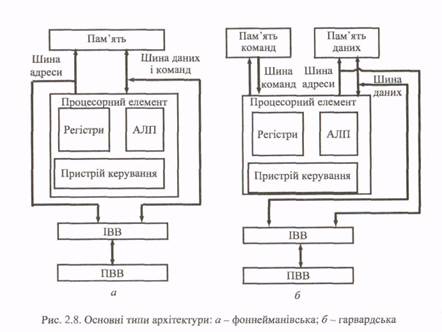

Існують два основні типи архітектури - фоннейманівська та гарвардська. Фоннейманівську архітектуру (рис. 2.8, а) запропонував 1945 року американський математик Джон фон Нейман.

Особливістю цієї архітектури є те, що програма і дані знаходяться у спільній пам'яті, доступ до якої здійснюється по одній шині даних і команд.

Гарвардську архітектуру вперше реалізовано 1944 року в релейній обчислювальній машині Гарвардського університету (США). Особливістю цієї архітектури є те, що пам'ять даних і пам'ять програм розділені та мають окремі шину даних і шину команд (рис. 2.8, б), що дозволяє підвищити швидкодію МП системи.

Структурні схеми обох архітектур містять: процесорний елемент, пам'ять, інтерфейси введення-виведення (ІВВ) і ПВВ. Пам'ять і ПВВ для різних типів МП можуть бути як внутрішніми, тобто розміщуватися на тому ж кристалі, що і процесорний елемент, так і зовнішніми.

Процесорний елемент містить регістри, арифметико-логічний пристрій (АЛП), пристрій керування і виконує функції обробки даних та керування процесами обміну інформацією. Пам'ять забезпечує зберігання кодів команд програми і даних. Інтерфейси призначені для зв'язку з ПВВ (наприклад, з клавіатурою, дисплеєм, друкувальними пристроями, датчиками інформації). Усі елементи структурної схеми з'єднані за допомогою шин.

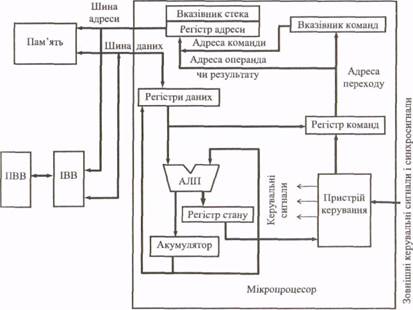

Розширену структурну схему з процесором фоннейманівської архітектури показано на рис. 2.9.

Рис. 2.9. Структурна схема з процесором фоннейманівської архітектури

Схема процесора містить пристрій керування, АЛЛ і регістри: адреси, даних, команд, стану, а також акумулятор, лічильник команд та вказівник стека.

Пристрій керування відповідно до кодів команд та зовнішніх керува-льних сигналів і сигналів синхронізації виробляє керувальні сигнали для нсіх блоків структурної схеми МП, а також керує обміном інформацією між МП, пам'яттю і ПВВ.

Пристрій керування реалізує такі функції:

1. Функція початкового встановлення МП. Зовнішній сигнал початкового встановлення процесора RESET формується при ввімкненні джерела живлення МП або при натисканні кнопки RESET. У разі появи цього сигналу пристрій керування забезпечує завантаження нульового значення у програмний лічильник, що ініціює вибирання з пам'яті байта команди з нульовою адресою. Наприкінці вибирання вміст лічильника команд збільшується на одиницю і вибирається байт команд з наступною адресою. Таким чином виконується вся записана у пам'яті програма.

2. Функція синхронізації. Згідно із зовнішніми керувальними сигналами і сигналами синхросигналізації пристрій керування синхронізує роботу всіх блоків МП.

3. Функція переривань. Із надходженням сигналу переривання пристрій керування ініціює роботу підпрограми обробки відповідного переривання. Потреба у реалізації функцій переривань виникає тоді, коли під час виконання основної програми треба перевести МП на розв'язання іншої задачі, наприклад, обробки аварійної ситуації або роботи з ПВВ.

4. Функція узгодження швидкодії модулів мікропроцесорної системи. Під час обслуговування пам'яті та ПВВ із значно меншою швидкодією, ніж МП, узгодження швидкодії вирішується генерацією тактів очікування МП, а під час обслуговування пристроїв з більшою швидкодією, ніж МП, використовується режим безпосереднього доступу до пам'яті.

Арифметико-логічний пристрій являє собою комбінаційну схему на основі суматора, який сигналами з виходів пристрою керування налагоджується на виконання певної арифметичної або логічної операції: додавання, віднімання, ЛОГІЧНЕ І, ЛОГІЧНЕ АБО, ЛОГІЧНЕ НІ, ВИКЛЮЧНОГО АБО, зсуву, порівняння, десяткової корекції. Отже, АЛП виконує арифметичні або логічні операції над операндами, які пересилаються з пам'яті і(або) регістрів МП.

Операнд - це об'єкт у вигляді значення даних, вмісту регістрів або вмісту комірки пам'яті, з яким оперує команда, наприклад, у команді додавання операндами є доданки. Операнд може задаватися у команді у вигляді числа або знаходитися в регістрі чи комірці пам'яті. Одержаний після виконання команди в АЛП результат пересилається в регістр або комірку пам'яті.

Регістри призначені для зберігання п-розрядного двійкового числа. Вони являють собою n тригерів зі схемами керування читанням/записом та вибірки. Регістри створюють внутрішню пам'ять МП і використовуються для зберігання проміжних результатів обчислень.

Акумулятор - це регістр, у якому зберігається один з операндів. Після виконання команди в акумуляторі замість операнда розмішується результат операції. У 8-розрядних процесорах акумулятор бере участь в усіх операціях АЛП. У 16-розрядних МП більшість команд виконуються без участі акумулятора, але в деяких командах (введення, виведення, множення, ділення) акумулятор діє так само, як і у 8-розрядних МП, тобто зберігає один з операндів, а після виконання команди - результат операції.

Вказівник команд, або програмний лічильник, призначений для зберігання адреси комірки пам'яті, яка містить код наступної команди. Програму дій МП записано в пам'яті у вигляді послідовності кодів команд. Для переходу до наступної команди вміст лічильника збільшується на одиницю у момент вибирання команди з пам'яті. Наприкінці виконання команди в лічильнику команд зберігається адреса наступної команди.

Вказівник стека - це регістр, який зберігає адресу останньої зайнятої комірки стека. Стеком або стековою пам'яттю називається область пам'яті, організованої за принципом «останній прийшов - перший пішов».

Регістр команд зберігає код команди протягом усього часу виконання команди.

Регістр адреси і регістри даних призначені для зберігання адрес і даних, використовуваних під час виконання поточної команди у МП.

Регістр стану або регістр прапорців (ознак) призначений для зберігання інформації про результат операції в АЛП і являє собою декілька тригерів, які набувають одиничних або нульових значень. Наприклад, прапорець нуля встановлюється в одиницю при нульовому результаті операції.

Контрольні запитання

1. Дайте визначення архітектури МП.

2. Яка відмінність між гарвардською та фоннейманівською архітектурами?

3. Які функції виконує пристрій керування?

4. Що визначає вміст вказівника команд? Як він змінюється?

5. Чим відрізняється акумулятор від інших регістрів МП?