В основу побудови МПС систем покладено три принципи: магістральності, модульності, мікропрограмного керування.

Принцип магістральності визначає характер зв'язків між функціональними блоками МПС - усі блоки з'єднуються з єдиною системною шиною.

Принцип магістральності визначає характер зв'язків між функціональними блоками МПС - усі блоки з'єднуються з єдиною системною шиною.

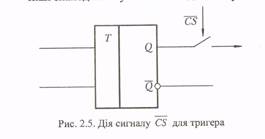

Принцип модульності полягає в тому, що система будується на основі обмеженої кількості типів конструктивно і функціонально завершених модулів. Кожний модуль МПС системи має вхід керування третім (високоімпедансним) станом. Цей вхід називається CS (Chip Select) - вибір кристала або ОЕ (Output Enable) - дозвіл виходу.

Дію сигналу CS для тригера показано на рис. 2.5. Вихідний сигнал тригера Q з'явиться на виводі лише при активному (у цьому випадку - нульовому) рівні сигналу CS. Якщо CS = 1, тригер переводиться у високо-імпедансний стан. Вихід тригера є тристабільним, тобто може знаходитися в одному з трьох станів: логічної одиниці, логічного нуля або у високоімпедансному. У кожний момент часу до системної шини МПС приєднано лише два модулі - той, що приймає, і той, що передає інформацію. Інші знаходяться у високоімпедансному стані. Принципи магістральності та модульності дозволяють нарощувати керувальні й обчислювальні можливості МП через приєднання інших модулів.

Принцип мікропрограмного керування полягає у можливості здійснення елементарних операцій - мікрокоманд (зсуву, пересилання інформації, логічних операцій). Певною комбінацією мікрокоманд можна створити набір команд, який максимально відповідатиме призначенню системи, тобто створити технологічну мову. У секційних процесорах набір мікрокоманд можна змінити, використовуючи інші мікросхеми пам'яті мікрокоманд.

Узагальнену структурну схему МПС показано на рис. 2.6. До складу МПС входять: центральний процесор (ЦП), ПЗП, ОЗП, система переривань, таймер, ПВВ. Пристрої введення-виведення приєднані до системної шини через інтерфейси введення-виведення.

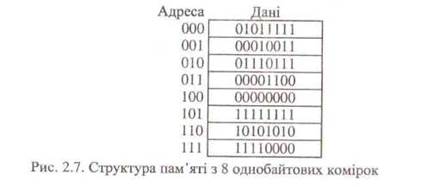

Постійний та оперативний запам'ятовувальні пристрої складають систему пам'яті, призначену для збереження інформації у вигляді двійкових чисел. Постійний запам'ятовувальний пристрій призначений для збереження програм керування таблиць, констант, ОЗП - для збереження проміжних результатів обчислень. Пам'ять організовано у вигляді масиву комірок, кожна з яких має свою адресу і містить байт або слово. Байтом називається група із 8 біт, а слово може мати будь-яку довжину в бітах. Найчастіше під словом розуміють двійкове число довжиною 2 байт.

|

Для звернення до комірки пам'яті треба видати її адресу на шину адреси. Так, комірка з адресою 000 має вміст 010111112 = 5F16.

Сегментом називається область пам'яті, яка складається з суміжних комірок. У МП i8086 сегмент завжди починається з адреси, кратної 16, і займає до 64 кбайт. Існують три основні сегменти: кодів, даних, стека.

Сегмент кодів містить коди команд, які адресуються сегментним регістром кодів CS та регістром - вказівником команд IP. Регістр CS визначає початкову адресу сегмента кодів, а регістр IP - зміщення в сегменті (відстань від початку сегмента до комірки, в якій знаходиться адреса команди).

Сегмент даних містить дані, константи та робочі області, потрібні для виконання програми. Регістр DS має початкову адресу сегмента даних, а зміщення в сегменті задається в команді.

Сегмент стека містить адреси повернення з підпрограм та дані. Регістр SS має початкову адресу сегмента стека, а регістр SP - зміщення в сегменті.

Деякі операції використовують додатковий сегмент даних, початкова адреса якого задається регістром ES, а зміщення в сегменті визначається командою.

Модуль центрального процесора обробляє дані та керує всіма іншими модулями системи. Центральний процесор, крім ВІС МП, містить схеми синхронізації та інтерфейсу із системною шиною. Він вибирає коди команд з пам'яті, дешифрує їх і виконує. Протягом часу виконання команди - командного циклу ЦП виконує такі дії:

- виставляє адресу команди на шину адреси

- отримує код команди з пам'яті та дешифрує його;

- обчислює адреси операнда і зчитує дані;

- виконує операцію, визначену командою;

- сприймає зовнішні керувальні сигнали, (наприклад, запити переривань);

- генерує сигнали стану і керування, потрібні для роботи пам'яті та ПВВ.

Пристрої введення-виведення або зовнішні пристрої - це пристрої, призначені для введення інформації у МП або виведення інформації з нього. Прикладами ПВВ є дисплеї, друкувальні пристрої, клавіатура, цифро-аналоговий та аналого-цифровий пристрої, реле, комутатори. Для з'єднання ПВВ із системною шиною їх сигнали мають відповідати певним стандартам. Це досягається за допомогою інтерфейсів введення-виведення.

Інтерфейси введення-виведення виконують функцію узгодження сигналів ПВВ із сигналами системної шини МП. Їх називають також контролерами або адаптерами. Мікропроцесор звертається до інтерфейсів за допомогою спеціальних команд введення-виведення. При цьому МП виставляє на шину адреси АВ адресу інтерфейсу, а по шині даних DB зчитує дані з пристрою введення або записує у пристрій виведення. На рис. 2.4 показано один інтерфейс введення і один інтерфейс виведення.

Система переривань дозволяє МПС реагувати на зовнішні сигнали -запити переривань, джерелами яких можуть бути: сигнали готовності від зовнішніх пристроїв, сигнали від генераторів, сигнали з виходів датчиків. Із появою запиту переривання ЦП перериває основну програму і переходить до виконання підпрограми обслуговування запиту переривання. Для побудови системи переривань МПК містять ВІС спеціальних програмовних контролерів переривань.

Таймер призначений для реалізації функцій, пов'язаних з відліком часу. Після того, як МП завантажує в таймер число, яке задає частоту, затримку або коефіцієнт ділення, таймер реалізує потрібну функцію самостійно.

Контрольні запитання

1. Назвіть принципи побудови МПС і охарактеризуйте їх.

2. Наведіть типову структуру МПС і поясніть призначення функціональних модулів.

3. Поясніть призначення входу керування третім станом.