К СБИС ПЛ с конфигурируемостью всех областей кристалла (типа «generic») принадлежат СБИС АРЕХ20К, АРЕХ20КЕ фирмы «Altera», Virtex и VirtexE фирмы «Xilinx», Ultra39K фирмы «Cypress Semiconductor», QL фирмы «QuickLogic», ProASIC500K фирмы «Actel», PSD фирмы WSI и др.

СБИС ПЛ АРЕХ20К/КЕ имеют уровень интеграции до более чем 2,5 млн системных вентилей и архитектуру комбинированного типа, называемую Multicore. В них комбинируются табличные методы реализации функций и реализации их в ДНФ, имеются встроенные блоки памяти и гибкая система межсоединений. Сочетая достоинства FPGA и CPLD, семейства с комбинированной архитектурой и высоким уровнем интеграции, в том числе и АРЕХ20К/КЕ, пригодны для решения как задач с интенсивными вычислениями, так и для реализации сложных логических контроллеров и других быстродействующих автоматов. На момент своего появления микросхемы АРЕХ20К/КЕ, которые были объявлены фирмой как первые промышленные СБИС ПЛ с интеграцией уровня SOPC, отличались и наибольшим объемом встроенной памяти (ядра ЗУ), составлявшим от 26 до 264 Кбит для разных представителей семейства при общих ресурсах памяти от 54 до 540 Кбит. Сложность микросхем характеризовалась числом системных вентилей от 162 К до 2,4 М. В первой половине 2000 г. появилось новое семейство фирмы «Altera» -АСЕХ, являющееся более дешевой версией семейства АРЕХ20К/КЕ с числом системных вентилей от 10 до 100 К и рабочей частотой 160 МГц. Ценой микросхем семейства АСЕХ считают 1 долл. за 5К вентилей.

Ядро ЗУ в микросхемах семейства АРЕХ20К/КЕ состоит из блоков ESB (Embedded System Blocks) no 2 Кбита в каждом, число блоков составляет от 26 у младших представителей семейства до 264 у старших. Блоки могут работать независимо с вариантами организации 128 х 16, 256 х8, 512 х4, 1024x2, 2048 х 1 или соединяться с другими для образования более емкой памяти. Вместе со схемами близлежащих логических блоков ESB могут образовывать блоки SRAM, буферы FIFO, двухпортовую память, а в некоторых микросхемах возможна и организация ассоциативной памяти САМ (Content Addressable Memory). Память типа САМ используется в системах коммуникаций, и ее наличие открывает много новых применений для микросхем.

Архитектура микросхем семейств АРЕХ20К/КЕ (рис. 7.27) характеризуется наличием трех типов структур: 1) табличных функциональных преобразователей типа LUT, заимствованных от семейства FLEX10K и FLEX6000; 2) блоков типа SOP (Sum Of Products) для воспроизведения ДНФ логических функций, заимствованных от микросхем семейства МАХ7000; 3) блоков встроенной памяти от микросхем FLEX10KE.

Архитектура Multicore включает в себя новый уровень иерархии, называемый MegaLAB. Каждый MegaLAB составлен из 16 логических блоков LABs, каждый из которых, в свою очередь, содержит по 10 логических элементов LE, и встроенной структуры ESB. На уровне MegaLAB реализованы локальные межсоединения без использования глобальных ресурсов коммутации. Между структурами MegaLAB и контактами ввода/вывода сигналы распространяются по непрерывным связям FastTrack, вносящим малые и предсказуемые задержки.

Блоки ввода/вывода БВВ (lOEs) позволяют работать со многими стандартами сигналов интерфейса: LVTTL; LVCMOS; 1.8-VI/O; 2,5-VI/O; 3,3-VI/O;3,3-VPCI; 3.3AGP; LVDS; GTL+; СТТ; SSTL-3 l,ll; STTL-2 1,11.

В состав современных СБИС ПЛ высокого уровня интеграции, как правило, включаются блоки, управляющие фазовыми соотношениями между синхросигналами в разных точках схемы. Одним из названий подобных блоков является PLL (Phase Locked Loop). В микросхемах семейства АРЕХ20К/КЕ такие блоки усовершенствованы относительно

своих предшественников и выполняют функции ClockLock, ClockBoost и ClockShift. Первая из этих функций снижает задержки контролируемых синхросигналов относительно опорных, вторая состоит в делении или умножении частот синхросигналов, а третья программирует фазовые сдвиги между контролируемыми синхросигналами. Наличие перечисленных возможностей позволяет существенно повысить тактовые частоты реализуемых устройств без нарушения их работоспособности по сравнению с вариантами без блоков PLL.

Каждый внешний вывод микросхем связан с блоком ввода/вывода (БВВ или ЮЕ). Блоки ввода/вывода расположены в концах строк и столбцов шин быстрых связей (FastTracks), которые проходят по всей длине или ширине схемы. Каждый БВВ содержит двунаправленный буфер и триггер (регистр), который может быть входным, выходным или входить в состав двунаправленной линии. БВВ обеспечивает поддержку интерфейса JTAG с возможностями периферийного сканирования для тестирования и конфигурирования микросхемы, имеет управляемую крутизну фронтов, формируемых буферами сигналов, и управление третьими состояниями буферов. Имеется опция Турбо-бита, т. е. его программирование на быстрый или экономичный режим работы схемы.

Микросхемы семейства APEX выпускаются в вариантах с напряжением питания 2,5 В (вариант 20К) и 1,8 В (вариант 20КЕ). При этом напряжения питания для периферийных элементов, обеспечивающих передачу сигналов во внешние цепи, могут составлять 1,8; 2,5 или 3,3 В.

Семейства СБИС ПЛ Virtex и VirtexE фирмы «Xilinx» - FPGA с триггерной памятью конфигурации (SRAM-based), заявленные фирмой как «истинные программируемые системы на кристалле». Семейство Virtex с напряжением питания 2,5 В выпущено в конце 1998 г.,семе-

йство VirtexE с напряжением питания 1,8 В и более высоким уровнем интеграции - несколько позднее. Оба семейства имеют мегавентильный уровень интеграции, блоки встроенной памяти большой емкости и работают на системной частоте до 200 МГц. Основные технологические параметры: минимальный технологический размер 0,22 мкм,пять слоев ме- таллизации.

|

Рис. 7.28. Архитектура микросхем семейств Virtex и VirtexE

Число пользовательских выводов у корпусов микросхем для разных представителей семейства составляет от 180 до 804. Эффективная система межсоединений согласно данным фирмы, обеспечивает достижимый процент использования вентилей до 90 даже в сложных проектах. Линии ввода/вывода программируются на 15 стандартов интерфейсных сигналов. Реализуется интерфейс для шины PCI, работающей на частотах 33 или 66 Мгц.

Общий план кристаллов микросхем Virtex и VirtexE показан на рис. 7.28. Сердцевина на схемы - матрица блоков, основу которых с блоки КЛБ (CLB, Configurable Logic Blocks) и переключательные блоки ПБ (GRM, Globsl Routing Matrix). В совокупности КЛБ и ПБ соcтавляют так называемый VersaBlock. Переключательный блок содержит набор программируемых ключей на пересечениях горизонтальных и вертикальных линий каналов трассировки, таким образом, VersaBlock имеет как средства логической обработки данных, так и средства локальной трассировки, обеспечивающие коммутацию КЛБ (рис.7.29). Как видно из рисунка, VersaBlock обеспечивает связи трех типов:

1) межсоединения в составе КЛБ и между КЛБ и ПБ;

2) внутренние обратные связи для КЛБ, позволяющие подавать выходные сигналы КЛБ к табличным функциональным преобразователям этого же КЛБ с малыми задержками;

3) прямые связи, соединяющие горизонтально-смежные КЛБ без использования ПБ, что ускоряет передачу сигналов.

|

Иерархическая система межсоединений семейств Virtex и VirtexE сохранила многие черты, традиционные для фирмы «Xilinx», но имеет и своеобразные особенности, в частности, систему коммутации, названную VersaRing, дающую дополнительные возможности межсоединений в периферийной области кристалла. Благодаря этой системе облегчается взаимозаменяемость выводов микросхемы и их размещения по тем или иным цепям конфигурируемой схемы. Такие возможности могут обеспечивать сохранение прежних печатных плат при модификациях внутренней структуры СБИС.

На периферии кристалла располагаются блоки ввода/вывода (lOBs), а в углах - схемы DDL (Digital Delay Loops), назначение и функционирование которых аналогичны рассмотренным для блоков PLL семейства АРЕХ20К/КЕ несмотря на иное название блоков.

Блоки ввода/вывода имеют и тракт ввода, и тракт вывода сигнала, так что подключенные к ним контактные площадки могут быть использованы как входы или выходы в зависимости от программирования блока (рис. 7.30). Через тракт ввода входные сигналы передаются во внутренние цепи микросхемы либо непосредственно, либо с запоминанием триггером, тип которого можно выбрать из числа возможных вариантов (управляемый фронтом, защелка). В цепь информационного входа триггера включен программируемый элемент задержки, который при необходимости позволяет исключить нарушение условий предустановки или выдержки сигналов, соблюдение которых обеспечивает работоспособность схемы.

Тракт вывода содержит буфер с третьим состоянием, выводящий сигналы на контактную площадку КП. Выходные сигналы могут быть поданы на вход буфера непосредственно от комбинационных цепей выработки логических функций или через триггер, тип которого также может быть выбран из числа имеющихся вариантов. Управление третьим состоянием может осуществляться как от комбинационных логических схем, так и через триггер, который обеспечивает синхронизацию сигналов разрешения или запрещения буфера.

Блоки ввода/вывода могут обеспечивать интерфейс шины PCI с частотой до 66 Мгц.

Блоки ввода/вывода семейств Virtex и VirtexE способны воспринимать и вырабатывать сигналы, отвечающие широкому спектру стандартов на интерфейс: LVTL; LVCMOS2; PCI3.3V; PCI5.0V; GTL; GTL+; HSTL 1,11,111; SSTL31,11; SSTL21,11; СТТ; AGP. Для конфигурации буферов, соответствующей тому или иному стандарту, в некоторых случаях требуются определенные значения двух внешних напряжений: VCCO и VREF. Входной буфер воспринимает пороговое напряжение VREF. Уровень сигнала логической единицы для большинства стандартов интерфейса зависит от напряжения VCCO. Оба напряжения задаются на контактах микросхемы и обслуживают группу блоков ввода/вывода, называемую банком. Для всех БВВ данного банка напряжения идентичны, поэтому существуют ограничения на стандарты интерфейса у близко расположенных контактов. Внутри банка могут быть и разные стандарты интерфейса, если они требуют одних и тех же напряжений VCCO и VREF. В качестве входных для напряжений VREF могут быть запрограммированы определенные пользователем внешние выводы. В микросхемах Virtex и VirtexE организовано по восемь банков (по два на каждую сторону кристалла).

Основой конфигурируемого логического блока КЛБ семейств Virtex и VirtexE (рис. 7.31) являются четыре логические ячейки ЛЯ (LCs, Logic Cells). В каждой логической ячейке имеется четырех входовый функциональный преобразователь табличного типа LUT, логические схемы переноса и управления и триггер (регистр) типа D. КЛБ делится на две идентичные секции (Slice 1 и Slice 2), схема одной из секций раскрыта на рисунке. Величины G1-G4 и F1-F4 - это аргументы функций Y и X, вырабатываемых преобразователями LUT. Выходные сигналы от преобразователей могут передаваться прямо на выход КЛБ или на вход триггера типа D. Имеющиеся в логических ячейках специальные логические схемы позволяют комбинировать выходы нескольких функциональных преобразователей для получения любых функций пяти и шести аргументов и некоторых функций большего числа аргументов, а также мультиплексоров размерностью до 8 - 1.

Ресурсы памяти функциональных преобразователей секции можно использовать как синхронную статическую память SRAM с организацией 16´2 или 32 ´ 1 или как двухпортовую синхронную SRAM с организацией 16x1 или для образования 16-разрядного регистра сдвига.

Ресурсы памяти функциональных преобразователей секции можно использовать как синхронную статическую память SRAM с организацией 16´2 или 32 ´ 1 или как двухпортовую синхронную SRAM с организацией 16x1 или для образования 16-разрядного регистра сдвига.

Специальные логические схемы выработки сигналов переноса упрощают и ускоряют воспроизведение арифметических функций. Ресурсы одной ЛЯ позволяют реализовать в ней схему разряда полного сумматора. Предусмотрены и специальные логические элементы для построения из ЛЯ множительных устройств.

Триггер типа D программируется в вариантах управления фронтом или защелки. Информационный вход триггера подключается к выходам функциональных преобразователей или же прямо ко входам секций (входы BY, BX). Помимо сигналов Clock и Clock Enable каждая секция имеет синхронные сигналы сброса и установки триггеров.

В каждом КЛБ имеются два буфера с третьим состоянием, способные работать на внешние шины.

При работе микросхем большинство сигналов передается через основную систему межсоединений (General Purpose Routing). Линии связей этой системы расположены в горизонтальном и вертикальном каналах трассировки между строками и столбцами КЛБ. Ресурсы этой системы следующие.

• Переключательный блок у каждого КЛБ, обеспечивающий ему доступ к трассам основной системы межсоединений.

• По 24 линии передач сигналов от ПБ к соседним ПБ в каждом из четырех направлений.

• 96 буферированных линий передач сигналов между ПБ от одного к другому через шесть блоков в каждом из четырех направлений. Сигналы поступают на эти линии только в их концах и доступны в концах линий или в их серединах (на расстоянии трех блоков от источника). Треть этих линий двунаправленные, остальные однонаправленные.

• 12 длинных линий, буферированных, двунаправленных, передающих сигналы по всей схеме (по всей высоте или ширине кристалла) с малыми задержками.

Кроме системы основных соединений микросхемы имеют ресурсы VersaRing, о которых уже говорилось, а также глобальные и специальные ресурсы. Глобальные ресурсы используются для распределения синхросигналов и других сигналов, поступающих на большое число приемников, а специальные - для распространения сигналов переноса и т. п.

Микросхемы семейств Virtex и VirtexE воспринимают все команды, специфицированные в стандарте IEEE 1149.1 интерфейса JTAG.

7.7.3. СБИС ПЛ КЛАССА «СИСТЕМА НА КРИСТАЛЛЕ» С БЛОЧНОЙ АРХИТЕКТУРОЙ

В СБИС ПЛ класса «система на кристалле» с блочной архитектурой выделяются специализированные области (аппаратные ядра), проектируемые методами заказных схем. Достоинства и недостатки применения блочных архитектур обсуждались ранее, в п. 7.7.1. По субъективному мнению авторов, использование микросхем с блочной архитектурой является весьма перспективным направлением.

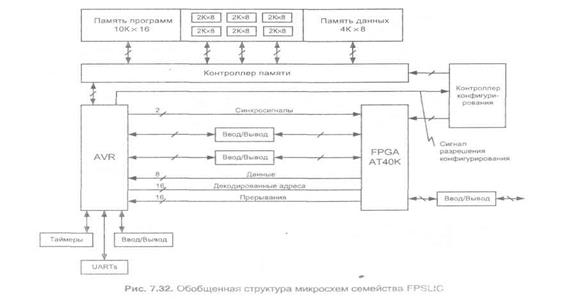

Первые объявленные СБИС, в которых процессор, память и FPGA размещены на одном кристалле - семейство FPSLIC (Field Programmable System Level Integration Chips) фирмы «Atmel», одной из крупных фирм-разработчиков цифровых микросхем, в том числе микросхем программируемой логики. До появления семейства FPSLIC, выход которого на рынок датируется серединой 2000 г., фирмой «Atmel» были разработаны хорошо известные процессоры AVR и FPGA семейства АТ40К. В микросхемах семейства FPSLI как раз и совмещены процессорное ядро AVR, FPGA типа АТ40К и блоки статической памяти SRAM. Такая «комплектация» соответствует возможностям построения системы на кристалле. При закреплении функций процессора и памяти за соответствующими ядрами на программируемую логику возлагаются все остальные функции, необходимые для построения системы (например, функции управления памятью и/или внешними устройствами, создание проблемно-ориентированных сопроцессоров, реализация интерфейсных функций тех или иных шин и т. д.). В СБИС FPSLIC FPGA рассматривается как «большое внешнее устройство» с разнообразными заказными или общеупотребительными функциями, к которому процессор обращается для выдачи ему команд и исходных данных и получения результатов.

На рис. 7.32 представлена обобщенная структура микросхем семейства FPSLIC. Микросхемы имеют напряжение питания 3,3 В, изготовляются технологическими процессами с топологической нормой 0,35 мкм, имеют несколько режимов пониженного энергопотребления

AVR - 8-разрядное процессорное ядро производительностью более 30 MIPS (при тактовой частоте 40 Мгц) с RISC-архитектурой, имеющее систему команд, содержащую около 120 инструкций. Особенностями микроконтроллера с ядром AVR в первую очередь являются выполнение команд, извлекаемых непосредственно из статической памяти SRAM, что значительно ускоряет работу микроконтроллера, и наличие в АЛУ умножителя MPL для.аппаратной реализации операции умножения, широко используемой в процессах

цифровой обработки сигналов (ЦОС). Архитектура AVR оптимизирована для разработки приложений на языке С, ядро имеет регистровый файл из 32 регистров.

С ядром AVR связан ряд устройств, характерных для микроконтроллеров: два универсальных асинхронных программируемых связных адаптера (UARTs), два 8-разрядных и один 16-разрядный таймер-счетчик, два программируемых порта ввода/вывода. Дополнительно введен специальный аппаратный интерфейс I2 С для обеспечения связи с внешней энергонезависимой памятью типа EEPROM, используемой для конфигурирования микросхем FPSLIC.

Блок статической памяти общей емкостью 36 Кбайт - двухпортовая память с временем доступа 15 не содержит фиксированные области памяти программ (с организацией 10К ´ 16) и памяти данных (с организацией 4К ´ 8) и, кроме того, область, которую при конфигурации схемы можно по желанию разработчика полностью или частями добавить к памяти программ или к памяти данных. Предписание по использованию не фиксированной области памяти содержится в специальном регистре конфигурации в контроллере памяти микросхемы (Memory Controller).

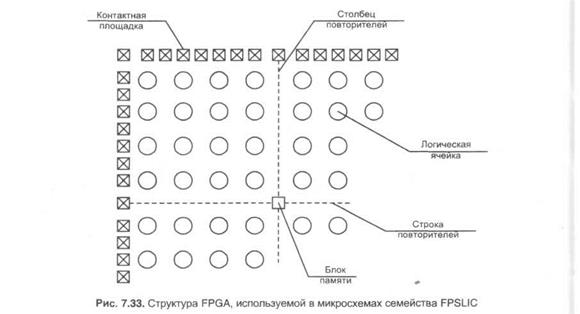

В блоке FPGA используются стандартные структуры микросхем АТ40К, работающие на системной частоте 100 Мгц, сложностью от 10 до 40К используемых эквивалентных вентилей с емкостью встроенной памяти от 2048 до 18 432 бит. В основных чертах эти структуры типичны для FPGA, хотя и имеют некоторые оригинальные особенности (рис. 7.33). Основа блока - симметричная матрица идентичных логических ячеек, в каждую из которых входят несколько программируемых мультиплексоров, триггер типа D, буфер с тремя состояниями и два табличных функциональных преобразователя (LUT). Функциональные преобразователи воспроизводят функции трех переменных (одних и тех же для обоих преобразователей) и могут быть объединены для выработки любых функций четырех переменных. Для логических ячеек предусмотрены несколько стандартных режимов (конфигураций), а именно следующие:

• реализации функций одноразрядного сумматора (арифметический режим);

• выполнения операции умножения (режим DSP/Multiplier);

• реализации разряда счетчика;

• выполнения функций мультиплексоров с буферами на три состояния (режим Tristate/MUX).

Перечисленные режимы, как видно, ориентированы на проекты с интенсивными вычислениями, такие как реализация цифровых фильтров, быстрых преобразований Фурье, конвольверов, криптографических алгоритмов и многих других мультимедийных задач. На основе блока FPGA реализуются и общеупотребительные интерфейсные функции (UARTs, PCI и др.).

Топологически логическая ячейка трактуется как восьмиугольник и с восемью ближайшими соседями она имеет прямые связи (Direct Connects), проходящие по матрице ячеек в ортогональных и диагональных направлениях. Благодаря прямым связям, в частности, строятся ультрабыстродействующие матричные множительные устройства.

Массив FPGA имеет шесть внешних и две внутренних линии тактирования. Для внутренних линий тактирования источником сигналов служит ядро AVR, причем одна из этих линий принадлежит системной линии тактирования микроконтроллера, а вторая может быть запрограммирована на соединение с одним из нескольких источников тактовых сигналов, генерируемых внутри AVR (таймеров и др.).

Ядро АТ40К имеет свою статическую память, называемую FreeRam. Время доступа к данным этой памяти составляет 10 не. Благодаря наличию FreeRAM функции памяти в создаваемых на основе FPGA устройствах реализуются без затрат логических ресурсов FPGA. Возможны различные варианты организации памяти FreeRAM: синхронный или асинхронный, одно- или двухпортовый для RAM, FIFO и др. Варианты организации создаются инструментальными средствами макрогенерации функций.

Система межсоединений элементов FPGA иерархична и включает в себя локальные шины и экспресс-шины. С восемью ближайшими соседями, как уже отмечалось, логические ячейки имеют прямые связи. Сегменты локальных шин покрывают расстояния в четыре ячейки, экспресс-шин - в восемь. Шины соединяются через повторители (Repeaters), подключаемые к двум соседним сегментам. Повторители регенерируют сигналы и выполняют также некоторые функции их коммутации. В системе межсоединений используются программируемые пасс-вентили (Pass gates), с помощью которых формируются шины с тремя состояниями.

Интерфейс FPGA с ядром AVR предусматривает для FPGA 16 входных линий декодированного адреса от AVR, 16 выходных линий запросов прерываний с различными приоритетами для AVR. Таким образом, каждому устройству, реализованному в FPGA и имеющему адрес в адресном пространстве ввода/вывода AVR, придается возможность иметь собственный запрос прерывания.

Кроме того, AVR определяет направление передачи данных, посылая для FPGA сигналы стробов чтения и записи. Эти сигналы управляют двунаправленной шиной данных, образуемой из линий Express Lines системы межсоединений FPGA. Таким образом, ядро микроконтроллера взаимодействует с устройствами, созданными в FPGA, принципиально подобно тому, как обычно процессор взаимодействует с внешними устройствами.

Для функций заказной периферии, реализуемой в FPGA, существует макробиблиотека, что существенно упрощает проектирование. Автоматическая генерация макросов, которую способна выполнять FPGA AT40K, минимизирует также риски проектирования, так как дает возможность пользоваться уже хорошо проверенными схемными решениями.

Другой аспект взаимодействия AVR и FPGA состоит в том, что они имеют общий доступ к двухпортовой памяти SRAM с временем доступа 15 не (рис. 7.34). Между FPGA и AVR размещены 36 Кбайт этой памяти, которая в первую очередь используется микроконтроллером, подсоединенным к одному из портов, для хранения команд и данных. Порт, подсоединенный к FPGA, используется во время загрузки конфигурации, чтобы загрузить память программ и память данных микроконтроллера. FPGA может обращаться к SRAM одновременное AVR. Разделяемая память позволяет реализовать различные варианты буферного обмена между FPGA и AVR (буферы FIFO, LIFO или др.).

У порта SRAM, подключенного к FPGA, нет сигнала разрешения чтения, т. е. чтение данных для FPGA всегда разрешено. Для предотвращения конфликтов при обращениях FPGA и AVR в одно и то же время к одному и тому же адресу требуется позаботиться о логике арбитража (чаще всего специальный управляющий регистр микроконтроллера при необходимости ограничивает доступ к памяти со стороны FPGA).

Важная особенность микросхем семейства FPLIC - способность реализовать концепцию кэш-логики (Cache Logic), впервые введенную фирмой «Atmel». Понятие кэш-логики отражает достижения в области развития адаптивных систем. Кэш-логика позволяет производить полное или частичное реконфигурирование системы «на лету», без потери имевшихся данных и нарушения работы неизменяемой части устройств. Сохраняются данные, которые были получены к моменту перестройки той или иной части системы. Та часть аппаратуры, в которой в данный момент происходит обработка информации, представлена схемой соответствующей конфигурации в FPGA, а пассивная часть системы представлена данными, сохраняемыми в недорогих устройствах памяти. В результате экономно выполняются логические преобразования. Когда активизируются новые операции, новая конфигурация записывается «поверх старой».

Та или иная решаемая задача может быть разложена на множество операций низшего иерархического уровня, таких как сдвиг, счет, сложение, умножение, мультиплексирование и т. д. Ясно, что каждая из подобных функций может быть использована многократно в разных ситуациях, причем в каждый момент времени активна только малая часть функций. Исключая избыточность и контролируя условия появления каждой операции, можно так организовать систему, что сложные функции будут воспроизводиться с помощью небольшого числа несложных и, следовательно, дешевых схем программируемой логики. В одном из примеров требуемая задача решалась обычным способом с помощью 10 000 вентилей, а применение кэш-логики позволило применить микросхему программируемой логики сложностью всего 2000 эквивалентных вентилей, причем остальные 8000 вентилей удалось исключить, используя «кэширование», т. е. запоминание неизменной в данное время информации в более дешевой системной памяти.

Концептуально выделяют предопределенную (predermined) и динамическую кэш-логику. Первая подразумевает использование предопределенных функций и макросов, хранимых во внешней энергонезависимой памяти (EPROM, EEPROM, диск, CD-ROM). Эти функции уже проработаны, размещены и трассированы и имеют ранее сгенерированные битовые потоки (Bit streams) конфигурирования. Выполнением их управляют средства самой кэш-логики или внешние средства (программы процессора). При загрузке новых функций данные в регистрах не теряются даже в модифицируемой части системы.

Второй тип кэш-логики подразумевает определение требуемых функций, размещение и трассировку схем их реализации и генерацию битовых потоков настройки программируемой логики в реальном масштабе времени. Такая кэш-логика ассоциируется с разработкой адаптивных систем и в настоящее время существует лишь как концепция, еще не имеющая законченной физической реализации.

Применение кэш-логики снижает сложность программируемой части аппаратуры и, в конечном счете, удешевляет аппаратуру и улучшает такие ее характеристики, как надежность (вследствие уменьшения числа физически существующих схемных компонентов), потребляемую мощность и др. Область перспективного применения кэш-логики достаточно широка: это портативная аппаратура с ее высокими требованиями к снижению потребляемой мощности и габаритных размеров, системы с интенсивными вычислениями (компьютерная графика, распознавание образов и речи и многое другое).

Микросхемы семейства FPSLIC имеют механизм конфигурирования FPGA под управлением AVR, который может загружать кэшевую память FPGA, имея прямой доступ к шине данных SRAM-конфигурации. При обычной загрузке конфигурации кэшевый доступ в память конфигурации блокируется. При кэшевом доступе AVR использует три регистра для формирования адреса и один регистр для данных. Типовое назначение этого режима для AVR - принять последовательные данные через UART и направить их в качестве данных конфигурации в FPGA, вызывая таким образом загрузку или разрешая системную реконфигурацию, при которой структура FPGA алгоритмически видоизменяется.

Разработчики таких сложных СБИС, как FPSLIC, подчеркивают, что подобные микросхемы с их впечатляющими возможностями не следует рассматривать как просто микроконтроллеры с программируемой проектировщиком периферией, поскольку для этой относительно ограниченной цели могут найтись более простые решения (например, с применением микросхем программируемой пользователем периферии фирмы WSI). С точки зрения технико-экономических показателей, эффект достигается в первую очередь при достаточно полном использовании новых функциональных возможностей, присущих такой качественно новой продукции как микросхемы семейства FPSLIC и им подобные [уже объявлено о выпуске блочных СБИС типа «система на кристалле» фирмой «Triscend» (Triscend E5, Configurable System-on-Chip) ожидаются подобные разработки и от фирмы «Altera» и других].

7.8. КОНФИГУРИРОВАНИЕ БИС/СБИС ПРОГРАММИРУЕМОЙ ЛОГИКИ

Способ конфигурирования БИС/СБИС ПЛ, т. е. настройки их на определенный алгоритм функционирования, зависит от типа программируемых элементов. Для микросхем с энергонезависимой памятью конфигурации (EPROM, EEPROM, Flash) запись в память является специальным сточки зрения электрических процессов режимом. Конфигурирование таких СБИС может производиться вне создаваемой системы с помощью программаторов или же в составе системы (т. е. при сохранении монтажа микросхемы на плате), но также с использованием специальных устройств, выпускаемых фирмами-производителями, и, как правило, посредством расширенного интерфейса JTAG. При этом для процессов записи информации требуются повышенные напряжения программирования Unp (для микросхем семейств МАХ7000 и МАХ9000 фирмы «Altera», например, это 12 В при рабочем напряжении питания 5 В). Для старых микросхем требовались несколько источников питания, более новые стали снабжаться внутренними преобразователями рабочего напряжения в повышенное напряжение программирования.

Для БИС/СБИС ПЛ со статической памятью конфигурации ее загрузка не требует каких-либо специальных электрических режимов и провес конфигурирования состоит в передаче в микросхему информации, необходимой для получения требуемых соединений в логических блоках, блоках ввода/вывода и подключения их к трассам межсоединений (локальным и глобальным матрицам межсоединений, системам основных и прямых связей, длинным линиям и т. д.). Операция конфигурирования выполняется после каждого выключения питания, причем обычно сам факт очередного включения питания автоматически инициирует процесс конфигурирования, который может повторяться неограниченное число раз. Отсутствие специальных электрических режимов для записи информации в память конфигурации обеспечивает возможность ее проведения в работающей схеме, причем возможна и частичная реконфигурация, относящаяся лишь к части системы.

Конфигурирование БИС/СБИС ПЛ со статической (триггерной) памятью конфигурации, о которой подробнее говорится ниже, представляет собою запись во внутренние регистры (триггеры) данных, задающих структуру блоков системы и их межсоединений. Каждый бит настроечных данных задает состояние соответствующему триггеру, управляющему программируемым ключом в схеме логического блока, программируемого мультиплексора, программируемого межсоединения и т. п.

БИС/СБИС ПЛ обычно имеет несколько возможных режимов конфигурирования (например, у FPGA ´C4000 фирмы «Хilinx» их шесть, у СБИС семейства Virtex той же фирмы четыре, у микросхем семейства Spartan -два). У способов конфигурирования микросхем разных фирм и разных типов много общего. Для конкретности рассмотрим способы конфигурирования СБИС ПЛ типа SOC семейства Virtex.

Для конфигурирования этой микросхемы используются как специализированные выводы, так и выводы, которые после завершения конфигурирования могут играть роль выводов общего назначения. К специализированным относятся выводы М2, М1, МО, на которых задается код того или иного режима, вывод для синхросигналов процесса конфигурирования, выводы PROGRAM, DONE и выводы периферийного сканирования TDI, TDO, TMS, ТСК. Вывод синхросигнала может быть выходом, когда этот сигнал генерируется микросхемой, или входом, когда поступает извне.

Возможные способы конфигурирования:

• пассивный последовательный (Slave-serial mode);

• активный последовательный (Master-serial mode);

• байт-последовательный (SelectMAP mode);

• периферийного сканирования.

В пассивном последовательном режиме микросхема получает данные конфигурирования в виде потока битов из последовательной памяти PROM или другого источника. Синхронизация осуществляется от внешнего источника, каждый положительный фронт синхросигнала вводит бит данных от входа DIN. Несколько микросхем могут быть соединены в цепочку для конфигурирования в едином процессе от общего потока битов. В этом случае после завершения конфигурирования очередной микросхемы данные конфигурации для следующих микросхем появляются на выводе DOUT микросхемы, завершившей конфигурирование.

В активном последовательном режиме выходной синхросигнал микросхемы подается на последовательное ЗУ, с которого на вход DIN микросхемы поступает последовательный поток битов конфигурации. Микросхема воспринимает каждый бит под управлением положительного фронта синхросигнала. После загрузки очередной микросхемы цепочки данные для следующей снимаются с выхода DOUT той микросхемы, которая закончила конфигурирование. Для синхронизации процесса можно выбирать частоту из широкого диапазона значений. По умолчанию используется наименьшая частота 2,5 МГц. Максимальная частота - 60 МГц. Устанавливаемые частоты, естественно, должны соответствовать возможностям используемых PROM и включенных в цепочку микросхем. При включении питания устанавливается частота 2,5 МГц. Если не поступит команда на изменение этого значения (опция ConfigRate в программе генерации битового потока конфигурации), процесс продолжится до конца на частоте 2,5 Мгц.

В байт-последовательном режиме время конфигурирования минимально. Используется байт-последовательный поток данных, которые записываются в микросхему с учетом флажка ее готовности BUSY. Байтовый поток задается от внешнего источника, как и сигналы тактирования, разрешения работы CS и WRITE. В этом режиме данные могут и читаться. Если сигнал WRITE пассивен, то данные конфигурации читаются из микросхемы (этот процесс есть часть процесса Readback). В режиме SelectMAP также можно конфигурировать одновременно несколько микросхем, но в этом случае они включаются параллельно по входам синхронизации, данных, WRITE и BUSY. Загружаются микросхемы поочередно, путем соответствующего управления сигналами разрешения их работы CS.

В режиме периферийного сканирования конфигурирование осуществляется исключительно через выводы порта тестирования ТАР (Test Access Port) интерфейса JTAG. Используется специальная команда CFG_IN, позволяющая входным данным от вывода TDI преобразовываться в пакеты данных для внутренней шины конфигурации микросхемы.

Процесс конфигурирования для микросхем Virtex содержит три этапа: очистка памяти конфигурации, загрузка в нее данных и активизация логических схем, участвующих в процессе.

Конфигурирование начинается автоматически после включения питания, но может быть и задержано пользователем с помощью сигнала PROGRAM, снятие которого запрещает конфигурирование. Завершение очистки памяти выявляется с помощью сигнала INIT, а завершение всего процесса - с помощью сигнала DONE.

Данные для загрузки памяти конфигурации формируются системой автоматизированного проектирования.

Реконфигурация в системе - одно из важнейших достоинств СБИС ПЛ, позволяющее легко изменять логику их работы. Потребности в изменениях возникают как для устранения не выявленных при первоначальном тестировании ошибок, так и для модернизации (Upgade) систем. Возможности программирования в системе растут, если при проектировании часть функциональных возможностей СБИС ПЛ оставлять свободной, имея запас по скорости, функциональным возможностям и ресурсам межсоединенй. При реконфигурации в системе должно сохраняться назначение внешних выводов, иначе потребуется изменить монтаж печатных плат.

Среди СБИС ПЛ имеются и такие, в которых реализованы одновременно триггерная и энергонезависимая память конфигурации. В этом случае конфигурирование СБИС ПЛ можно производить без внешних источников данных путем автоматической загрузки триггерной памяти из энергонезависимой.