ПРОГРАММИРУЕМАЯ ЛОГИКА И ЕЕ ПРИМЕНЕНИЕ В МИКРОПРОЦЕССОРНЫХ СИСТЕМАХ

ОБЩИЕ СВЕДЕНИЯ, КЛАССИФИКАЦИЯ

7.1.1. УРОВЕНЬ ИНТЕГРАЦИИ ИНТЕГРАЛЬНЫХ СХЕМ (ИС) И ЕГО ВЛИЯНИЕ НА КАЧЕСТВО ЦИФРОВОЙ АППАРАТУРЫ И ЕЕ ПРОЕКТИРОВАНИЕ.

БИС/СБИС ПРОГРАММИРУЕМОЙ ЛОГИКИ - СРЕДСТВО ИСКЛЮЧЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ МАЛОГО И СРЕДНЕГО УРОВНЕЙ ИНТЕГРАЦИИ ИЗ СОСТАВА МИКРОПРОЦЕССОРНЫХ СИСТЕМ

Интегральные схемы (ИС), составляющие основу элементной базы средств обработки информации, характеризуются широким диапазоном сложности (уровня интеграции). Уровень интеграции оценивается условным числом эквивалентных вентилей (чаще всего вентилей типа 2И-НЕ), которые могли бы быть размещены на данном кристалле. Выпускаемые промышленностью цифровые схемы имеют уровень интеграции от нескольких единиц для малых интегральных схем (МИС) до нескольких миллионов для сверхбольших интегральных схем (СБИС).

Генеральная тенденция развития цифровых интегральных схем - постоянный рост уровня интеграции. Непрерывное за все время существования ИС совершенствование технологии их производства позволяет постоянно снижать минимальные размеры схемных элементов и потребляемую ими мощность и увеличивать площадь кристалла, благодаря чему растет достижимый уровень интеграции. Эти же факторы существенно улучшают технико-экономические параметры не только самих ИС (быстродействие, надежность, стоимость, отнесенную к единице логической мощности, и др.), но и параметры реализованной на ИС аппаратуры.

К основным модулям микропроцессорной системы относятся процессоры, память, внешние устройства и интерфейсные схемы. Микросхемы процессоров и памяти сточки зрения производителей ИС являются стандартной продукцией. Промышленность выпускает широкий спектр обоих типов микросхем, отличающихся большим разнообразием параметров. Из имеющегося множества типономиналов процессоров и запоминающих устройств проектировщик (системотехник) выбирает наиболее подходящий для своего проекта вариант. Важно, что изготовитель микросхем процессоров и памяти не выполняет индивидуальные заказы потребителей, а работает на широкий рынок. Это обеспечивает стандартным микросхемам большие объемы производства - необходимое условие реализуемости ИС высокого уровня интеграции. Действительно, стоимость проектирования Спр сложных ИС чрезвычайно велика, но входит в стоимость микросхемы в виде составляющей Спр/N, где N— тиражность производства данной ИС. Только при достаточно больших значениях N будут оправдываться большие затраты средств на проектирование БИС/СБИС.

Кроме стандартных частей микропроцессорная система содержит и некоторые индивидуальные схемотехнические части для сопряжения модулей и управления ими. Такие индивидуальные части системы ранее приходилось строить с помощью ИС малого и среднего уровней интеграции, применение которых ведет к резкому увеличению числа корпусов и внешнего монтажа в схемах МПС, а это сопровождается столь же резким снижением их быстродействия и надежности, росту габаритных размеров и потребляемой мощности.

Таким образом, для создания высококачественной сложной цифровой аппаратуры следует использовать ИС высокого уровня интеграции.

Появление в нестандартных блоках системы малых и средних ИС всегда объяснялось только экономическими причинами - чрезмерно высокой стоимостью заказных БИС/СБИС при малых объемах их выпуска. С точки зрения технологии, естественно, реализация специализированных БИС/СБИС была вполне осуществима. Препятствия к применению БИС/СБИС в специализированных частях микропроцессорных систем стали постепенно устраняться по мере развития программируемых ИС.

Как будет показано далее, применение БИС/СБИС с программируемой логикой улучшает и ряд других важных параметров проектов - время подготовки продукции к выходу на рынок (Time to Market), безошибочность проектирования и др.

7.1.2. КЛАССИФИКАЦИЯ ИС ПРОГРАММИРУЕМОЙ ЛОГИКИ

Микросхемы программируемой логики классифицируются по нескольким признакам (рис. 7.1). По уровню интеграции их можно разделить на простые, сложные и схемы типа «системы на кристалле» (SOC, System On Chip), как показано на рис. 7.1. Можно сказать также, что простые ИС программируемой логики относятся к первому их поколению, тогда как сложные и SOC принадлежат к следующим.

Простые ИС с программируемой логикой (ИС ПЛ), обозначаемые в совокупности как PLD (Programmable Logic Devices), делятся на микросхемы программируемой матричной логики ПМЛ (PAL, Programmable Array Logic) и микросхемы программируемых логических матриц ПЛМ (PLA, Programmable Logic Array). Усложненные варианты PAL некоторые производители называют схемами GAL (Generic Array Logic). Простые ИС ПЛ рассчитаны на реализацию систем переключательных функций и использовались для замены нескольких корпусов или даже десятков корпусов стандартных ИС на один корпус PLD. По мере их усложнения решаемые ими задачи также усложнялись, в частности, появилась ориентация на реализацию конечных автоматов (в схемы PLD стали вводить элементы памяти).

Продолжением линии развития ПМЛ стали сложные БИС/СБИС типа CPLD (Complex PLD), в которых, как и в PLD, используются схемы непосредственной реализации дизъюнктивных нормальных форм переключательных функций (функций типа SOP, Sum Of Products), но в одной CPLD имеется несколько ПМЛ (PAL, GAL), объединенных системой коммутации.

Сложные ИС ПЛ типа FPGA (Field Programmable Gate Arrays) содержат матрицу логических блоков того или иного типа, расположенных по строкам и столбцам, между которыми размещены средства коммутации, позволяющие с помощью программирования получать необходимые взаимные соединения логических блоков. Сами блоки могут быть выполнены различным образом. Стремление объединить достоинства, присущие CPLD и FPGA, привело к созданию БИС/СБИС комбинированной архитектуры, для которых еще не выработано общепринятое название.

Рост уровня интеграции дал возможность размещать на кристалле схемы, сложность которых соответствует целым системам (мегавентильные схемы). Такие схемы именуются SOC и могут быть разделены на два типа - однородные схемы, в которых функциональное назначение отдельных областей кристалла обеспечивается программированием одних и тех же по типу ресурсов (схемы типа generic), и блочные структуры, в которых отдельные области кристалла специализированы уже при их изготовлении. Про такие кристаллы говорят, что они содержат специализированные аппаратные ядра (Hardcores).

Важным классификационным признаком ИС ПЛ является тип памяти конфигурации, т. е. тип программируемых элементов, задаваемое состояние которых как раз и создает требуемое устройство как конкретный вариант межсоединений имеющихся на кристалле схемотехнических ресурсов. Программируемые элементы представляют собой двухполюсники, играющие роль ключей, которым при программировании задаются состояния «замкнуто» или «разомкнуто». Число программируемых элементов в ИС ПЛ зависит от их сложности и в схемах наибольшего уровня интеграции измеряется миллионами.

В ИС ПЛ используются или использовались ранее следующие типы программируемых элементов:

• плавкие перемычки Fuse (в схемах самых первых образцов);

• пробиваемые диэлектрические перемычки Antifuse (краткий русский термин отсутствует);

• однократно заряжаемые «плавающие затворы» МОП-транзисторов (EPROM-OTP);

• перезаряжаемые «плавающие затворы» с введением заряда электрическими воздействиями на транзистор и его стиранием с помощью облучения кристалла ультрафиолетовыми лучами (EPROM);

• перезаряжаемые «плавающие затворы» с электрическими записью и стиранием зарядов (EEPROM, Flash);

• ключевые МОП-транзисторы, управляемые триггерами памяти конфигурации (SRAM-based).

Репрограммируемые элементы EPROM, EEPROM, Flash, SRAM-based различаются по свойствам. Элементы EPROM с ультрафиолетовым стиранием допускают ограниченное число перезаписей заряда, так как процесс облучения постепенно изменяет свойства кристалла.

Элементы с электрическим стиранием имеют существенно большее число допустимых перезаписей заряда (приблизительно в тысячу раз), а элементы с триггерной памятью конфигурации могут репрограммироваться неограниченно.

Одним из признаков классификации служит наличие или отсутствие связи между задержками распространения сигналов и конкретными путями их передачи по межсоединениям кристалла. Этот фактор важен, так как независимость задержки от конкретного пути передачи сигнала означает предсказуемость задержек, что существенно облегчает построение на кристалле работоспособных схем, особенно схем высокого быстродействия.

7.1.3.КОНСТРУКТИВНО-ТЕХНОЛОГИЧЕСКИЕ ТИПЫ СОВРЕМЕННЫХ ПРОГРАММИРУЕМЫХ ЭЛЕМЕНТОВ

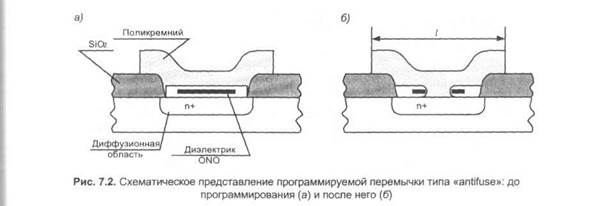

Программируемые перемычки типа «antifuse» (рис. 7.2, а, б) в исходном состоянии (до программирования) имеют чрезвычайно большие сопротивления (токи утечки порядка фемтоампер). Программирующий импульс напряжения пробивает трехслойный диэлектрик с чередованием слоев «оксид - нитрид - оксид» и создает проводящий поликремниевый канал между поликремниевым электродом и диффузионной областью n+, причем в зависимости от тока через перемычку в режиме ее программирования можно

получить проводящий участок с сопротивлениями от 100 Ом и выше при очень малой паразитной емкости.

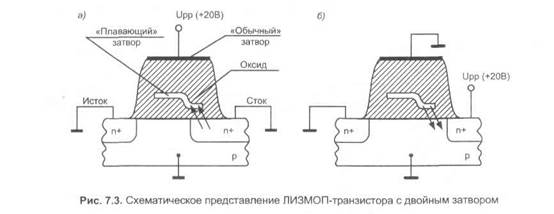

Элементы EEPROM и Flash реализуются на ЛИЗМОП-транзисторах (название транзистора отражает процесс лавинной инжекции заряда в плавающий затвор). На рис. 7.3 показан ЛИЗМОП-транзистор с двумя затворами - плавающим и обычным.

Плавающий затвор не имеет внешнего вывода и как бы погружен в диэлектрик (оксид, т. е. двуокись кремния). В этом затворе может создаваться или ликвидироваться заряд электронов. При подаче на обычный затвор повышенного значения программирующего напряжения через тонкий слой оксида электроны туннелируют в плавающий затвор, в котором создается заряд отрицательного знака. После снятия программирующего напряжения и возврата напряжения на затворе к уровню рабочих напряжений электроны оказываются в ловушке, где могут сохраняться в течение десятков лет. При этом транзистор будет заперт, так как отрицательный заряд плавающего затвора создает электрическое поле, противодействующее полю положительно заряженного затвора. При отсутствии заряда в плавающем затворе рабочее положительное напряжение на внешнем затворе обеспечивает отпирание транзистора (создает между стоком и истоком проводящий канал). На рис. 7.3,а показан режим программирования ЛИЗМОП-транзистора, а на рис. 7.3,6 - режим стирания заряда. Стрелками показаны пути туннелирования электронов через тонкий слой оксида.

Память конфигурации типа EEPROM на основе ЛИЗМОП для обновления содержимого не требует извлечения микросхемы из устройства и допускает большое число циклов стирания данных (от десятков тысяч до миллиона). Стирание старой информации и запись новой занимают время порядка миллисекунд.

Программирование заряда в плавающем затворе используется и в технике EPROM, причем в этом случае возможно применение ЛИЗМОП-транзисторов с одним плавающим затвором при стирании заряда путем облучения кристалла ультрафиолетовыми лучами через специальное окошко в корпусе микросхемы. Стирание информации в памяти конфигурации типа EPROM является длительным процессом, занимающим десятки минут, и производится на специальном программаторе. Число циклов стирания существенно ограничено (сотни, тысячи). В последнее время схемотехника EEPROM быстро совершенствуется и все больше вытесняет схемотехнику EPROM, широко распространенную в предыдущих программируемых схемах.

Вариантом схемотехники EEPROM является так называемая Flash-память. Принцип работы элементов этой памяти не отличается от принципа работы описанных ЛИЗМОП-транцисторов,

но новый технологический уровень их реализации и полученные вследствие этого улучшенные технико-экономические характеристики, как и блочное стирание данных, выделили Flash-память в отдельный класс, который считается вершиной достижений в области памяти с электрическим стиранием данных, хранимых в виде зарядов плавающих затворов.

В схемах со статической памятью конфигурации роль программируемого соединения играет транзисторный ключ. Такой ключ, управляемый триггером памяти конфигурации, показан на рис. 7.4. Ключевой транзистор Т2 замыкает или размыкает участок ab в зависимости от состояния триггера, подключенного к затвору транзистора

Рис. 7.4. Ключевой транзистор, управляемый триггером памяти конфигурации

|

. При программировании сигналом с линии выборки включается транзистор Т1 и с линии записи/чтения подается сигнал установки или сброса триггера. В рабочем режиме транзистор Т1 заперт, а триггер сохраняет заданное ему состояние. Соответственно характеру памяти конфигурации (статическая триггерная) схемы такого типа называют SRAM-based.

Загрузка тех или иных данных в память конфигурации программирует микросхему. Процесс программирования может производиться неограниченное число раз и с высокой скоростью. При выключении питания конфигурация разрушается, поэтому после каждого включения питания требуется новая загрузка данных в память конфигурации. Такая загрузка может производиться из какой-либо энергонезависимой памяти за время порядка миллисекунд (в зависимости от объема файла конфигурации за единицы, десятки, сотни миллисекунд или даже больше). Триггеры памяти конфигурации распределены по всей площади кристалла и размещаются вблизи тех схем, которые они конфигурируют.

В современных микросхемах программируемой логики триггерная память конфигурации занимает важнейшее место.

Завершая обсуждение общих вопросов, связанных с особенностями микросхем программируемой логики, следует подчеркнуть, что они выпускаются промышленностью как полностью готовые. При использовании таких схем потребитель не обращается к изготовителю для проведения каких-либо завершающих разработку операций и выполняет программирование микросхем самостоятельно. Это дает основание отнести ИС ПЛ к стандартной продукции электронной промышленности, что ведет к известным положительным последствиям - массовости производства и снижению стоимости микросхем.