¬ведение

—егодн€шнюю жизнь невозможно представить без вычислитель≠ных устройств (¬”), скрытых в бытовой технике, измерительных и медицинских приборах, управлении агрегатами транспортных средств, телекоммуникаци€х, чип-картах и т.п. ¬ персональных компьютерах, которых сейчас в мире сотни миллионов штук, функ≠ции периферийных устройств исполн€ют различные специализи≠рованные ¬”. ≈сли мысленно охватить всю электронику, используе≠мую человеком, то в целом, на один универсальный микропроцессор приход€тс€ многие дес€тки специализированных ¬”. „исло новых применений ¬” стремительно возрастает, а сроки их разработки неуклонно сокращаютс€.

ќсновна€ часть специализированных ¬” реализована на микро≠контроллерах. Ќо остаетс€ большое множество задач, требующих экстремальных характеристик быстродействи€, пропускной способ≠ности, энергопотреблени€, дл€ реализации которых необходима раз≠работка заказных микросхем. ¬ последнее врем€ €дро микрокон≠троллера и необходимые сложные периферийные устройства выпол≠н€ют в виде системы на кристалле (—Ќ ). ¬озрастающий объем разработок специализированных ¬” и —Ќ требует освоени€ новых технологий их проектировани€.

ѕроектирование ¬” представл€ет собой поэтапное преобразование технического описани€ ¬” с уточнением и детализацией описани€ на каждом новом этапе. Ќачальное описание специализированного ¬” включает в себ€ алгоритмы его функционировани€, пор€док взаимодействи€ с внешним миром, а также технические ограниче≠ни€, такие как быстродействие, энергопотребление, габариты и т.п.

“радиционное проектирование ¬” основано на составлении на каждом этапе различных графических схем. ¬ соответствии с назва≠нием этапа, различают схемы алгоритмов, схемы электрические структурные, функциональные и принципиальные. „ерчение схем св€зано с высокой трудоемкостью, затратами времени, а главное - с трудностью вы€влени€ и исправлени€ ошибок проектировани€. ѕо≠всеместное внедрение —јѕ– электронных схем обеспечивает умень≠шение трудозатрат, повышение качества проектов, но не мен€ет в корне характер проектировани€, как ручного составлени€ схем.

»спользование при разработке ¬” таких €зыков проектировани€, как VHDL и Venlog, позвол€ет отказатьс€ от составлени€ схем на

большинстве этапов разработки ¬”. “ехнологи€ проектировани€ ¬” с помощью VHDL предполагает описание исходных алгоритмов функционировани€ аппаратуры и ее интерфейса на €зыке VHDL и автоматическую трансл€цию этого описани€ до уровн€ логических схем и далее - до уровн€ масок микросхем или прошивки програм≠мируемых логических интегральных схем (ѕЋ»—). ѕри этом схемы ¬” в графическом виде практически не используютс€, а отсутствие ошибок в проекте автоматически контролируетс€ средствами вери≠фикации. ак основное средство верификации, используетс€ моде≠лирование функционировани€ ¬” на VHDL-симул€торе на всех эта≠пах проектировани€. –азработка современных ¬” без использовани€ €зыков VHDL и Verilog стала практически невозможной.

язык VHDL - необычный €зык, как дл€ программистов, так и дл€ разработчиков аппаратуры. Ёто св€зано с тем, что по своей при≠роде VHDL - €зык параллельного программировани€. Ќачинающие программисты иногда путаютс€ в основах программировани€ на VHDL, допускают трудно вы€вл€емые ошибки, а их результирую≠щие проекты ¬” нередко оказываютс€ далекими от оптимальных. роме того, современна€ технологи€ проектировани€ средств ¬” основана на р€де особенных требований, предъ€вл€емых к проек≠там, описанным на VHDL. ј большинство разработчиков аппарату≠ры, изучающих VHDL, с этими требовани€ми мало знакомо. ѕоэто≠му цель данной книги - помочь освоить VHDL, как современное средство проектировани€ ¬”.

|

|

|

ратко о VHDL

“радиционно, разработка электрических схем €вл€етс€ одним из этапов проектировани€ средств вычислительной техники. Ёта ответ≠ственна€ работа св€зана с большими трудозатратами, контролем правильности и соответстви€ задуманному проекту, необходимостью четкого и емкого описани€ созданных схем, трудност€ми с их со≠провождением и модернизацией. —јѕ– вычислительной техники, как правило, имеют средства ввода и редактировани€ схем. ќднако два дес€тилети€ назад при разработке —Ѕ»— стали отказыватьс€ от схемного проектировани€.

язык Very high speed integrated circuits Hardware Description Language (VHDL) был разработан в 1983 г. по заказу ћинистерства обороны —Ўј с целью формального описани€ логических схем дл€ всех этапов разработки электронных систем. ќн €вл€етс€ стандарт≠ным €зыком с 1987 г. —тандартом 1993 г. закреплены многие его усовершенствовани€ [1]. Ќар€ду с €зыком Verilog он €вл€етс€ базо≠вым €зыком при разработке аппаратуры современных вычислитель≠ных систем.

¬ чем преимущества VHDL над схемным проектированием?

ѕроектирование больших вычислительных устройств (¬”). — по≠мощью VHDL проще и быстрее ввести и проверить большой проект. ƒес€тью строками VHDL можно описать как 1, так и 100000 триг≠геров. ћикросхему с интеграцией более 10000 вентилей разработать только с помощью электрических схем практически невозможно по причине громоздкости схем.

ѕроект на VHDL Ч объединение структуры ¬” и алгоритма его функционировани€. ƒл€ ¬”, описанного на VHDL, необ€зательно выполн€ть проверку правильности его функционировани€, напри≠мер, путем его макетировани€. „тобы определить, правильно ли ¬” выполн€ет заданный алгоритм, достаточно его VHDL-программу за≠пустить на исполнение в симул€торе VHDL. —оответствующие —јѕ–

преобразуют VHDL-описание в комплект документации дл€ изготов≠лени€ работоспособного устройства.

ѕроект на VHDL Ч самодокументированный, т.е. он не требует дополнительного технического описани€ или представлени€ в виде схем. Ќечеткость и небрежность описани€ исключаютс€, так как проект на VHDL несложно проверить.

¬ысока€ надежность проекта. —интаксический анализ, моделиро≠вание и компил€ци€ в логическую схему быстро вы€вл€ют ошибки проекта.

ѕроект на VHDL Ч универсальный проект. –азработанный одна≠жды вычислительный блок может быть использован во многих дру≠гих проектах. ѕри этом многие структурные и функциональные па≠раметры блока могут быть настраиваемыми (параметры разр€дно≠сти, объема пам€ти, элементна€ база, состав блока и структура межсоединений).

ѕроект на VHDL Ч портативный проект. –азработанный дл€ од≠ной элементной базы, проект ¬” без труда переноситс€ на другую элементную базу, напр. —Ѕ»— с различной технологией.

ѕроект на VHDL Ч долгоживущий проект. Ёлектрическа€ схема всегда разрабатываетс€ под конкретную элементную базу и интер≠фейс. “ак как элементна€ база смен€етс€ через 2-5 лет, за этот же период устаревают и электрические схемы, использующие еЄ. ѕро≠ект ¬” на VHDL может быть повторно использован через несколько лет. ’орошее техническое решение (напр., изобретение), описанное на VHDL, может быть востребованным в течение дес€тилетий.

|

|

|

VHDL - универсальное средство описани€ ¬” на уровн€х:

□ алгоритмическом,

□ структурном,

□ регистровых передач (RTL) и потоков данных (dataflow),

и логическом,

□ аналоговых схем.

’од проектировани€ с использованием VHDL

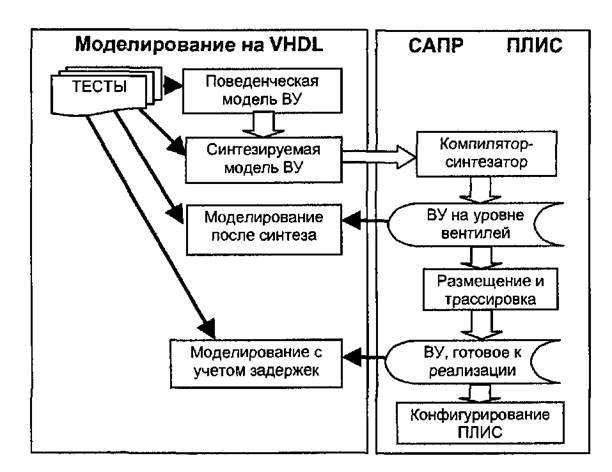

Ќа рис. 1 показана схема разработки проекта ¬”, предназначен≠ного дл€ исполнени€ в программируемой логической интегральной схеме (ѕЋ»—).

¬начале ¬” описываетс€ в виде своей поведенческой модели, на которой отрабатываетс€ задуманный алгоритм функционировани€ ¬”. «атем эта модель вручную перерабатываетс€ в синтезируемую модель ¬”, описанную на уровне регистровых передач. “ака€ мо≠дель, будучи странслированной компил€тором-синтезатором, дает проектную документацию в виде файла описани€ схемы ¬” на уровне вентилей (EDIF-файл). ѕри этом автоматически выполн€етс€ логическа€ оптимизаци€ ¬”. ќдновременно этот файл автоматиче≠ски преобразуетс€ в VHDL-модель ¬” на уровне вентилей.

ѕроект ¬” в виде Electronic Distribution International Format (≈Ѕѕ√)-файла принимаетс€, как исходные данные, всеми —јѕ– из≠готовлени€ ѕЋ»— и —Ѕ»—. Ёти —јѕ– выполн€ют замену вентилей на библиотечные компоненты, их размещение на площади кристал≠ла, трассировку межсоединений, проектирование масок, проверку соответстви€ проектным нормам и т.п. ¬ результате, записываютс€ файлы проектной документации изготовлени€ кристалла и его логи-

ческой модели, учитывающей задержки, как в вентил€х, так и в межсоединени€х. Ёта модель также представл€етс€ на VHDL.

—тоимость ошибок при проектировании —Ѕ»— очень высока, осо≠бенно на ранних этапах. ѕоэтому все этапы проектировани€ - алго≠ритмический, структурный, логический, технологический - сопро≠вождаютс€ моделированием ¬” с помощью, так называемого, испы≠тательного стенда (testbench). Ётот стенд представл€ет собой VHDL-модель, составными част€ми которой €вл€ютс€ модель тестируемого ¬” и модели генератора тестовых сигналов и логического анализа≠тора, провер€ющих правильность функционировани€ ¬”. ѕричем на всех этапах может использоватьс€ один и тот же испытательный стенд и те же тестовые файлы.

VHDL используетс€ в современных —јѕ–

»сторически сложилось, что в микроэлектронной индустрии наи≠большее распространение получил €зык Verilog. ѕолтора дес€тиле≠ти€ назад этот €зык выиграл конкурентную борьбу с другими €зы≠ками задани€ ¬”, благодар€ небольшим вычислительным ресурсам, требуемым от прежних рабочих станций и достаточно точным ре≠зультатам моделировани€ —Ѕ»—. VHDL - более универсальный и гибкий €зык, но он проигрывал в быстродействии €зыку Verilog, особенно при моделировании на уровне вентилей и транзисторов. VHDL получил широкое распространение в университетах и ис≠следовательских учреждени€х, так как это строгий, стройный, уни≠версальный и расшир€емый €зык. “ак, например, по€вились пакеты VHDL дл€ аналогового моделировани€, моделировани€ многознач≠ной логики. роме того, симул€торы VHDL были гораздо дешевле симул€торов Verilog.

¬се современные —јѕ– микроэлектроники имеют компил€торы как с Verilog, так и с VHDL. ѕрограммист, освоивший VHDL, без особого труда может перейти к программированию на €зыке Verilog. Ќо программисту, знающему Verilog, перейти к VHDL труднее.

¬ажнейшими качествами VHDL в —јѕ– выступают следующие:

√ибкость. ѕроект, описанный на VHDL, может быть легко на≠строен под конкретные задачи потребител€.

”ниверсальный €зык. VHDL - общеприн€тый €зык дл€ всех ос≠новных фирм - изготовителей микросхем ѕЋ»—, ѕЋћ, заказных

—Ѕ»—, как стандартный €зык дл€ задани€ сложных проектов. ѕро≠ектирование с VHDL - устойчива€ тенденци€ в инженерной техно≠логии. —уществуют компил€торы, транслирующие VHDL-программы в эквивалентные им Verilog-программы.

|

|

|

ћоделирование с учетом задержек. ‘ирмы-изготовители микро≠схем в своих —јѕ– обеспечивают генерацию моделей результатов размещени€ и трассировки, описанных на VHDL.

—тандартное подключение блоков. онструкции €зыка, такие как entity, port map, configuration, обеспечивают надежную и бы≠струю стыковку блоков, разработанных разными фирмами и разра≠ботчиками, в различном сочетании.

—тандартное тестирование. Ќа всех этапах разработки выполн€≠етс€ тестирование по одной методике одними и теми же тестами.

VHDL Ч стандарт будущего. ¬се новые —јѕ– основаны на техно≠логии трансл€ции описани€ ¬” на €зыке описани€ аппаратуры. »с≠пользование VHDL - гаранти€ того, что через 5 и 10 лет найдетс€ —јѕ–, поддерживающа€ старые разработки.

“ехнологи€ разработки систем на кристалле

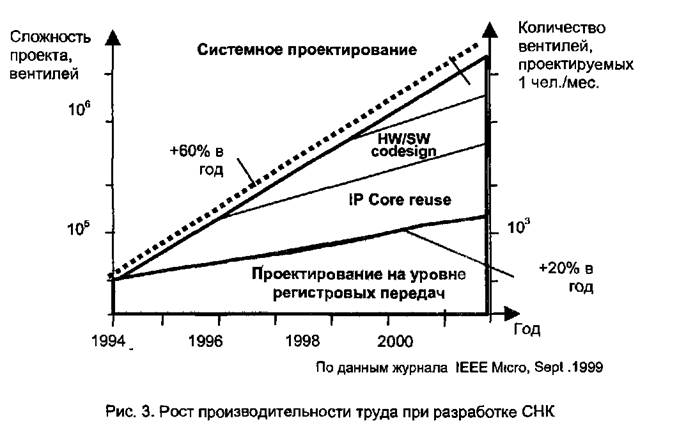

—огласно известному закону ћора, количество транзисторов на кристалле —Ѕ»— с каждым годом увеличиваетс€ приблизительно на 60 %. — определенного момента времени то оборудование, которое размещалось на одной печатной плате, стало возможным поместить на одном кристалле (рис. 2). ѕричем это становитс€ выгодным, бла≠годар€ уменьшению общей стоимости, числа необходимых микро≠схем, энергопотреблени€, повышению надежности ¬”.

“аким образом, на одном кристалле размещаетс€ не только кон≠кретное функциональное устройство, например, центральный про≠цессор, но и другие устройства, такие как ј÷ѕ, ќ«”, ѕ«”, блоки цифровой обработки сигналов, интерфейсные узлы и т.п., допол≠н€ющие его до законченной системы блоков. ѕоэтому такое ¬” при-

н€то называть System On the Chip (SOC) - системой на кристалле (CHK) [2].

—Ќ - это, как правило, заказна€ —Ѕ»—. „тобы разработка —Ќ себ€ окупила, необходимо реализовать дес€тки и сотни тыс€ч —Ѕ»—. ѕроект ¬”, реализованный на ѕЋ»—, может быть выгодным при парти€х, как в дес€тки, так и в дес€тки тыс€ч экземпл€ров, благо≠дар€ дешевизне разработки и производства такой ¬”. –азработка такого ¬” длитс€, как минимум, в 2 раза быстрее, чем проектиро≠вание —Ѕ»—. Ёто обусловило бурное распространение ѕЋ»— в каче≠стве элементной базы —Ќ .

Ќаиболее трудоемкими и ответственными этапами разработки —Ќ выступают этапы структурного проектировани€ и верификации соответстви€ ¬” заданным алгоритмам функционировани€. ѕоэтому эффективность —јѕ– микросхем и производительность разработчи≠ков, выполн€ющих проектирование на уровне регистровых передач, посто€нно растет приблизительно на 20 % в год. Ќо, начина€ с се≠редины 90-х годов, производительность разработчиков стала заметно отставать от роста сложности —Ќ (рис. 3).

ѕервым направлением улучшени€ технологии разработки —Ќ , ориентированным на уменьшение зазора между ростом производи≠тельности проектировани€ на уровне регистровых передач и ростом сложности —Ќ , €вл€етс€ применение крупных библиотечных вы≠числительных модулей (Intellectual Property Cores). Ёти модули должны быть надежно повтор€емыми и настраиваемыми под решае≠мые задачи в р€де проектов —Ќ . ѕовторное применение таких мо≠дулей (IP Core reuse), которые можно назвать вычислительными заготовками за их функциональную и технологическую адапти≠руемость, позвол€ет уменьшить трудозатраты и сроки проектирова≠ни€ —Ќ .

¬торое направление - это разработка —јѕ– совместного проектиро≠вани€ аппаратно-программного обеспечени€ (Hardware - Software Codesign). јрхитектура —Ќ , как правило, включает в себ€ микропро≠цессорное €дро с периферийными устройствами в различном сочетании. ќбычно процесс разработки ¬” с такой архитектурой состоит из трех последовательных этапов: проектировани€ электрической схемы аппа≠ратуры, разработки матобеспечени€ микропроцессора и стыковки мато≠беспечени€ с аппаратурой.

|

|

|

ƒл€ ускорени€ проектировани€ разрабатывают —јѕ–, котора€ не только служит дл€ совместного выполнени€ этих этапов, но и обеспечивает моделирование работы —Ќ и ее верификацию в комплексе.

Ќаибольшее ускорение разработки —Ќ может дать внедрение —јѕ– непосредственного отображени€ алгоритмов в аппаратуру, т.е. —јѕ– системного проектировани€. Ќапример, така€ —јѕ– может включать в себ€ трансл€цию программы с €зыка высокого уровн€, таком как C++, с автоматическим разделением вычислительных за≠дач между микропроцессорным €дром и спецпроцессорами и други≠ми периферийными устройствами.

ƒл€ более плавного перехода от алгоритма функционировани€ системы, описанного на €зыке C++, к аппаратно-программному опи≠санию всЄ чаще примен€етс€ €зык System-C. ќсобенность этого под≠множества €зыка C++ в том, что его функции имеют взаимно одно≠значное соответствие с конструкци€ми €зыков VHDL и Verilog, опи≠сывающими аппаратуру.

¬ычислительные заготовки

¬ крупных фирмах, долгие годы занимающихс€ разработкой —Ѕ»—, а теперь и —Ќ , наработаны большие библиотеки стандарт≠ных модулей, таких как: ќ«”, јЋ”, периферийные устройства. ¬ новых проектах —Ќ некоторые блоки приходитс€ разрабатывать заново, а остальные - обычно берутс€ из библиотеки. ѕри этом если модуль не€сно описан, не имеет удобного интерфейса, документа≠ции, комментариев, испытательного стенда с надежными тестами, то он повторно примен€тьс€ не будет.

≈сли такой модуль изначально оформлен в виде вычислительной заготовки, то он будет без лишних проблем вставл€тьс€ в любой но≠вый проект. Ѕолее того, лицензию на него можно предлагать другим фирмам-разработчикам —Ќ . –исунки 2, 4 иллюстрируют суть вы≠числительной заготовки (IP core).

1. VHDL и технологи€ систем на кристалле

√ибкие заготовки обычно подстраиваютс€ к услови€м нового про≠екта в широких пределах и независимы от его технологии (сери€ ѕЋ»—, технологи€ —Ѕ»—). ќбычно в них задаютс€ разр€дность дан≠ных, объем пам€ти, таблицы констант, перечень периферийных уст≠ройств, иногда - быстродействие, которое пропорционально аппара≠турным затратам. ћинимизаци€ аппаратурных затрат вычислитель≠ных заготовок обеспечивает не только уменьшение стоимости —Ќ , но и минимизацию его энергопотреблени€, что €вл€етс€ важным фактором дл€ портативных и энергонезависимых ¬”, в которых примен€ютс€ —Ќ .

„тобы проект ¬” был прин€т как гибка€ вычислительна€ заго≠товка, он должен иметь:

а исчерпывающую и €сную документацию;

а текст описани€ на VHDL или Verilog в хорошем стиле дл€ синтеза, заготовка должна быть настраиваемой под техниче≠ские услови€ потребител€;

а хорошие средства верификации в виде испытательных стен≠дов, исчерпывающих тестов, возможно, экспериментальных макетов;

а четкую методику того, как ¬” вставл€ть в —Ќ , включающую надежные скрипты (программы на макро€зыке —јѕ–, автома≠тизирующие тестирование и создание жесткой или твердой за≠готовки) [2].

¬ сегодн€шних услови€х, чтоб быстрее перейти от идеи к "желе≠зу", эффективнее провести проектирование новой —Ќ , необходимо эту —Ќ "собрать" из имеющихс€ вычислительных заготовок (рис. 2), а отсутствующие заготовки - приобрести на рынке IP cores, который бурно развиваетс€ в последние годы.

≈сли приобрести не удастс€ или если проект - исследователь≠ский, то необходимую заготовку можно поискать, например, в банке бесплатных IP cores, что на сайте www.opencores.org. Ётот банк соз≠дан по инициативе организаций, содействующих развитию техноло≠гии —Ќ , а также инженеров, желающих поделитьс€ своими ре≠зультатами. ≈сли оба этих пути не устраивают, то придетс€ ¬” про≠ектировать самосто€тельно и данна€ книга может этому помочь.

ѕрограммируемые логические интегральные схемы

„то такое FPGA?

ѕрограммируемые логические интегральные схемы (ѕЋ»—) по€≠вились полтора дес€тилети€ назад как альтернатива программируе≠мым логическим матрицам (ѕЋћ). ѕЋ»— отличаютс€ от последних как по архитектуре, так и по технологии изготовлени€.

ѕЋћ представл€ет собой матрицу многовходовых (более дес€тка входов) логических элементов с триггерами, в которых программи≠руютс€ конституенты единиц дизъюнктивных нормальных форм функций этих элементов. ¬ первых ѕЋћ программирование выпол≠н€лось пережиганием перемычек между источниками сигналов пе≠ременных и входами логических элементов. «атем перемычки заме≠нили ћќѕ-транзисторами с плавающим затвором, как в электриче≠ски перепрограммируемом ѕ«”. ѕоэтому сейчас. ѕЋћ изготов≠л€ютс€ по технологии флэш-пам€ти. Ѕольшие ѕЋћ (CPLD) отличаютс€ только тем, что несколько ѕЋћ собраны на одном кри≠сталле и объединены программируемым полем св€зей.

|

|

|

ѕЋ»— представл€ет собой матрицу маловходовых (от двух до п€≠ти входов) логических элементов, триггеров, отрезков линий св€зи, соедин€емых перемычками из полевых транзисторов. —уд€ по анг≠лийскому названию ~ Field Programmable Gate Array (FPGA), ѕЋ»— программируютс€ изменением уровн€ электрического пол€ (field) в затворах этих транзисторов. «атворы всех "программирующих" по≠левых транзисторов подключены к выходам триггеров одного длин≠ного сдвигового регистра, который заполн€етс€ при программирова≠нии ѕЋ»—. Ќекоторые из участков этого регистра могут также ис≠полн€ть роль €чеек ѕ«”.

ѕрошивка обычно хранитс€ в ѕ«”, сто€щем р€дом с ѕЋ»—. ѕо≠сле включени€ питани€ или по сигналу сброса она автоматически переписываетс€ в программирующий сдвиговый регистр ѕЋ»—. Ётот процесс называетс€ конфигурированием ѕЋ»—. “ак как основу ѕЋ»— составл€ют триггеры, хран€щие прошивку, называемую кон≠фигурацией, то ѕЋ»— изготавливаютс€ по технологии микросхем статического ќ«”.

ѕо сравнению с CPLD, ѕЋ»— выигрывают, во-первых, в неогра≠ниченном количестве перепрограммирований, во-вторых, в логиче-

ской емкости, в том числе в удельной емкости вентилей на цент, в-третьих, в малом энергопотреблении. ак правило, ѕЋ»— имеют на два-три пор€дка большую емкость в числе эквивалентных логиче≠ских вентилей, чем CPLD и также как статическое ќ«”, почти не потребл€ют энергии при отсутствии переключений. ѕоскольку топо≠логи€ ѕЋ»— регул€рна и масштабируема, период разработки и вне≠дрени€ ѕЋ»— новых серий сравнительно мал, и они изготовл€ютс€ по самой современной технологии. Ќаконец, у ѕЋ»— на пор€док выше надежность (ниже интенсивность отказов), чем у CPLD.

јрхитектура ѕЋ»— фирмы Xilinx

‘ирма Xilinx принадлежит к числу родоначальников ѕЋ»— и самых крупных их производителей. Ќиже рассматриваетс€ краткое описание архитектурных особенностей ѕЋ»— серии Virtex выпус≠каемой этой фирмой [3]. Ёти особенности наследуютс€ в новых сери≠€х ѕЋ»—, а также в серии Spartan, микросхемы которой призваны заменить заказные —Ѕ»— в мало- и среднесерийном производстве изде≠лий электроники. роме того, принципы функционировани€ структур≠ных элементов ѕЋ»— этой серии узнаваемы в архитектурах ѕЋ»— дру≠гих фирм-производителей, таких как, Altera, Actel, Atmel.

“опологи€ ѕЋ»—

Ќа площади кристалла ѕЋ»— (рис. 5.) размещены матрица кон≠фигурируемых логических блоков ( ЋЅ или CLB), матрица отрезков линий межсоединений, покрытых матрицами из полевых транзисто-

|

ров - перемычек (ћѕ). ѕо

кра€м кристалла размеше≠

ны блоки настраиваемых

ќ«” - BlockRAMs. ѕо пе≠

риметру кристалла разме≠

щены блоки ввода-вывода

сигналов (IOBs), а также

периферийный канал ли≠

ний межсоединений, на≠

зываемый VersaRing,

предназначенный дл€ сое≠

динени€ ЋЅ с произ≠

вольным ё¬ линией св€≠

зи с малой задержкой.

|

ƒл€ обеспечени€ достаточ-11 ых возможностей маршрута-1ации межсоединений, а также i [ х высокого быстродействи€, используетс€ до дев€ти слоев металлизации в которых реали-юваны матрица отрезков линий межсоединений, система линий < инхронизации и питани€.

Ћогическа€ таблица

–оль основного логического элемента в ѕЋ»— играет логи≠ческа€ таблица (Ћ“) или look-

up table (LUT), представл€юща€ собой однобитное ќ«” на 16 €чеек (рис. 6).

¬ Ћ“ по адресу G3,G2,G1,G0 записана единица, если код адреса представл€ет собой конституенту единицы заданной четырехвходо-иой логической функцией. Ќапример, если по адресу 1,1,1,1 записа≠на единица, а по остальным адресам - ноль, то Ћ“ реализует че-1 ырехвходовую функцию ». Ќа рис. 6 показан пример кодировани€ функции »сключающее »Ћ» на четыре входа. “риггеры Ћ“ вход€т и состав программирующего сдвигового регистра, и их начальное (осто€ние заполн€етс€ в период конфигурировани€ ѕЋ»—.

“риггер

¬ ѕЋ»— используютс€ программируемые D-триггеры (рис. 7). ѕри конфигурировании можно задать такие режимы работы триг-

|

iepa, как триггер с начальным сбросом (R) или начальной ус-[ ановкой (S), с записью по фронту или спаду синхро-< ерии, с разрешением или без разрешени€ записи.

ѕосле окончани€ конфигу≠рировани€ ѕЋ»— выдает сиг-кал общего сброса GSR, кото≠рый устанавливает все тригге≠ры в 0 или 1.

|

—труктура ЋЅ

¬ базовой серии ѕЋ»— ’—4000 фирмы Xilinx основной единицей обору≠довани€ считаетс€ ЋЅ, состо€щий из двух триггеров, двух Ћ“ и схем уско≠ренного переноса, суммировани€ и управлени€ CY. ¬ новых сери€х ѕЋ»— количество триггеров и Ћ“ в ЋЅ уве≠личилось вдвое и вчетверо. „тобы ос≠тавить дл€ всех серий одну и ту же единицу оборудовани€, условились на≠зывать ЋЅ из двух триггеров и двух Ћ“ эквивалентным ЋЅ (Ё ЋЅ) или CLB slice. “аким образом, ЋЅ серии Virtex состоит из двух Ё ЋЅ, а серии VirtexII - из четырех Ё ЋЅ (рис. 8).

—хемы дл€ ускорени€ арифметических операций

¬ Ё ЋЅ две Ћ“ и два триггера соеди-

нены вместе через схему ускоренного переноса и два однобитных полусумматора (рис. 9). Ёти схемы позвол€ют эффективно реа≠лизовать многоразр€дные параллельные сумматоры, а на их осно≠ве - различные счетчики и јЋ”.

ƒл€ минимизации оборудовани€ и ускорени€ вычислени€ опера≠ции умножени€ используетс€ дополнительна€ схема поразр€дного произведени€. Ќеобходимо добавить, что в новой серии Virtex2 реа≠лизованы аппаратные умножители 18 на 18 разр€дов.

|

ћультиплексоры в ѕЋ»—

Ѕольшую долю оборудовани€ в ¬— за≠нимают мультиплексоры. — помощью одного Ћ“ можно реализовать двух-входовой мультиплексор. ƒл€ эф≠фективной реализации 4-х и более входовых коммутаторов в ЋЅ имеютс€ схемы мультиплексоров F5 и F6, которые играют роль верхних уровней древовидного мультиплексора (рис. 10).

Ўины с трем€ состо€ни€ми

ѕрименение шин с трем€ состо€ни€ми - типичное схемное реше≠ние ¬”, реализованных на плате. Ѕлагодар€ такому решению, легко достигаетс€ многомодульность и наращиваемость системы, низкие аппаратурные затраты и малые задержки в системе межсоединений. I in утри заказных —Ѕ»— редко примен€ютс€ шины с трем€ сос≠то€ни€ми из-за технологических трудностей их безотказной реали≠зации, а также увеличенной задержки их переключени€.

Ќесмотр€ на это, в ѕЋ»— фирмы ’Ўпх всЄ-таки широко приме≠н€ютс€ шины с трем€ состо€ни€ми, хот€ это существенно повышает их себестоимость. «ато, во-первых, проще выполнить переход от проекта схемы на плате к проекту —Ќ . ¬о-вторых, ¬” с общими шинами, к которым подключено несколько дес€тков модулей, имеет аппаратные затраты в несколько раз меньше, чем такое же ¬”, в котором глины заменены на эквивалентную схему из системы муль≠типлексоров. ¬-третьих, с помощью общих шин эффективно реали-иовать встроенное распределенное ќ«”, о котором пойдет речь ниже.

ƒл€ реализации общей шины каждый ЋЅ имеет два буфера с Хгром€ состо€ни€ми BUFT, которые через транзисторы-перемычки могут подключатьс€ к общим шинам, проход€щим вдоль всего кри≠сталла (рис. 11).

¬ обычных шинах третье состо€ние характеризуетс€ уровнем, наход€щимс€ между уровн€ми логической 1 и логического 0. ќдна≠ко в случае, когда все тристабильные буферы будут в третьем (за-

|

крытом) состо€нии, выходные каскады приемников, подключенных к общей шине, ѕудут полуоткрытыми, через них потечет большой посто€нный ток, и они могут вый≠ти из стро€. ƒл€ исключени€ такого элек≠трического режима, в ѕЋ»— обща€ шина нагружена на концах специальной тригтерной схемой - Weak Keeper, котора€ выводит уро≠вень шины или к уровню Ќ, или к уровню L (слабые 1 или 0), если все буферы закрыты.

ќ«” в ѕЋ»—

ƒл€ реализации в ѕЋ»— модулей ќ«” предусмотрено две возможности. ѕервую воз≠можность предоставл€ет кажда€ Ћ“, котора€

|

|

может быть сконфигурирована как 16-битовое синхронное ќ«”. ƒве соседних Ћ“ могут быть сконфигурированы как 16-битовое двухпортовое ќ«” с записью и чтением по одному адресу и чте≠нием по другому адресу (рис. 12). ѕри этом дл€ реализации син≠хронного режима записи входной бит данного, сигнал записи и ад≠рес запоминаютс€ в триггерах-защелках, а дл€ чтени€ по второ≠му адресу из блока второй Ћ“ ис-

пользуетс€ только мультиплексор чтени€.

ƒл€ наращивани€ емкости пам€ти выхо≠ды нескольких ЋЅ с модул€ми ќ«” через тристабильные буферы подключаютс€ к об≠щим шинам. ѕри этом- требуетс€ допол≠нительное оборудование только дл€ по≠строени€ схемы дешифрации адреса, кото≠ра€ выдает сигналы выборки той или иной Ћ“ дл€ записи или того или другого три-стабильного буфера дл€ чтени€. “акое ќ«” распределено по площади кристалла и по≠этому названо Distributed RAM.

≈сли Ћ“ запрограммировать как прими≠тив SRL16, то из ее триггеров будет реали≠зован 16-разр€дный сдвиговый регистр с однобитовым входом и программируемым номером выходного разр€да, т.е. пам€ть FIFO регулируемой длины. “акие регистро≠вые линии задержки удобно использовать при проектировании конвейерных спе≠циализированных ¬”, ¬” с поразр€дной

обработкой, буферов дл€ приема и передачи данных и т.п.

¬торую возможность предоставл€ют отдельные блоки пам€ти BlockRAM. ¬ ѕЋ»— серии Virtex они могут быть сконфигурирова≠ны, как ќ«” объемом 256 16-разр€дных слов, 512 8-разр€дных слов, и т.д. Ёта пам€ть может быть запрограммирована как однопортова€ или как полностью двухпортова€ пам€ть (рис. 13). Ќачальное со-

сгоиние этой пам€ти задаетс€ при ее конфигурировании, поэтому ими может быть использована также как ѕ«”. ¬ каждой новой се≠рии ѕЋ»— объем блоков BlockRAM и их число - увеличиваютс€.

Ѕлоки ввода-вывода сигналов

ѕЋ»— наход€т широкое применение благодар€ тому, что их можно включать в большинство проектов ¬” и ими можно замен€ть схемы, реализованные на устаревшей элементной базе. ѕредпосыл≠кой этому служит большое число блоков ввода-вывода сигналов ё¬, настраиваемых под различные стандарты электрического соединени€ иходов микросхем. Ќа рис. 14 показана структура одного ё¬.

—игнальный вывод ѕЋ»— получил название PAD. — помощью на≠стройки к нему можно подключать внутренний нагрузочный рези≠стор PULLUP или резистор PULLDOWN, соединенные с шиной пи≠тани€ или шиной земли, соответственно. Ёти резисторы обеспечива≠ют режим выхода с открытым коллектором (стоком) дл€ систем с рп.шичными уровн€ми логики. ¬ходной сигнал с PAD поступает на компаратор IBUF, порог срабатывани€ которого программируетс€ мод уровни ““Ћ, ћќѕ, шины PCI и многие другие, а также может регулироватьс€ установкой подаваемого снаружи потенциала уровн€ срабатывани€ Vref. ƒл€ обеспечени€ временного сдвига сигнала от≠носительно фронта синхросерии, обеспечивающего надежный прием сигнала во внутренние триггеры, в цепь входного сигнала может иключатьс€ специальна€ схема задержки.

¬ыходной сигнал в ё¬ формируетс€ в тристабильном буфере OBUFT, причем его уровень максимального тока программируетс€ ступен€ми и может достигать 20 мј. ƒл€ обеспечени€ быстродействующего ввода-пмвода передаваемые и принимаемые биты данных, а также сигнал управлени€ тристабильным буфером могут запоминатьс€ в триггерах.

¬ ѕЋ»— новых поколений к сигнальным выводам кристалла подключаютс€ резисторы с программируемым сопротивлением, предназначенные дл€ согласовани€ импеданса источника или прием≠ника сигнала с импедансом линии св€зи. Ѕлагодар€ этому возможна на≠дежна€ высокочастотна€ передача данных между микросхемами.

Ќапр€жение питани€ ѕЋ»— каждого нового поколени€ посто€н≠но уменьшаетс€, благодар€ чему минимизируетс€ энергопотребление при высоком быстродействии (см. главу 4). ƒл€ того, чтобы обеспе≠чить согласование входных и выходных уровней дл€ как можно большего числа стандартов уровней напр€жени€ логических схем, на блоки ё¬ подаетс€ отдельное питание.

ё¬ сгруппированы в банки, и на каждый из банков можно пода≠вать различный уровень напр€жени€ питани€. Ќо дл€ ѕЋ»— по≠следних поколений это напр€жение не должно превосходить 3,3 ¬. —игнальные входы-выходы ѕЋ»— обычно защищены от перенапр€≠жени€ цепочками из ограничивающего резистора и диода, подключенных между PAD и лини€ми питани€ и земли. ѕоэтому обычно допускаетс€ подавать на входы PAD уровень, больший 3,3 ¬ через дополнительный резистор, ограничивающий входной ток и обеспечивающий входной уровень на PAD, не превосход€щий напр€≠жение питани€ плюс падение напр€жени€ на открытом диоде.

ѕри диагностике, отладке, в одном из режимов конфигурирова≠ни€, ѕЋ»— может быть переключена в режим пограничного скани≠ровани€ (Boundary Scan). ¬ этом режиме все ё¬ соедин€ютс€ в це≠почку одного длинного регистра сдвига. ѕутем стандартного внеш≠него управлени€ этим регистром сдвига через интерфейс JTAG можно считывать состо€ни€ выводов, подавать тестовые сигналы, конфигурировать ѕЋ»—.

¬ период конфигурировани€ ѕЋ»— дл€ того, чтобы подключае≠мые к ней устройства не функционировали неопределенным обра≠зом, выходы ё¬ отключаютс€ и на них обычно выставл€етс€ уро≠вень Ќ слабой единицы.

—истема синхронизации

ќдним из принципов разработки проектов дл€ ѕЋ»— €вл€етс€ принцип однотактной синхронизации, согласно которому все тригге≠ры в ¬” или в его блоке срабатывают одновременно по одному сиг≠налу синхросерии (см. главу 4). ƒл€ его реализации в ѕЋ»— син≠хросигналы распростран€ютс€ по быстродействующей древообразной

|

(e i it, котора€ обеспечивает почти одновременный приход фронта син≠хроимпульса на синхровходы всех i ршгеров (рис. 15).

ƒл€ надежного функциониро-иими€ ѕЋ»— синхросигнал дол≠жен подаватьс€ через вывод GCLKPAD и попадать в сеть синхро≠серии через буфер GCLKBUF.

¬ ѕЋ»— предусмотрено 4 вы≠пи д€ GCLKPAD, размещенных на iipoi ивоположных сторонах ее

корпуса. —инхросигнал может вырабатыватьс€ и внутри ѕЋ»—, по в этом случае его следует завести в сеть синхросерии через i лобальный буфер BUFG.

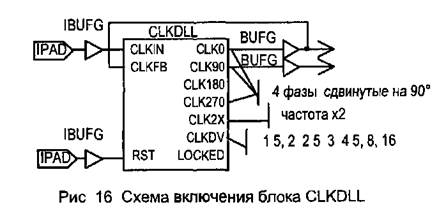

— помощью синхронного автомата, сконфигурированного в ѕЋ»—, можно измен€ть частоту и фазу синхросерии. Ќо в этом <* л учае ее временные параметры будут недостаточно ста-бпмьными, и поэтому такой подход обычно не примен€етс€. ƒл€ надежного регулировани€ частоты синхросерии в ѕЋ»— вклю-чпюг делители частоты синхросерии с автоподстройкой Ч блоки (MiKDLL. Ќа рис. 16 показана типична€ схема его включени€. »нок CLKDLL обеспечивает умножение частоты синхросерии в 2 рм.за, сдвиг ее фазы на 90, 180 и 270 градусов, деление на 1.5, 2, 2.5, 3, 4.5, 8 и 16.

|

онфигурирование ѕЋ»—

ƒл€ конфигурировани€ ѕЋ»— в ней предусмотрены входы зада≠ни€ режима ћ2, Ml, ћќ, вывод синхросерии программировани€ CCLK, вход последовательности конфигурации PROGRAM, выход флага окончани€ конфигурировани€ DONE и выводы порта JTAG. ¬ зависимости от установленного режима можно загружать прошивку ѕЋ»— через однобитовый вход PROGRAM, порт JTAG или 8-разр€дную шину D с использованием дл€ управлени€ выводов WRITE и BUSY.

онфигурирование через однобитовый вход длитс€ до нескольких дес€тков секунд. Ёто стандартный способ конфигурировани€ и дл€ него не требуетс€ дополнительного оборудовани€, кроме ѕ«” про≠шивки с однобитовым выходом. — помощью одной микросхемы ѕ«” можно запрограммировать несколько ѕЋ»—, цепи программирова≠ни€ которых дл€ этого соедин€ютс€ в кольцо.

ƒл€ реализации конфигурировани€ через шину D необходимо до≠полнительное внешнее устройство (автомат или микроконтроллер), управл€ющее записью и выдающее последовательность адресов чте≠ни€ на входы ѕ«” восьмиразр€дной шиной данных. «ато оно проис≠ходит значительно быстрее - практически с максимальным темпом чтени€ из ѕ«”.

¬ последнее врем€ выпускаютс€ ѕ«”, специально предназначен≠ные дл€ конфигурировани€ ѕЋ»— через шину D, в состав которых входит автомат управлени€ записью.