Двухступенчатый RST-триггер состоит из двух RST-триггеров, управляемых разными фазами тактового сигнала (рис. 8.38, а). Двухступенчатая структура триггера в условном графическом изображении обозначается двумя буквами ТТ (рис. 8.38, б).

Диаграмма работы двухступенчатого триггера показана на рис. 8.38, в. При С = 1 происходит запись информации в первый триггер. В это время второй триггер заблокирован нулевым уровнем сигнала. При С = 0 блокируется первый триггер, и информация из первого триггера переносится во второй.

Рассмотренный принцип построения триггеров обеспечивает высокую надежность работы, так как запись и хранение информации разделены: сначала информация записывается в первую триггерную ячейку при отключенной второй, затем хранится во второй ячейке при отключенной первой.

Т-триггер

Т-триггер изменяет свое состояние каждый раз, когда на его вход поступает управляющий сигнал. Название триггера происходит от английского слова tumble — переключать, кувыркаться. Структурная схема Т-триггера показана на рис. 8.39, а, условное графическое изображение — на рис. 8.39, б.

В интервале между входными импульсами состояния первого (назовем его Т1) и второго (Т2) триггеров в соответствии с принципом работы двухступенчатого триггера одинаковые. При поступлении управляющего импульса информация с выходов Т2 записывается в T1, в результате получается  и

и  . По окончании управляющего импульса информация из Т1 записывается в Т2, и состояние обоих триггеров становится одинаковым. Таким образом, в результате действия каждого управляющего импульса триггер переключается в противоположное состояние с задержкой, равной длительности управляющего импульса.

. По окончании управляющего импульса информация из Т1 записывается в Т2, и состояние обоих триггеров становится одинаковым. Таким образом, в результате действия каждого управляющего импульса триггер переключается в противоположное состояние с задержкой, равной длительности управляющего импульса.

JK-триггер

Название JK-триггера происходит от английских слов jump — прыгать и keep — держать. Структурная схема JK-триггера показана на рис. 8.40, а, а его условное графическое изображение показано на рис. 8.40, б. Это — синхронный двухступенчатый RS-триггер с перекрестными обратными связями и входной логикой, что позволяет устранить присущее RS-триггеру состояние неопределенности при одновременной подаче на оба информационных входа логических единиц. JK-триггер является универсальным. На его основе с помощью несложных коммутационных изменений можно получить RS-, Т- и D-триггеры.

При подаче тактовых сигналов на С- вход и попеременной подаче информационных сигналов на J- и K -входы триггер работает как двухступенчатый Т-триггер. При подаче информационного сигнала на J- вход и одновременно через инвертор на К- вход триггер превращается в D-триггер.

Запоминающие устройства

Запоминающие устройства предназначены для записи, хранения и считывания двоичной информации. В состав запоминающего устройства (ЗУ) входят: матрица-накопитель и функциональные узлы, необходимые для управления матрицей-накопителем, усиления сигналов при записи и считывании, обеспечения режима синхронизации. Все эти элементы расположены на одном полупроводниковом кристалле.

На рис. 8.41 показана структура ЗУ, в которой матрица-накопитель состоит из 16 элементов памяти (ЭП), объединенных в 4 строки и 4 столбца. ЭП, расположенные в одной строке, образуют ячейку памяти (ЯП), способную запомнить четырехразрядное машинное слово, то есть 4 бита информации. Эти ЭП объединены адресными шинами Х0...Х3. Элементы, расположенные в одном столбце, объединены разрядными шинами Y0...Y3. В режиме записи информации разрядные шины подключаются к усилителям записи, и на них подается комбинация нулей и единиц, а на одну из адресных шин от дешифратора адреса поступает управляющий сигнал, в результате входная комбинация нулей и единиц оказывается записанной в 4 элемента памяти. В режиме хранения разрядные шины отключаются от усилителей. В режиме считывания разрядные шины подключаются к усилителям считывания, и происходит считывание ранее записанной информации.

Запоминающие устройства делятся на две группы: постоянные запоминающие устройства (ПЗУ) и оперативные запоминающие устройства (ОЗУ).

ПЗУ (по-английски ROM — Read Only Memory, что переводится как «память только для считывания») используются только для считывания ранее записанной информации. В ПЗУ обычно хранятся стандартные программы, необходимые для выполнения арифметических или логических операций. Важным свойством ПЗУ является сохраняемость информации при выключении питания. По способу записи информации ПЗУ подразделяются на масочные (ПЗУМ), программируемые (ППЗУ) и репрограммируемые (РПЗУ).

ОЗУ (по-английски RAM — Random Access Memory, что переводится как «память с произвольной выборкой») предназначены для быстрого попеременного ввода и вывода информации. В ОЗУ обычно хранятся промежуточные данные в процессе выполнения арифметических или логических операций.

Элементы памяти ОЗУ подразделяются на статические и динамические. ЭП статического типа хранят информацию сколь угодно долго, пока включен источник питания. В ЭП динамического типа информация хранится ограниченное время; в этих элементах предусматривается восстановление (регенерация) информации.

Масочные ПЗУ

В качестве элементов памяти масочных ПЗУ используются диодные или транзисторные структуры, включаемые на пересечениях адресных и разрядных шин. На рис. 8.42 представлена схема ПЗУМ, содержащая в качестве элементов памяти полупроводниковые диоды. В процессе изготовления таких ИМС формируется матрица размером 4x4, содержащая 16 диодов (в реальных схемах их число составляет 64, 128, 256, 512 и т. д.). На заключительном этапе изготовления ИМС с помощью маски, изготовленной методом фотолитографии, осуществляется подключение диодов к адресным и разрядным шинам. Наличие диода между адресной и разрядной шиной соответствует логической единице, отсутствие — логическому нулю. При подаче на какую-либо адресную шину X положительного напряжения шина X через диод соединяется с соответствующей разрядной шиной. Например, при подаче напряжения на шину Х1 считывается четырехразрядное число 0001, а при подаче напряжения на шину Х3 — число 0011. Напряжение на адресные шины поступает от дешифратора адреса.

Программируемые ПЗУ

Отличие программируемых ПЗУ от масочных состоит в том, что программирование осуществляется не производителем в процессе изготовления ИМС, а пользователем перед началом эксплуатации. В программируемых ПЗУ диоды (или биполярные транзисторы) подключаются к разрядным шинам через плавкие перемычки. При программировании эти перемычки пережигают путем пропускания импульсов тока. В результате образуется структура, аналогичная масочному ПЗУ.

Репрограммируемые ПЗУ

Репрограммируемые ПЗУ допускают многократное перепрограммирование, то есть многократное стирание ранее записанной информации и многократную запись новой. В качестве элемента памяти в РПЗУ используют МДП-транзистор с плавающим затвором, эквивалентная схема которого показана на рис. 8.43, а. Такие транзисторы помимо обычного управляющего затвора, соединенного с адресной шиной, содержат второй затвор, размещенный между управляющим затвором и подложкой (рис. 8.43, б). Этот дополнительный затвор не имеет внешних выводов и поэтому называется плавающим. Оба затвора выполнены из сильнолегированного поликремния и отделены один от другого слоем SiO2 толщиной 0,02-0,04 мкм.

Толщина оксидного слоя между плавающим затвором и подложкой имеет такую же величину. Длина канала составляет 1-2 мкм. Площадь, занимаемая элементом на подложке, составляет 6-10 литографических квадратов, что позволяет создавать накопители информации с емкостью более 1 Мбит.

В режиме программирования логической единицы на разрядную шину подается высокий потенциал U1 (около 10 В), а на адресную шину — потенциал Ux > U1. При этих условиях между истоком и стоком существует канал, в котором электроны разгоняются до скоростей, при которых становится возможным лавинное размножение электронов, в результате чего появляются высокоэнергетические (горячие) электроны, способные преодолеть потенциальный барьер на границе раздела кремний-оксид кремния. Поскольку потенциал затвора выше потенциала канала, то существует поперечное (вертикальное) электрическое поле, в котором электроны, попавшие в слой оксида кремния, перемещаются в сторону плавающего затвора, в результате плавающий затвор приобретает отрицательный заряд.

В режиме программирования логического нуля на разрядную шину подается низкий потенциал U0. В этом случае продольное (горизонтальное) электрическое поле в канале отсутствует, и накопления заряда в плавающем затворе не происходит.

В режиме хранения логической единицы плавающий затвор имеет отрицательный заряд, а в режиме хранения логического нуля заряд равен нулю. Поскольку плавающий затвор со всех сторон окружен диэлектриком, то заряд затвора сохраняется длительное время (несколько лет). Наличие или отсутствие заряда затвора влияет на величину порогового напряжения МДП-транзистора. Если отрицательный заряд отсутствует, то пороговое напряжение  невелико (порядка 1-2 В). Если же заряд существует, то пороговое напряжение

невелико (порядка 1-2 В). Если же заряд существует, то пороговое напряжение  возрастает (порядка 8 В).

возрастает (порядка 8 В).

В режиме считывания разрядная шииа Y подключается к усилителю считывания, а на шину X подается напряжение Ux лежащее в пределе между  и

и  (обычно 5 В). Если в ЭП хранится логическая единица, то канал в МДП-транзисторе не индуцируется, и шина Y оказывается изолированной от подложки. Если в ЭП хранится логический ноль, то канал индуцируется, и шина Y соединяется с подложкой.

(обычно 5 В). Если в ЭП хранится логическая единица, то канал в МДП-транзисторе не индуцируется, и шина Y оказывается изолированной от подложки. Если в ЭП хранится логический ноль, то канал индуцируется, и шина Y соединяется с подложкой.

Стирание (удаление электронов из плавающего затвора) осуществляется путем облучения кристалла ультрафиолетовыми лучами, под действием которых электроны приобретают энергию, достаточную для преодоления потенциального барьера на границе между кремнием и оксидом кремния. Далее они дрейфуют в подложку, потенциал которой должен быть выше потенциала управляющего затвора. Корпуса ИМС, содержащие ЭП рассмотренного типа, имеют специальное окно со вставленным кварцевым стеклом. В каждом цикле перепрограммирования происходят некоторые изменения в структуре кристаллической решетки полупроводника, образуются дополнительные поверхностные заряды, происходит захват электронов ловушками в слое оксида кремния и т. д. Все это приводит к изменению пороговых напряжений. Поэтому максимально допустимое число циклов перепрограммирования обычно не превышает 103.

Рассмотренный способ хранения информации нельзя признать совершенным. Процесс записи протекает сравнительно медленно (около 1 мс) и связан с большими энергетическими затратами по преодолению потенциального барьера между кремнием и оксидом кремния. Более совершенным является способ проникновения электронов в плавающий затвор путем туннелирования из подложки через диэлектрик.

На рис. 8.44 приведена энергетическая диаграмма системы подложка—диэлектрик—плавающий затвор, иллюстрирующая механизм туннельных переходов. При ширине запрещенной зоны кремния, равной 1,1 эВ, и ширине запрещенной зоны оксида кремния, равной примерно 9 эВ, на границе Si— SiO2 возникает энергетический барьер высотой около 4 эВ. Преодолеть такой барьер может незначительная часть «горячих» электронов. Если же уменьшить толщину диэлектрика до 0,01 мкм и довести величину напряженности электрического поля в нем до 106-107 В/см, то электроны смогут совершить туннельные переходы из зоны проводимости подложки в зону проводимости диэлектрика и оттуда в зону проводимости поликремниевого затвора. Поскольку плавающий затвор со всех сторон изолирован, то в нем произойдет накопление отрицательного заряда. Туннелирование электронов через диэлектрик — процесс двухсторонний, его можно использовать как для заряда, так и для разряда плавающего затвора.

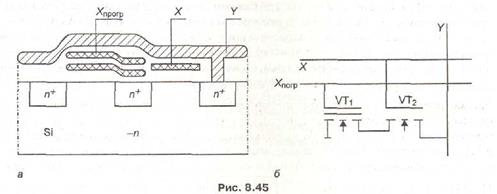

Структура ЭП, программируемого с помощью туннельного эффекта, представлена на рис. 8.45, а, эквивалентная схема — на рис. 8.45, 6. Левая часть структуры образует бистабильный МДП-транзистор с плавающим затвором, перекрывающим область стока со слоем туннельно-тонкого диоксида толщиной порядка 10 нм, в котором происходит туннелирование электронов. Правая часть структуры представляет собой обычный МДП-транзистор, предназначенный для подключения стока бистабильного транзистора к разрядной шине.

В режиме программирования на программирующую шину Хпрогр подается напряжение порядка 20 В, а на адресную шину — напряжение, превышающее пороговое, в результате чего разрядная шина через транзистор VT2 подключается к стоку транзистора VT1. При программировании логической единицы на разрядной шине устанавливается нулевой потенциал. В этом случае в туннельно-тонком диоксиде происходит туннелирование электронов в плавающий затвор. При программировании логического нуля на разрядной шине устанавливается высокий потенциал, и туннелирования не происходит. В итоге, как и в предыдущем случае, при программировании логической единицы плавающий затвор приобретает отрицательный заряд, а при программировании логического нуля заряд затвора равен нулю.

При считывании информации подается отпирающее напряжение на шину X, и транзистор VT1 подключается к разрядной шине через транзистор VT2. Для стирания информации шину Хпрогр соединяют с подложкой, а на сток транзистора VT1 подают высокое напряжение, при этом происходит туннелирование электронов из плавающего затвора в сток.

Рассмотренный ЭП обладает рядом достоинств по сравнению с элементами, в которых происходит накопление «горячих» электронов, например, имеется возможность поэлементного быстрого электрического стирания информации, кроме того, число циклов перепрограммирования достигает 105. Однако ЭП с программированием с помощью туннельного эффекта занимают сравнительно большую площадь (порядка 30-90 литографических квадратов).