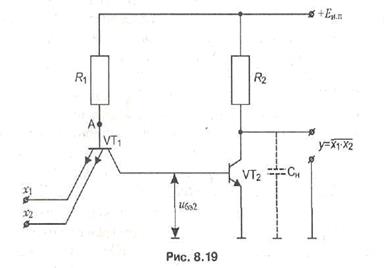

В базовом элементе ТТЛ (рис. 8.19) функции диодов VD1 и VD2 выполняют эмиттеры многоэмиттерного транзистора, а роль диодов VD3 и VD4 — его коллекторный переход. Следовательно, схема ТТЛ выполняет ту же логическую операцию, что и схема ДТЛ, то есть И—НЕ. Действительно, если на входе х1 или х2 действует сигнал низкого уровня  (логический нуль), то в цепи протекает ток от источника питания Еи.п через резистор R1 и соответствующий открытый эмиттерный переход. Потенциал базы транзистора VT1 становится равным примерно 0,7 В. Этот потенциал распределяется примерно поровну между коллекторным переходом транзистора VT1 и эмиттерным переходом транзистора VT2. Поэтому напряжение uбэ2 недостаточно для отпирания транзистора VT2, и на выходе схемы устанавливается высокий уровень напряжения

(логический нуль), то в цепи протекает ток от источника питания Еи.п через резистор R1 и соответствующий открытый эмиттерный переход. Потенциал базы транзистора VT1 становится равным примерно 0,7 В. Этот потенциал распределяется примерно поровну между коллекторным переходом транзистора VT1 и эмиттерным переходом транзистора VT2. Поэтому напряжение uбэ2 недостаточно для отпирания транзистора VT2, и на выходе схемы устанавливается высокий уровень напряжения  (логическая единица). Если на входах х1 и х2 действует высокий уровень сигнала

(логическая единица). Если на входах х1 и х2 действует высокий уровень сигнала  (логическая единица), то эмиттерные переходы транзистора VT1 заперты, ток течет от источника Еи.п через резистор R1 коллекторный переход VT1 и эмиттерный переход VT2. Потенциал базы транзистора VT2 становится равным

(логическая единица), то эмиттерные переходы транзистора VT1 заперты, ток течет от источника Еи.п через резистор R1 коллекторный переход VT1 и эмиттерный переход VT2. Потенциал базы транзистора VT2 становится равным  , а потенциал

, а потенциал  . Транзистор VT2 отпирается, и на выходе схемы устанавливается низкий уровень напряжения

. Транзистор VT2 отпирается, и на выходе схемы устанавливается низкий уровень напряжения  .

.

Схема ТТЛ, сохраняя все достоинства схемы ДТЛ, имеет существенный выигрыш по площади. Поэтому эта схема в настоящее время практически вытеснила схемы ДТЛ и получила очень широкое распространение. Однако в рассмотренном варианте схема ТТЛ несмотря на простую технологию из-за малой нагрузочной способности и низкого быстродействия почти не применяется. Действительно, при подключении к выходу схемы нескольких нагрузок в виде аналогичных схем вырастает нагрузочная емкость Сн, а так как резистор R2 имеет достаточно большую величину, то вырастает постоянная времени заряда емкости и быстродействие схемы падает. Для устранения этого недостатка в схемах ТТЛ вместо простого инвертора используют сложный инвертор (рис. 8.20).

Транзистор VT2 в этой схеме выполняет функцию «фазорасщепителя». Рассмотрим работу инвертора. Пусть на входе инвертора (на базе транзистора VT2) действует низкий уровень напряжения U0 (логический нуль). Транзистор VT2 закрыт, потенциал точки А высокий, а точки В — низкий, следовательно, транзистор VT3 закрыт, a VT4 открыт. Нагрузочная емкость Cн быстро заряжается от источника Еи.п через резистор R2, открытый эмиттерный переход транзистора VT4 и диод VD1. На выходе схемы устанавливается высокий уровень напряжения  (логическая единица). Резистор R4 предназначен для ограничения тока в последовательной цепочке VT4-VD1-VT3. Дело в том, что в моменты переключения схемы из одного состояния в другое оба транзистора, VT3 и VT4, открыты (один из них открывается, а другой не успевает закрыться), и чтобы предотвратить замыкание источника Eи.п на «землю», ставится ограничительный резистор R4.

(логическая единица). Резистор R4 предназначен для ограничения тока в последовательной цепочке VT4-VD1-VT3. Дело в том, что в моменты переключения схемы из одного состояния в другое оба транзистора, VT3 и VT4, открыты (один из них открывается, а другой не успевает закрыться), и чтобы предотвратить замыкание источника Eи.п на «землю», ставится ограничительный резистор R4.

Если на входе инвертора устанавливается высокий уровень напряжения U1 (логическая единица), то транзистор VT2 открыт, VT4 закрыт и VT3 открыт. Емкость Си разряжается через открытый транзистор VT3, и на выходе схемы устанавливается низкий уровень напряжения  (логический нуль). Диод VD1 обеспечивает надежное запирание транзистора VT4 при открытом транзисторе VT3. Благодаря тому что заряд и разряд паразитной емкости Сн проходит через транзисторы VT3 и VT4 с низким сопротивлением в открытом состоянии, схема ТТЛ со сложным инвертором обладает высоким быстродействием. Среднее время задержки распространения сигнала в этой схеме составляет около 10 нс. Более высоким быстродействием обладает схема ТТЛШ, в которой вместо обычных биполярных транзисторов применены транзисторы с барьером Шотки. В этом случае

(логический нуль). Диод VD1 обеспечивает надежное запирание транзистора VT4 при открытом транзисторе VT3. Благодаря тому что заряд и разряд паразитной емкости Сн проходит через транзисторы VT3 и VT4 с низким сопротивлением в открытом состоянии, схема ТТЛ со сложным инвертором обладает высоким быстродействием. Среднее время задержки распространения сигнала в этой схеме составляет около 10 нс. Более высоким быстродействием обладает схема ТТЛШ, в которой вместо обычных биполярных транзисторов применены транзисторы с барьером Шотки. В этом случае  .

.

Для расширения функциональных возможностей ТТЛ-логики промышленность выпускает логические элементы, выполняющие три функции: И/ИЛИ—НЕ. Схема такого комбинированного логического элемента представлена на рис. 8.21, а, а на рис. 8.21, б — его функциональная блок-схема, которая содержит два двух-входовых элемента И на транзисторах VT1 и VT4, а также двухвходовый элемент ИЛИ—НЕ на транзисторах VT2 и VT3, выходной каскад на транзисторах VT5 и VT6 аналогичен рассмотренному выше. На рис. 8.21, в приведено схематическое изображение таких элементов, приводимых в справочниках.