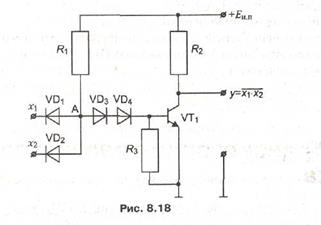

Более совершенным по сравнению с логическим элементом ТЛНС является логический элемент диодно-транзисторной логики (ДТЛ), схема которого показана на рис. 8.18.

В этой схеме можно выделить две последовательно включенные функциональные части: в первой входные сигналы х1 и х2 подаются на диодный элемент (диоды VD1 и VD2 и резистор R1), выполняющий операцию И; вторая часть, выполненная на транзисторе VT1 представляет собой инвертор. Таким образом, в схеме раздельно выполняются логические операции И и НЕ, следовательно, схема реализует логическую операцию 2И—НЕ (число 2 означает количество входов ЛЭ). Диоды VD3 и VD4 играют роль элемента связи между двумя частями схемы и повышают ее помехоустойчивость.

Если на один из входов х1 или х2 подан сигнал  , то один из диодов открыт и в схеме течет ток от источника

, то один из диодов открыт и в схеме течет ток от источника  через резистор R1 и открытый диод. При этом в точке А установится потенциал

через резистор R1 и открытый диод. При этом в точке А установится потенциал  = 0,7 В, недостаточный для отпирания двух последовательно включенных диодов VD3 и VD4. В результате транзистор VT1 будет закрыт и на выходе схемы установится напряжение

= 0,7 В, недостаточный для отпирания двух последовательно включенных диодов VD3 и VD4. В результате транзистор VT1 будет закрыт и на выходе схемы установится напряжение  соответствующее логической единице. В таком состоянии схема будет оставаться до тех пор, пока на оба входа, х1 и х2 не будет подан высокий уровень сигнала

соответствующее логической единице. В таком состоянии схема будет оставаться до тех пор, пока на оба входа, х1 и х2 не будет подан высокий уровень сигнала  (логическая единица). В этом случае диоды VD1 и VD2 закрываются, потенциал точки А увеличивается, став достаточным для открывания диодов VD3 и VD4, и в цепи течет ток от источника

(логическая единица). В этом случае диоды VD1 и VD2 закрываются, потенциал точки А увеличивается, став достаточным для открывания диодов VD3 и VD4, и в цепи течет ток от источника  через резистор R1 диоды VD3 и VD4 в базу транзистора VT1. В результате транзистор VT1, открывается, и на выходе схемы устанавливается низкий уровень напряжения

через резистор R1 диоды VD3 и VD4 в базу транзистора VT1. В результате транзистор VT1, открывается, и на выходе схемы устанавливается низкий уровень напряжения  (логический нуль), следовательно, в схеме ДТЛ выполняется операция И—НЕ. Резистор R3 служит в данной схеме для того, чтобы создать цепь рассасывания накопленного в базе транзистора VT1 заряда (при переключении VT1 из открытого состояния в закрытое). В некоторых случаях резистор R3 соединяют не с землей, а с источником отрицательного напряжения

(логический нуль), следовательно, в схеме ДТЛ выполняется операция И—НЕ. Резистор R3 служит в данной схеме для того, чтобы создать цепь рассасывания накопленного в базе транзистора VT1 заряда (при переключении VT1 из открытого состояния в закрытое). В некоторых случаях резистор R3 соединяют не с землей, а с источником отрицательного напряжения  , чтобы обеспечить более быстрое рассасывание базового заряда и уменьшить время задержки сигнала.

, чтобы обеспечить более быстрое рассасывание базового заряда и уменьшить время задержки сигнала.

Логические элементы ДТЛ обладают высоким быстродействием и большим логическим перепадом  . Чаще всего они реализуются в виде гибридных ИМС. Что касается полупроводниковых ИМС, то схема ДТЛ обладает существенным недостатком — большим количеством диодов, а каждый диод—это, в сущности, транзистор в диодном включении. Каждый такой транзистор нуждается в изолирующем кармане, и поэтому площадь, занимаемая схемой на подложке, оказывается очень большой. Отсюда появилась идея заменить совокупность логических диодов (VD1 и VD2) и диодов VD3 и VD4 одним многоэмиттерным транзистором, выполненным в одном изолирующем кармане. Таким образом был осуществлен переход к одному из самых распространенных семейств логических ИМС — схемам транзисторно-транзисторной логики (ТТЛ).

. Чаще всего они реализуются в виде гибридных ИМС. Что касается полупроводниковых ИМС, то схема ДТЛ обладает существенным недостатком — большим количеством диодов, а каждый диод—это, в сущности, транзистор в диодном включении. Каждый такой транзистор нуждается в изолирующем кармане, и поэтому площадь, занимаемая схемой на подложке, оказывается очень большой. Отсюда появилась идея заменить совокупность логических диодов (VD1 и VD2) и диодов VD3 и VD4 одним многоэмиттерным транзистором, выполненным в одном изолирующем кармане. Таким образом был осуществлен переход к одному из самых распространенных семейств логических ИМС — схемам транзисторно-транзисторной логики (ТТЛ).