Асинхронный HDLC-протокол. Асинхронный HDLC - это протокол, использующий для передачи HDLC-кадров по каналу связи технологию UART-кадров. Данный протокол используется как физический уровень для протоколов РРР (point-to-point). Так же как и в других протоколах, СРМ, работая с асинхронным HDLC-протоколом (AHDLC-контролллер), выполняет формирование кадров и передачу их по сети с минимальным вмешательством центрального процессора. Работа AHDLC-контроллера похожа на работу классического HDLC-контроллера.

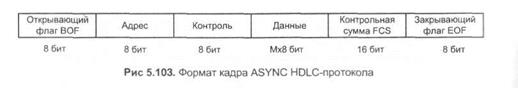

ASYNC HDLC-контроллер передает HDLC-кадры в пакетах UART-протокола. UART-пакет служит средством передачи данных HDLC-кадра по асинхронной сети. При формировании кадра данных для непосредственной передачи по сети контроллер использует следующий формат: 1 старт-бит, 8 бит данных, 1 стоп-бит, битов контроля четности нет.

.

.

Для обеспечения указанного выше формата UART-кадра в регистре режима AHDLC-npo-токола PSMR (рис. 5.102) биты CHLN1 и CHLNO должны быть установлены в «1». Для других протоколов эти биты определяют число битов в передаваемом символе данных.

Бит FLC в регистре PSMR определяет тип контроля при передаче данных. Если бит FLC = 0, то идет обыкновенная передача. Если бит FLC = 1, то производится асинхронный контроль передачи. При этом, если сигнал  станет равным единице, то передача останавливается после завершения передачи текущего символа. Если сигнал

станет равным единице, то передача останавливается после завершения передачи текущего символа. Если сигнал  = 1 после середины передачи текущего символа, то передача может остановиться после передачи следующего символа. Пока

= 1 после середины передачи текущего символа, то передача может остановиться после передачи следующего символа. Пока  = 1, могут передаваться символы IDLE. Когда сигнал

= 1, могут передаваться символы IDLE. Когда сигнал  восстановится (

восстановится ( = 0), передача продолжится с того места, где она остановилась. Таким образом, при передаче регистрируется всего одна ошибка -это потеря сигнала

= 0), передача продолжится с того места, где она остановилась. Таким образом, при передаче регистрируется всего одна ошибка -это потеря сигнала  . При этом передача прерывается, буфер закрывается, устанавливается признак ошибки СТ = 1 в слове состояния буфера BD и устанавливается бит ТХЕ прерывания в регистре событий SCCE. После получения команды RESTART TRANSMIT передача возобновляется из следующего TxBD.

. При этом передача прерывается, буфер закрывается, устанавливается признак ошибки СТ = 1 в слове состояния буфера BD и устанавливается бит ТХЕ прерывания в регистре событий SCCE. После получения команды RESTART TRANSMIT передача возобновляется из следующего TxBD.

Отличия между протоколами HDLC и ASYNC HDLC перечислены ниже.

• Для AHDLC-контроллера нет ограничения на максимальную длину принимаемого кад-

ра, так как принимаются все символы между открывающим и закрывающим флагами. Таким образом, не существует механизма ограничения числа байтов принимаемых в буфер данных, и все данные будут записаны в память даже из кадра с длиной, превышающей максимальную.

• Если во время приема кадра произошла одна из ошибок приема, то принятый кадр

игнорируется и не записывается в память. Таким образом, счетчик принятых байтов

регистрирует только кадры, записанные в память.

• Команда GRACEFUL STOP TRANSMIT не используется.

• Счетчики ошибок контрольной суммы CRCEC и ошибок принятия ABORT-последова-

тельностей в ASYNC HDLC-контроллере не используются.

Особенности программирования регистра GSMR для ASYNC HDLC-контроллера перечислены ниже.

• Бит RFW:= 1. Для AHDLC-контроллера устанавливается размер буферов FIFO, рав-

ный 8 байтам для канала SCC1 и 4 байтам для других SCC-каналов. Размер ячейки

буфера равен 8 битам.

• В битах TDCR и RDCR должен быть задан коэффициент внутреннего увеличения такто-

вой частоты приемника и передатчика. Для AHDLC-контроллера допустимые значения

коэффициента 8х, 16х и 32х. Но если используется протокол IrLAP, то должен быть выб-

ран коэффициент 16х (биты TDCR = RDCR:= 10).

При работе с ASYNC HDLC-протоколом в регистр синхронизации DSR должен быть записан код 0х7Е7Е.

Передача символов. При включении в работу передатчика AHDLC-контроллер проверяет бит готовности R первого буфера BD-дескриптора. Если бит R = 1, то контроллер читает данные из памяти по SDMA-каналам в буфер FIFO канала передачи и начинает передавать их в канал. Перед началом передачи данных из нового кадра контроллер добавляет к кадру открывающий флаг. Набор символов, которые могут быть переданы по AHDLC-каналу, ограничен рекомендациями RFC 1549.

|

Формат поля, флаг задается пользователем в ячейке ВОР памяти параметров. Рекомендованные значения: для протокола РРР - 0х7Е, для протокола IRLAP (infra-red link access protocol) - 0xC0.

Когда контроллер обнаружит последний буфер BD кадра данных (буфер в слове состояния которого будет установлен бит L = 1), то он подсчитывает контрольную сумму кадра CRC и передает ее в канал, а затем передает закрывающий флаг. Формат закрывающего флага задается пользователем в ячейке EOF памяти параметров. Рекомендованное значение для протокола РРР - 0х7Е, для протокола IRLAP - 0хС1.

Далее, если сброшен бит продолжения СМ = 0 в слове состояния последнего буфера BD, то AHDLC-контроллер устанавливает в слове состояния последнего буфера кадра биты статуса передачи кадра и сбрасывает бит готовности буфера к передаче R:= 0.

Если в слове состояния BD был установлен бит I = 1, то контроллер генерирует ТхВ-прерывание через регистр событий. Таким образом, прерывание может регистрироваться после передачи буфера, группы буферов или после окончания передачи всего кадра.

Если в слове состояния буферного дескриптора установлен бит продолжения СМ = 1, то после передачи данных из этого буфера будут установлены биты статуса передачи, но бит готовности кадра к передаче сбрасываться не будет, т. е. R = 1. После передачи буфера с СМ = 1 контроллер переходит к передаче следующего буфера BD. Если он еще не готов, т. е. бит R = 0, то контроллер будет ожидать его готовности. Формат кадра ASYNC HDLC-протокола представлен на рис. 5.103.

Открывающий и закрывающий флаги вставляются при передаче данных и удаляются контроллером при приеме. Контроллер принимает кадры только с одним разделяющим флагом между кадрами. Если между кадрами передается несколько символов флага, то контроллер будет их игнорировать. В ячейке NOF памяти параметров хранится число N, которое определяет, сколько N+1 открывающих флагов будет передано перед кадром.

Поле адреса может быть заполнено, только если оно получено при передаче из буфера данных, у которого в слове состояния буферного дескриптора установлен бит А = 1. RISC-контроллер не занимается в своей микропрограмме вопросами вставки, распознавания и контроля адресов. Все эти функции должны быть возложены на центральный процессор.

То же самое относится и к полю контроля. RISC-контроллер не выполняет функции обработки этого поля. Он только заполняет его при передаче данных из буфера, если в слове состояния буферного дескриптора указано, что буфер содержит контрольный символ (бит С = 1). Всей обработкой данных из этого поля должен заниматься центральный процессор.

При передаче контрольная сумма кадра FCS (Frame Control Sequence) автоматически добавляется к кадру данных перед закрывающим флагом. Контрольная сумма вычисляется над содержимым первоначального кадра до добавления в него символов «прозрачности», старт- и стоп-битов или символов флагов. Для формирования контрольной суммы контроллер использует 16-битный образующий полином циклического кода. В ячейке C_MASK памяти параметров хранится константа этого полинома 0x0000F0B8, а в ячейке C_PRES - начальное значение счетчика контрольной суммы 0x0000FFFF.

При передаче данных AHDLC-контроллер постоянно контролирует, что за байты данных он передает в сеть. Если для байта данных выполняется одно из перечисленных ниже условий, то включается алгоритм обеспечения «прозрачности» данных и вместо одного исходного байта передается двухбайтовая последовательность. Первый байт - это специальный символ control-escape, формат которого задан в ячейке ESC памяти параметров (для протоколов РРР и IrLAP рекомендуется значение 0x7D). Второй байт - это исходный байт, над которым выполнена операция «исключающее ИЛИ» XOR с константой 0x20. Условия включения алгоритма кодировки «прозрачности» при передаче байта данных:

1) если этот байт - флаг (формат Ох7Е для протокола РРР и 0хС0/0С1 - для IrLAP);

2) если этот байт — контрольный символ control-escape — 0x7D;

3) если этот байт имеет значение между 0x00 и 0x1 F и соответствующий бит установ-

ки в таблице Тх контрольных символов. Эта кодировка выполняется только для протоко-

ла РРР.

В ячейке TXCTL_TBL памяти параметров хранится таблица контрольных символов при передаче, а в ячейке RXCTL_TBL - таблица контрольных символов при приеме данных. Эти таблицы используются только для протокола РРР. Если используется протокол IrLAP, эти ячейки должны быть инициализированы в «0». Каждая из этих ячеек представляет собой таблицу из 32 бит. Бит номер 0 соответствует символу 0x00, бит номер 1 -0x01, бит номер 2 - 0x02 и т. д. Бит номер 31 соответствует символу 0x1 F. Если в этих таблицах в бите i установлена «1», то символ, соответствующий этому биту, рассматривается как контрольный.

Распределение памяти параметров ASYNC HDLC-протокола приведено в табл. 5.66.

Таблица 5.66 Память параметров ASYNC HDLC-протокола

| Адрес | Название | Размер, бит | Описание |

| SCC base +34 | C_MASK | Константа полинома CRC | |

| SCC base+38 | C_PRES | Начальные значения CRC | |

| SCC base+3C | BOF | Открывающий флаг | |

| SCC base+3E | EOF | Закрывающий флаг | |

| SCC base+40 | ESC | Контрольный ESC-символ | |

| SCC base+42 | - | Зарезервировано | |

| SCC base+44 | - | Зарезервировано | |

| SCC base+46 | ZERO | Инициализация «0» | |

| SCC base+48 | - | Зарезервировано | |

| SCC base+4A | RFTHR | Число принятых кадров до прерывания | |

| SCC base+4C | - | Зарезервировано | |

| SCC base+4E | - | Зарезервировано | |

| SCC base+50 | TXCTL_TBL | Таблица контрольных символов Тх | |

| SCC base+54 | RXCTL_TBL | Таблица контрольных символов Rx | |

| SCC base+58 | NOF | Число открывающих флагов | |

| SCC base+5A | - | Зарезервировано | |

| Примечание. Все переменные в таблице инициализируются пользователем. Ячейка ZERO должна быть проинициализирована «0». Зарезервированные ячейки используются контроллером для временного хранения данных.. |

Пользователь может остановить передачу данных из буферов, передав AHDLC-контроллеру команду STOP TRANSMIT. Эта команда используется, если необходимо изменить порядок передачи данных из буферов или если обнаружена ошибка передачи в канале. После получения данной команды AHDLC-контроллер начинает передавать в сеть ASYNC HDLC ABORT-последовательность, которая состоит из ESCAPE-символа (Ox7D) и закрывающего флага. После передачи такой ABORT-последовательности контроллер передает в сеть символы IDLE, пока не получит команду возобновления передачи RESTART TRANSMIT. Форматы ABORT-последовательности для протоколов РРР и IrLAP приведены в табл. 5.67.

Таблица 5.67

Формат ABORT-последовательности

| Протокол | Формат |

| РРР IrLAP | 0x7D,0х7Е 0x7D, 0хС1 |

При получении команды STOP TRANSMIT контроллер не переходит к передаче из следующего TxBD и текущим остается буфер, передачу которого прервали. Также останавливается передача и данных, которые уже находились в FIFO. В этом отличие ASYNC HDLC-протокола от других протоколов, в которых содержимое FIFO передается в сеть перед остановкой. Пользователь всегда может прочитать в ячейке TBPTR протокол-независимой части памяти параметров SCC-канала 0 номер, передача из которого прервалась.

Команда INIT TX PARAMETERS используется для инициализации параметров в памяти параметров передатчика контроллера.

Прием данных. После включения в работу (бит ENR = 1 в регистре GSMR) приемник ожидает появления кадра данных на линии RXD, анализируя присутствие на линии символа открывающего флага кадра. Обнаружив начало нового HDLC-кадра данных, контроллер обращается к следующему буферному дескриптору в таблице и проверяет его готовность к приему, т. е. проверяет бит незанятости буфера Е = 1 в слове состояния дескриптора. Если буфер не занят, то контроллер начинает записывать в него данные. Когда буфер будет заполнен, контроллер сбросит бит Е:= 0. Если длина текущего кадра данных превышает размер буфера (максимальный размер буфера указан в ячейке переменной MRBLR), то производится опрос готовности к приему данных следующего буфера в таблице, и, если он свободен, прием текущего кадра будет продолжен в новый буфер.

Во время приема кадра ASYNC HDLC-контроллер автоматически контролирует принимаемый символ, декодируя его в соответствии с заданным алгоритмом.

1) Если код принятого символа находится между 0x00 и 0x1 F и в таблице ячейки

RXCTL_TBL памяти параметров для этого символа в соответствующем бите установле

на «1», то принятый символ считается служебным и отбрасывается. Если соответствую

щий символу бит равен 0, то символ принимается в нормальном режиме и записывается

в память.

2) Если принят символ control-escape 0x7D, то этот символ отбрасывается, а над сле

дующим принятым символом выполняется операция «исключающее ИЛИ» с константой

0x20, прежде чем этот символ будет участвовать в подсчете контрольной суммы и будет

записан в память.

3) Если принята пара символов 0x70, 0x70, то первый символ будет отброшен,

а второй - декодирован с помощью операции XOR с константой 0x20, а затем записан

в память как код 0х5D.

4) Если принят символ закрывающего флага (0х7Е для протокола РРР или 0хС1 для

протокола IrLAP), то прием кадра данных будет закончен.

5)При приеме все символы IDLE автоматически удаляются.

После завершения приема кадра данных и удаления из него всех служебных «transparenb-символов, всех старт- и стоп-битов и всех символов флагов контроллер сравнивает подсчитанную с помощью 16-битного CRC CCITT-полинома контрольную сумму со значением, которое было получено в поле контрольной суммы принятого кадра. Далее контроллер записывает полученную контрольную сумму в буфер и закрывает буфер. В ячейку длины последнего буферного дескриптора контроллер заносит длину реально принятого кадра, устанавливает бит последнего буфера кадра L:= 1 в слове состояния последнего буфера, заполняет биты статуса принятого кадра и сбрасывает бит незанятости буфера Е:= 0, если только бит СМ = 0. Затем контроллер устанавливает бит RXF в регистре событий, уведомляя через маскируемое прерывание центральный процессор, что данные приняты и находятся в памяти. После завершения всех этих действий контроллер начинает поиск нового кадра данных.

Пользователь может управлять работой приемника ASYNC HDLC-контроллера, передавая ему команды: ENTER HUNT MODE, CLOSE RX BD, INIT RX PARAMETERS. После получения команды «поиск нового кадра» контроллер перейдет в нормальный режим работы при обнаружении в канале одного или более символов открывающего флага кадра.

При приеме AHDLC-контроллер регистрирует следующие типы ошибок (см. ниже).

• Ошибка переполнения overrun. Для временного хранения принятой информации каж

дый AHDLC-контроллер имеет внутренние буферы FIFO размером 8 байт для канала

SCC1 и по 4 байта для других SCC-каналов. Данные из FIFO по SDMA-каналам под

управлением RISC-контроллера начинают передаваться в соответствующие буферы

памяти как только будут получены первые 8 бит кадра. Если RISC-контроллер не ус

певает очищать ячейки FIFO для приема новой информации из сети и в момент прихо

да новой порции данных все ячейки FIFO окажутся занятыми, то возникает ошибка

переполнения буферов overrun. При этом контроллер будет вынужден записать но

вые данные поверх старых, что приведет к потере информации. Далее текущий буфер

закрывается, в его слове состояния устанавливается бит ошибки переполнения OV:=

1 и через регистр событий генерируется, если оно разрешено, RXF-прерывание к цен

тральному процессору. После этого контроллер начинает поиск следующего кадра в

канале связи.

• Ошибка потери CD-сигнала. Во время приема кадра данных контроллер постоянно

проверяет наличие сигнала на линии  . Если во время приема этот сигнал будет

. Если во время приема этот сигнал будет

потерян  = 1, то контроллер прекращает прием, закрывает текущий буфер, устанав

= 1, то контроллер прекращает прием, закрывает текущий буфер, устанав

ливает в слове состояния текущего BD бит потери сигнала  . CD:= 1 и генерирует,

. CD:= 1 и генерирует,

если разрешено, прерывание RXF через регистр событий. Эта ошибка имеет самый

высокий приоритет, и после ее обнаружения другие ошибки не проверяются, а прием

ник после установки сигнала cd = 0 переходит в режим «охоты» (поиска нового кадра).

• Прием ABORT-последовательности. Эта ошибка регистрируется ASYNC HDLC-кон-

троллером, когда он получит пару символов 0x70, Ох7Е. При возникновении этой ошибки

открытый буфер приема закрывается, в его слове состояния устанавливается бит

ошибки АВ:= 1 и генерируется, если разрешено, прерывание RXF через регистр собы

тий. При этом для прерванного кадра CRC-контроль не выполняется. Если ABORT-

последовательность была получена, когда не было приема и не было открытых буфе

ров, в этом случае следующий в таблице буфер приема открывается и тут же закрыва

ется с установленным битом ошибки АВ = 1 в его слове состояния.

• Ошибка контрольной суммы. Если при подсчете контрольной суммы была выявлена ошибка, то контроллер записывает принятую контрольную сумму в буфер, затемзакрывает буфер и устанавливает бит ошибки проверки CRC суммы CR:= 1 в слове состояния буферного дескриптора и бит RXF:= 1 в регистре событий, вызывая маскируемое прерывание центрального процессора. Далее контроллер переходит в режим поиска нового кадра данных.

• Ошибка приема BREAK-последовательности. Эту ошибку обнаруживает UART-при-емник при приеме break-символа, состоящего из одних нулевых битов. При обнаружении этой ошибки открытый буфер приема закрывается, в его слове состояния устанавливается бит ошибки BRK:= 1 и генерирует, если разрешено, прерывание RXF через регистр событий. При этом для прерванного кадра CRC контроль не выполняется. Событие начала приема BREAK-последовательности регистрируется в бите BRKs регистра событий, а окончание BREAK-последовательности при получении первого единичного бита регистрируется в бите BRKe регистра событий.

Ошибки шума, характерные для UART-протокола в асинхронном режиме, не регистрируются. Появление ошибок такого типа должно обнаруживаться при проверке контрольной суммы.

UART-контроллер. Основные режимы работы UART-контроллера. Протокол UART (Universal Asynchronous Receiver Transmitter) используется для организации низкоскоростного канала связи между двумя станциями в сети. Термин асинхронный означает, что между станциями передаются только данные и не передаются тактовые сигналы. Протокол UART-это символьно-ориентированный протокол, т. е. минимальная единица передаваемой информации - это символ, и при передаче могут встречаться только символы строго определенного формата. Если принят символ, который не входит в установленный протоколом набор символов, то принятый пакет игнорируется и генерируется сообщение об ошибке. Ряд символов из установленного набора используются для управления передачей и не являются информационными. Наиболее часто асинхронный канал связи применяется для соединения терминалов и компьютеров или для подключения отладочного оборудования.

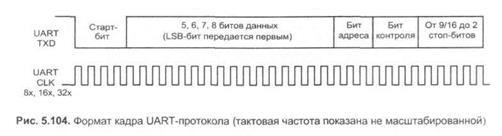

Генераторы тактовых сигналов приемника и передатчика работают независимо и асинхронно, но с близкими частотами синхронизации. Для связи двух станций достаточно всего двух линий (одна - для передачи данных TxD, другая - для приема данных RxD). Признаком начала кадра является появление старт-бита на линии данных. Приемник измеряет длину старт-бита, измеряет частоту передачи данных и внутри приемника увеличивает ее в 8, 16, 32 раза. Затем приемник опрашивает 8, 16, 32 раза значение бита на битовом интервале. Обычно используется увеличение частоты в 16 раз и опрос значения бита производится тоже 16 раз. Выбрав из проведенных 16 опросов три опроса в центре битового интервала (обычно это опросы 7, 8, 9), приемник анализирует их значение и за значение бита на битовом интервале выбирается значение по максимальному совпадению результатов этих трех опросов. Этот процесс определения значения бита при асинхронной передаче носит название oversampling.

Когда в UART сети нет передачи информации, передатчик посылает в канал последовательность битов «1», которая называется IDLE-последовательность. Так как старт-бит в кадре всегда равен 0, то приемник может всегда легко выделить начало кадра в канале связи. UART-протокол также использует последовательность из всех «0», которая называется BREAK-последовательностью и служит для прерывания передач в канале.

В современных сетях применяется и вариант синхронного UART-протокола. В этом протоколе полностью поддерживается формат кадра асинхронного UART-протокола, только при приеме не используется механизм oversampling и частота увеличивается в один раз, т.е. на каждый битовый интервал приходится один период тактовой частоты и один опрос значения бита. При работе в синхронном режиме тактовый сигнал может быть получен или от внутреннего генератора или от внешнего источника через внешние контакты (рис. 5.104).

|

Рис. 5.104. Формат кадра UART-протокола (тактовая частота показана не масштабированно

Любой SCC может быть запрограммирован на работу в UART-протоколе. В СРМ дополнительно SMC-каналы могут работать с упрощенной версией UART-протокола. Программирование каналов осуществляется в регистре GSMR в СРМ.

При работе UART-контроллер поддерживает режим multidrop для работы в сетях master/slave (рис. 5.105). Для обеспечения работы в сетях с многоточечной (multipoint) конфигурацией в состав кадра данных введен дополнительный «адресный» бит.

При работе с UART-протоколом,,но в режиме NMSI, каждый SCC-канал получает доступ к семи внешним контактам: передаваемые данные TXD, принимаемые данные RXD, синхронизация приема RCLK, синхронизация передачи TCLK, запрос передачи  , разрешение приема

, разрешение приема  и индикатор передачи

и индикатор передачи  . Другие модемные сигналы - DSR (готовность данных) и готовность терминала DTR - могут быть реализованы через контакты параллельных портов ввода/вывода. Таким образом, каналы, работающие с UART-протоколом, могут обмениваться данными с любыми внешними устройствами, поддерживающими стык RS-232.

. Другие модемные сигналы - DSR (готовность данных) и готовность терминала DTR - могут быть реализованы через контакты параллельных портов ввода/вывода. Таким образом, каналы, работающие с UART-протоколом, могут обмениваться данными с любыми внешними устройствами, поддерживающими стык RS-232.

Формат кадра. В любом режиме работы формат кадра UART-протокола состоит из следующих элементов:

• старт-бита «0»;

• битов данных (LSB-бит передается первым);

• необязательного адресного бита;

• необязательного бита контроля по четности/нечетности;

• одного или двух стоп-битов «1».

|

Пользователь может сам определить формат кадра, программируя регистр настройки UART-режима PSMR (рис. 5.106) в контроллере МРС860.

Рис. 5.105. Два способа включения UART-контроллера конфигурации multidrop

|

Биты CL определяют длину передаваемых данных (табл. 5.68).

Таблица 5.68 Длина передаваемых данных

| бит СL | Размер поля данных, бит |

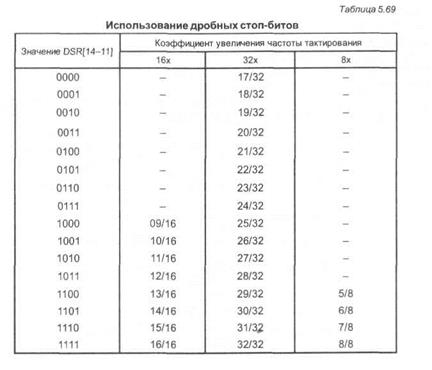

Биты SL определяют длину стоп-битов: 0 - один стоп-бит, 1 - два стоп-бита. Для того чтобы правильно распознать конец кадра, приемник должен получить хотя бы один стоп-бит. Стоп-бит - это логическая «1». Для асинхронного UART передатчик может быть запрограммирован на использование дробных стоп-битов. Дробным может быть только последний стоп-бит, т. е. если используются два стоп-бита, то первый передается в полном формате, а второй - в дробном. Символы IDLE всегда передаются с полными стоп-битами. При программировании дробных стоп-битов (табл. 5.69) используются биты FSB в регистре синхронизации SCC-канала DSR. Эти биты доступны пользователю и могут быть модифицированы в любое время.

|

Приемник UART может всегда принимать дробные стоп-биты. Следующий кадр может начинаться в любое время по истечении трех периодов увеличенной тактовой частоты после получения стоп-бита предыдущего кадра.

Для контроля правильности передачи данных по сети в состав кадра введен бит контроля. Пользователь может выбирать тип контроля по четности или по нечетности. Если выбран контроль по четности, то при передаче подсчитывается число «1» в поле данных, и если это число нечетное, то бит контроля устанавливается в «1», если число единиц в поле данных четное - бит контроля в кадре равен 0. Если выбран контроль по нечетности и число «1» в поле данных нечетное, то бит контроля равен 0, иначе - 1.

Бит контроля может быть удален из кадра, если пользователь установил бит PEN:= О в регистре настройки. Если бит PEN:= 1, то производится контроль и бит контроля включен в кадр данных. Тип контроля задают значения битов RPM при приеме и ТРМ при передаче (табл. 5.70).

Таблица 5.70

Тип контроля в сети

| Биты RTM или ТРМ | Тип контроля |

| Контроль по нечетности Бит контроля всегда равен 0 Контроль по четности Бит контроля всегда равен 1 |

Подсчет контрольной суммы всегда производится и на приемной и на передающей стороне канала.

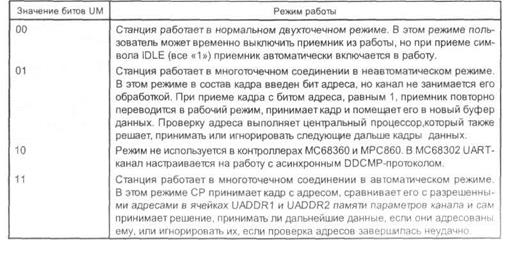

Для работы UART-контроллера в многоточечном соединении в состав кадра введен бит адреса. Если бит адреса в кадре равен 1, то в поле данных передается адрес узла, который требует соответствующей обработки. Если станция работает в двухточечном соединении, то бит адреса может быть исключен из кадра данных. Настройку UART-контроллера на определенный режим работы (табл. 5.71) производят биты UM в регистре настройки.

Таблица 5.71

Режимы работы UART контроллера

|

При работе с UART-контроллером пользователю предоставлена возможность временно остановить передачу и возобновить ее с точки останова через некоторое время. Остановкой передачи управляет бит FRZ. Если бит FRZ = 0, то передатчик работает в нормальном режиме. Если бит FRZ = 1, то передатчик передает все данные из FIFO канала и останавливает передачу. После сброса бита FRZ = 0 передача будет продолжена со следующего символа. Значение бита FRZ не влияет на работу приемника.

При работе с UART-протоколом пользователь может также управлять работой сигналов управления  и

и  и сигналами тактовой частоты.

и сигналами тактовой частоты.

При значении бита FLC = 1 производится контроль сигнала «разрешение передачи»  при передаче символов. Если во время передачи символа сигнал

при передаче символов. Если во время передачи символа сигнал  = 1, то передатчик передает текущий символ до конца и останавливает передачу. Генерируется ошибка «потеря

= 1, то передатчик передает текущий символ до конца и останавливает передачу. Генерируется ошибка «потеря  -сигнала», признак этой ошибки отмечается в бите CTS в слове состояния BD. Передача возобновляется после установки сигнала

-сигнала», признак этой ошибки отмечается в бите CTS в слове состояния BD. Передача возобновляется после установки сигнала  = 0. Если сигнал

= 0. Если сигнал  = 1, то возможна передача только IDLE-символов. Если бит FLC = 0, то UART-контроллер не анализирует состояние сигнала

= 1, то возможна передача только IDLE-символов. Если бит FLC = 0, то UART-контроллер не анализирует состояние сигнала  при передаче.

при передаче.

При значении бита DRT = 1 пользователь может запретить совместную одновременную работу приемника и передатчика. Этот режим часто применяется в многоточечной конфигурации, когда пользователь не желает принимать данные, которые он сам передает. Для этого он на время работы своего передатчика запрещает работу приемника. При значении DRT = 0 обеспечивается совместная работа приемника и передатчика.

Пользователь может при работе настраивать работу UART-контроллера или в асинхронном режиме, если бит SYN = 0, или в синхронном режиме, если бит SYN - 1. При работе в асинхронном режиме коэффициент внутреннего увеличения тактовой частоты в 8х, 16х или 32х раза устанавливается при программировании соответствующих битов в регистре GSMR модуля СРМ.

Если канал работает с синхронным UART-протоколом и требуется увеличение скорости передачи (например, при работе с V.14 устройствами), то при программировании бита RZS = 1 может быть включен режим прием кадра данных без стоп-битов. На практике это реализуется как передача нулевого стоп-бита. Для ускорения работы канала нулевой стоп-бит может рассматриваться и как старт-бит следующего кадра данных. Получив кадр данных с нулевым стоп-битом, приемник продолжает свою работу, регистрирует ошибку кадра (так как кадр принят без стоп-бита), но генерирует прерывание по ошибке, только когда примет два BREAK-символа без стоп-битов.

Работа UART-контроллера. При передаче данные выставляются на TXDx-контакт, при приеме данные читаются с RXDx-контакта. При передаче LSB-биты в поле данных передаются первыми.

Данные для передачи и данные, которые приняты из сети, хранятся в буфере памяти. В буферах хранится только содержимое поля данных. Старт-бит, стоп-бит, бит контроля и бит адреса добавляются при передаче и удаляются при приеме самим SCO-каналом и в памяти не хранятся. При работе в многоточечном соединении допускается хранение в памяти адреса, принятого в кадре данных. Данные одного кадра могут занимать несколько буферов. Если при приеме или передаче символа произошли ошибки, то будет установлен соответствующий бит ошибки в слове состояния BD.

Размер FIFO SCC-канала при работе с UART-протоколом равен 32 байтам для приема и 32 байтам для передачи, если используется канал SCC1, и по 16 байт, если используются другие SCC-каналы. Размер ячейки буфера FIFO устанавливается равным 8 битам при программировании регистра GSMR. В СРМ пользователь может ускорить передачу данных из FIFO-буфера передачи, сократив число ячеек FIFO до одной, установив соответствующее значение в бите TFL в регистре GSMR.

Если SCO-канал настроен на работу с UART-протоколом, то параметры конкретного протокола хранятся в протокол-ориентированной области parameter RAM (табл. 5.72).

Прием данных UART-контроллером. В UART-протоколе в отсутствие передачи по сети передаются IDLE-символы, которые состоят из 9-13 единиц «1». Размер IDLE-noc-ледовательности зависит от размера кадра данных, на работу с которым настроен канал. Размер IDLE-символа равен: 1 старт-бит + 5, 6, 7, 8 битов данных + 1 бит контроля (если он используется) + 1,2 стоп-бита. Приемник канала постоянно подсчитывает число полученных IDLE-символов в счетчике IDLE-символов IDLC. Если начинается прием нового кадра данных, то содержимое счетчика IDLC сбрасывается. Таким образом, IDLC-счетчик подсчитывает число IDLE-символов, полученных между приемом двух кадров данных. Пользователь может в ячейке MAXJDL определить максимально допустимое число IDLE-символов между кадрами данных.IDLC - это вычитающий счетчик, и при сбросе в него записывается содержимое ячейки MAXJDL, если счетчик IDLC досчитал до 0, то возникает ошибка приема «IDLE sequence». Текущий буфер закрывается, в нем устанавливается бит ID:= 1 (закрыто из-за IDLE-переполнения) и генерируется RX-npe-рывание в регистре событий, если оно разрешено. Если не был открыт буфер для приема, то прерывание не генерируется.

Для работы в сетях, где присутствуют более двух станций, в состав кадра UART-npo-токола введен бит адреса. Если бит адреса равен единице, то в кадре данных передается адрес получателя всех следующих кадров данных до кадра, в котором снова будет установлен бит адреса равный единице. UART-контроллер при обработке кадра с адресом может работать в двух режимах.

Таблица 5.72

Память параметров UART-контроллера в микроконтроллере МРС&60

| Адрес | Название | Размер, бит | Описание |

| SCC base+30 | - | Зарезервировано | |

| SCC base+34 | - | Зарезервировано | |

| SCC base+38 | MAXJDL | Максимальное число I OLE-символов | |

| SCC base+3A | IDLC | Счетчик IDLE-символов | |

| SCC base+3C | BRKCR | Регистр передаваемого BREAK-символа | |

| SCC base+3E | PAREC | Счетчик ошибок четности | |

| SCC base+40 | FRMEC | Счетчик ошибок формата кадра | |

| SCC base+42 | NOSEC | Счетчик ошибок шума | |

| SCC base+44 | BRKEC | Счетчик полученных BREAK-символов | |

| SCC base+46 | BRKLN | Длина принятой BREAK –последовательности -последовательности | |

| SCC base+48 | UADDR1 | Первый адрес | |

| SCC base+4A | UADDR2 | Второй адрес | |

| SCC base+4C | RTEMP | Временная память приемника | |

| SCC base+4E | TOSEQ | Передаваемый служебный символ | |

| SCC base+50 | CHAR1 | Контрольный символ 1 | |

| SCC base+52 | CHAR2 | Контрольный символ 2 | |

| SCC base+54 | CHAR3 | Контрольный символ 3 | |

| SCC base+56 | CHAR4 | Контрольный символ 4 | |

| SCC base+58 | CHAR5 | Контрольный символ 5 | |

| SCC base+5A | CHAR6 | Контрольный символ 6 | |

| SCC base+5C | CHAR7 | Контрольный символ 7 | |

| SCC base+5E | CHAR8 | Контрольный символ 8 | |

| SCC base+60 | RCCM | Маска контрольных символов | |

| SCC base+62 | RCCR | Регистр принятого контрольного символа | |

| SCC base+64 | RLBC | Регистр принятого BREAK-символа | |

| Примечание. Все переменные в табл. 5.72, кроме ячеек IDLC, BRKLN, RTEMP, RCCR и | |||

| RLBC, инициализируются пользователем до начала работы с UART-контроллером. |

1. Неавтоматический режим. В этом режиме канал принимает пакет с адресом как

обычные данные, закрывает текущий буфер и записывает адрес в новый буфер. В слове

состояния этого буфера устанавливается бит, показывающий, что буфер содержит ад

рес. Дальнейшую обработку адреса должен выполнять центральный процессор.

2. Автоматический режим. В этом режиме канал сам анализирует принятый адрес.

Он сравнивает принятый адрес с двумя возможными, которые записаны в ячейки UADRR1

и UADRR2. В ячейках хранятся 8-битные разрешенные адреса для данного канала. Если

хотя бы один адрес совпал, то данные из следующих кадров данных будут приниматься

в буфер канала. При этом в первом буфере, в который будут записываться данные,

в слове состояния устанавливается бит А:= 1, показывающий, что это первый буфер

с данными из последовательности, и бит AM, показывающий, какой адрес совпал. Если

AM = 0 - совпал адрес ADRR2, если AM = 1 - то совпал адрес ADRR1.

Если при приеме кадра данных обнаружена ошибка контроля по четности/нечетности (parity error), то канал записывает принятый байт в буфер, закрывает

буфер, устанавливает бит ошибки PR:= 1 в слове состояния BD и генерирует RX-прерывание через регистр событий (если оно разрешено). Также увеличивается на единицу счетчик ошибок четности в счетчике PAREC. В автоматическом многоточечном режиме работы канал переходит в режим «охоты».

При приеме в асинхронном режиме UART-контроллер три раза опрашивает значение бита на битовом интервале (oversampling). Если эти значения не равны, то возникает ошибка шума (noise error). При этом канал увеличивает на единицу счетчик ошибок шума в ячейке NOSEC, записывает принятый символ в буфер и продолжает нормальную работу.

При приеме UART-контроллер выделяет кадр данных из битового потока по старт-биту в начале и стоп-битам в конце кадра. Если в кадре не обнаружены «1» стоп-битов, то возникает ошибка формата (frame error). Канал записывает принятый символ в буфер, закрывает буфер и устанавливает в его слове состояния бит FR:= 1, увеличивает на единицу счетчик ошибок формата FRMEC и генерирует прерывание RX через регистр событий (если оно разрешено). Если произошла ошибка формата, контроль по четности не производится. В автоматическом многоточечном режиме работы канал переходит в режим «охоты».

Если UART-контроллер работает в синхронном режиме с нулевыми стоп-битами (бит RZS = 1 в регистре PSMR настройки UART-режима), ошибка формата обнаруживается, но пользователь может не реагировать на нее.

При приеме данные записываются в FIFO выбранного канала, далее они под управлением RISC-контроллера по SDMA-каналам пересылаются в память. Если скорость работы SDMA-каналов и сети не согласована, возможно возникновение ошибки переполнения (overrun), когда ячейки FIFO все заняты, а из сети получены новые данные. В этом случае: новые данные запишутся поверх старых символов в FIFO-буфер, буфер приема в памяти закроется, установится бит переполнения OV:= 1 в слове состояния BD и будет сгенерировано прерывание RX через регистр событий (если оно разрешено). В автоматическом многоточечном режиме работы канал переходит в режим «охоты».

При приеме UART-контроллер может использовать вход  для автоматического контроля наличия передачи в сети. Если сигнал

для автоматического контроля наличия передачи в сети. Если сигнал  равен единице при приеме символа, то возникает ошибка (CD lost) «потери CD-сигнала». Прием символа прекращается, буфер закрывается, устанавливается бит CD:= 1 в слове состояния BD и генерируется прерывание RX через регистр событий (если оно разрешено). В автоматическом многоточечном режиме работы канал переходит в режим «охоты».

равен единице при приеме символа, то возникает ошибка (CD lost) «потери CD-сигнала». Прием символа прекращается, буфер закрывается, устанавливается бит CD:= 1 в слове состояния BD и генерируется прерывание RX через регистр событий (если оно разрешено). В автоматическом многоточечном режиме работы канал переходит в режим «охоты».

В режим «охоты» перевести канал может и пользователь, если передаст через RISC-контроллер каналу команду ENTER HUNT MODE. Если при этом канал принимал сообщение, то оно будет потеряно. Находясь в режиме «охоты», приемник принимает BREAK-символы, увеличивает счетчик BRKEC, генерирует BRK-прерывание через регистр событий. Переход в рабочий режим возможен, если придет IDLE-символ или кадр с установленным битом адреса в многоточечной сети. Таким образом, в режиме «охоты» канал прекращает текущий прием кадра, закрывает старый буфер, подготавливает новый буфер и ждет нового кадра.

Если при приеме символов в режиме UART-протокола коммуникационный процессор получит команду CLOSE Rx BD, то он останавливает прием в текущий буфер, закрывает текущий BD, генерирует маскируемое прерывание и начинает прием в новый буфер.

Прием служебных символов. В ходе своей работы приемник может быть запрограммирован на выявление во входном битовом потоке кадров, которые содержат служебные символы. Служебным называется символ, при приеме которого может генерироваться прерывание. При обработке этого прерывания пользователь может анализировать процесс приема символов в сети. Формат служебных символов задает сам пользователь в регистрах CHAR1-CHAR8. Регистры управления служебными символами имеют следующий формат (рис. 5.107).

Каждый служебный символ имеет размер 8 бит. Принимая новый кадр данных, приемник начинает последовательно сравнивать его содержимое со служебными символами в таблице. Пользователь может управлять размером таблицы служебных символов с помощью бита Е (конец таблицы). Если у символа CHARi бит Е = 1, то это последний символ в таблице, и приемник прекращает проверку служебных символов. Если необходимо иметь таблицу из восьми символов, то у всех ячеек Е = 0.

Если служебный символ принят и совпал с шаблоном из таблицы, то он может быть сохранен в буфере, если бит R = 0 в ячейке шаблона, или может быть сохранен во временном регистре RCCR, если бит R = 1. Если бит R = 0, то после передачи символа в буфер буфер закрывается, новый буфер открывается для приема следующих данных и генерируется прерывание, если бит I = 1 в слове состояния BD. Если бит R = 1, то операции с текущим буфером не производится, но прерывание генерируется.

|

Пользователь может запретить проверку сравнения некоторых служебных символов с помощью регистра маски RCCM (рис. 5.107). В младших восьми битах этого регистра хранятся признаки проверки символов. Если i-разряд равен нулю, то проверка на сравнение принятого символа и служебного символа CHARi не производится. Если i-разряд равен единице, то символ CHARi принимает участие в сравнении. В старших разрядах (15-й и 14-й биты) ячейки RCCM хранятся, для того чтобы избежать ошибок при обработке битов Е и R в таблице служебных символов.

Если служебный символ был сохранен в буфере, то в слове состояния ВО устанавливается бит С:= 1, который сообщает пользователю, что последний байт в буфере - это служебный символ.

Кроме служебных символов UART-контроллер может контролировать прием символов BREAK. Символ BREAK - это от 9 до 13 «О» без стоп-битов. Если контроллер получил последовательность BREAK-символов, то он увеличивает счетчик BRKEC и закрывает текущий буфер приема, устанавливает в его слове состояния бит BR:= 1 и генерирует Rx-прерывание через регистр событий, если оно разрешено. В СРМ-процессоре контроллер также контролирует длину BREAK-последовательности.

При приеме первого BREAK-символа контроллер устанавливает бит начала последовательности BRKs в регистре событий. Далее он подсчитывает длину последовательности в символах. При получении первого бита, равного единице, контроллер записывает длину BREAK-последовательности в регистр BRKLN и устанавливает бит конца последовательности BRKe в регистре событий. Напомним, что изменение значения любого бита в регистре событий может вызвать прерывание центрального процессора, если оно разрешено.

Если UART-контроллер работает в синхронном режиме (бит SYN = 1 в регистре режима UART-контроллера) и установлен бит нулевых стоп-битов RZS = 1, то BREAK-после-довательность регистрируется только после приема двух BREAK-символов. Каждый последний принятый BREAK-символ будет сохраняться в регистре RLBC. Пользователь может подсчитать длину (число «О») в последнем BREAK-символе, начиная с 15-го бита в регистре RLBC и в сторону 0-го бита до бита, значение которого равно единице. Например, если в регистре RLBC записан двоичный код 0001хххххххх, то это значит, что было принято три нулевых бита.

Передача символов. При передаче UART-контроллер получает из буфера FIFO только сам символ, который будет передан в поле данных. Остальные поля кадра заполняются внутри SCC-контроллера. Во-первых, контроллер анализирует, какой тип контроля будет применен, и вычисляет контрольную сумму, которая записывается в бит контроля в кадре данных. Во-вторых, надо или нет вводить бит адреса в формат кадра. В-третьих, в формат кадра вводится необходимое число стоп-битов, при этом контролируется использование дробных стоп-битов.

Если передается первый символ из нового буфера данных, то в слове состояния буферного дескриптора анализируются биты А, Р, NS, CR. Бит N8 = 1 определяет, что все данные из буфера должны передаваться без стоп-битов. Если бит NS = 0, то все данные передаются со стоп-битами. Если установлен бит А = 1, то все данные из буфера передаются как адреса с установленным в «1» битом адреса в формате кадра, но только если контроллер настроен на работу в режиме многоточечного соединения. Если установлен бит CR = 1, то между передачами содержимого двух соседних буферов данных в канал выводятся три бита IDLE «1». Сигнал CTS, который должен быть активен при передаче данных, во время передачи IDLE-битов становится пассивным, генерируется прерывание «потеря CTS сигнала» и выставляется бит СТ = 1 (потеря CTS) в слове состояния текущего буфера. Если бит CR = 0, то следующий буфер передается сразу за текущим без задержек, если он был готов к передаче. При этом бит потери CTS - бит СТ в слове состояния BD не устанавливается. Если в слове состояния BD установлен бит Р = 1, то перед передачей содержимого буфера передается символ преамбулы (все биты «1»), и на другом конце канала обнаруживают IDLE-состояние линии связи перед получением данных. Преамбула передается, даже если длина буфера в BD установлена равной нулю. Преамбула представляет собой символ такой же длины, что и передаваемые данные, только все биты в символе равны единице.

Если UART-контроллер получил от CPU-ядра команду STOP TRANSMIT, то он передает в сеть содержимое FIFO передачи, затем передает определенное число символов BREAK, далее он переходит к передаче IDLE-символов, пока не получит команду RESTART TRANSMIT. Формат BREAK-символа представляет собой символ установленной длины, у которого все биты равны нулю и без стоп-битов. Количество BREAK-символов, которые UART-контроллер передаст в сеть, указывается пользователем в регистре BRKCR.

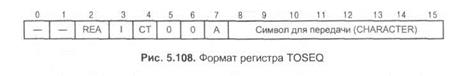

Пользователь может управлять процессом передачи данных (flow control), вставляя в поток передаваемой информации служебные символы. Для этого в области параметров протокола выделена специальная ячейка TOSEQ. В эту ячейку записывается символ управления передачей, который имеет наивысший приоритет перед передачей других символов. Перед тем как прочитать очередной символ из буфера данных, UART-контроллер проверяет готовность этого служебного символа. Если символ готов, то он помещается в FIFO передачи, а затем в канал будет передан символ управления передачей, например символы XON или XOFF.

Когда центральный процессор подготовил символ для передачи, устанавливается бит REA (READY):= 1 (рис. 5.108). Коммуникационный контроллер сбрасывает этот бит REA:= 0 только после окончания передачи служебного символа, формат которого указан в поле CHARACTER. После передачи служебного символа, если установлен бит I (Interrupt) = 1, то CPU уведомляется прерыванием через бит Тх-регистра событий U ART-контроллера.

Длина служебного символа CHARACTER совпадает с запрограммированной длиной других символов, с которыми работает контроллер. Значение поля CHARACTER может быть изменено пользователем, только когда сброшен бит готовности REA = 0.

При передаче служебного символа контролируется состояние сигнала разрешения передачи  = 0. Если при передаче служебного символа был потерян сигнал, т. е.

= 0. Если при передаче служебного символа был потерян сигнал, т. е.  = 1, то устанавливается бит СТ:= 1 в ячейке CHAR8 или TOSEQ, а также устанавливается бит CTS:= 1 в регистре событий UART-контроллера. Если передача служебного символа прервала передачу символов из буфера данных и при этом был потерян сигнал

= 1, то устанавливается бит СТ:= 1 в ячейке CHAR8 или TOSEQ, а также устанавливается бит CTS:= 1 в регистре событий UART-контроллера. Если передача служебного символа прервала передачу символов из буфера данных и при этом был потерян сигнал  , то и в слове состояния BD текущего буфера будет установлен бит потери сигнала

, то и в слове состояния BD текущего буфера будет установлен бит потери сигнала  бит СТ:= 1.

бит СТ:= 1.

Когда UART-контроллер работает в многоточечной конфигурации, пользователь должен установить бит А:= 1 в ячейке служебного символа.

|

Transparent-контроллер. Transparent-контроллер позволяет SCC-каналу принимать и передавать сетевые данные без их модификации. Выделяют несколько задач, для которых характерно использование режима «прозрачной передачи».

• Для передачи по сети в последовательном коде «особенных» данных, например, голоса, если не выделено специального протокола для этих целей.

•Для передачи данных в последовательном коде между микросхемами на плате или

приборе. Для этого требуется выполнять последовательно-параллельное и параллель

но-последовательное преобразование.

• Пользователь может организовать передачу кадров любого протокола в поле данных

кадра «прозрачного» уровня без промежуточного их декодирования. Например, для

организации связи между высокоскоростной и низкоскоростной сетями, которые обе

работают с временным мультиплексированием. В этом случае SCC-контроллер будет

выполнять функцию согласования скоростей двух сетей.

• Наиболее часто SCC-контроллеры с Transparent-режимом работы используются для

построения коммуникаторов и концентраторов. В этих случаях контроллер будет вы

полнять функции мультиплексирования данных от нескольких низкоскоростных кана

лов в один высокоскоростной.

• Часто режим прозрачной передачи применяют для передачи данных из памяти одного

компьютера в память другого компьютера, используя при этом преобразование дан

ных в последовательный код при передаче по последовательному каналу связи.

Настройка SCC-канала для работы в Transparent-режиме обмена в контроллере МРС860 производится в регистре общих режимов GSMR. Установка битов ТТХ = 1 для передатчика и TRX = 1 для приемника включает полнодуплексный режим «прозрачной передачи» независимо от значений битов MODE, которые осуществляют выбор коммуникационного потока для SCC-канала. Если же установлен только один из битов, то лишь одна часть SCC-канала будет работать в прозрачном режиме, а другая часть будет работать с коммуникационным протоколом, который выбран в битах MODE.

Transparent-контроллер имеет полностью независимые приемную и передающую части. Тактирование работы контроллера может производиться от внутреннего BRG-гене-ратора, или через внешние контакты, или через блок DPLL.

При передаче может быть выбран любой порядок битов в байте (или LSB-бит первый, или MSB-бит первый) и факультативно добавленные при передаче и контролированные при приеме поля контрольной суммы CRC. Для проверки передаваемых данных может быть использована или 16- или 32-разрядная CRC-контрольная сумма. В ячейке CRC_P (табл. 5.73) хранится начальное значение счетчика CRC 0x0000FFFF - для CRC16 и 0xFFFFFFFF -для CRC32. Для счетчика CRC_C памяти параметров хранится константа, определяющая тип образующего полинома циклического кода 0x0000FOBS - для CRC16 и 0xDEBB20F3 - для CRC32. Выбор типа CRC контрольной суммы производится в бите TCRC регистра режима GSMR.

Таблица 5.73

Память параметров Transparent-протокола в микроконтроллере МРС860

| Адрес | Название | Размер, бит | Назначение |

| SCCbase+30 SCC base+34 | CRC_P CRC_C | Начальное значение CRC-счетчика Константа CRC для приемника |

Синхронизация Transparent-контроллера. Синхронизация приемника и передатчика может выполняться двумя способами:

1) при помощи синхросигналов в канале связи;

2) при помощи внешних сигналов синхронизации.

Режим синхронизации устанавливается в битах SYNL в регистре GSMR (табл. 5.74).

Таблица 5.74

Размер синхросимволов

| Бит SYNL | Тип синхронизации |

| Внешними сигналами 4-битные инхросимволы 8-битные синхросимволы 16-битные синхросимволы |

Формат 4/8/16-битных синхросигналов задается в регистре синхронизации DSR. Например, если для синхронизации приемника выбран режим SYNL = 01, то прием кадра начинается после приема четырех бит синхросигнала.

Внешние сигналы  и

и  могут быть использованы для синхронизации передатчика и приемника. Бит CTSP в регистре GSMR определяет вид сигнала

могут быть использованы для синхронизации передатчика и приемника. Бит CTSP в регистре GSMR определяет вид сигнала  и способ синхронизации передатчика, а бит СОР — вид сигнала

и способ синхронизации передатчика, а бит СОР — вид сигнала  и способ синхронизации приемника. Если биты CTSP и СОР равны единице, то соответствующие сигналы выставляются в виде импульсов, которые отмечают момент начала обмена. В дальнейшем при обмене изменение состояния этих сигналов игнорируется. Этот режим удобен, когда пользователь желает передавать все данные без прерывания при передаче отдельных кадров. Если же биты CTSP или СОР равны нулю, то эти сигналы выставляются (становятся активными) только во время передачи кадра данных, во время промежутка между отдельными кадрами эти сигналы пассивны. Этот режим рекомендуется использовать, когда необходимо через прерывание отслеживать моменты передачи отдельных кадров в потоке данных.

и способ синхронизации приемника. Если биты CTSP и СОР равны единице, то соответствующие сигналы выставляются в виде импульсов, которые отмечают момент начала обмена. В дальнейшем при обмене изменение состояния этих сигналов игнорируется. Этот режим удобен, когда пользователь желает передавать все данные без прерывания при передаче отдельных кадров. Если же биты CTSP или СОР равны нулю, то эти сигналы выставляются (становятся активными) только во время передачи кадра данных, во время промежутка между отдельными кадрами эти сигналы пассивны. Этот режим рекомендуется использовать, когда необходимо через прерывание отслеживать моменты передачи отдельных кадров в потоке данных.

Сигналы  и

и  могут быть или асинхронными к передаваемым данным, и тогда контроллер будет производить внутреннюю синхронизацию, или синхронизированными с кадрами данных, что используется для ускорения обработки данных. Биты CDS и CTSS при значении «0» определяют асинхронный режим работы, а значение «1» определяет синхронизированный режим работы данных и сигналов

могут быть или асинхронными к передаваемым данным, и тогда контроллер будет производить внутреннюю синхронизацию, или синхронизированными с кадрами данных, что используется для ускорения обработки данных. Биты CDS и CTSS при значении «0» определяют асинхронный режим работы, а значение «1» определяет синхронизированный режим работы данных и сигналов  и

и  соответственно (рис. 5.109).

соответственно (рис. 5.109).

Синхронизированный режим работы часто используется для соединения нескольких коммуникационных контроллеров (рис. 5.110), когда выход  одного контроллера соединяется со входом

одного контроллера соединяется со входом  другого. При такой конфигурации сигнал

другого. При такой конфигурации сигнал  не используется, а начало передачи данных отмечается активным сигналом

не используется, а начало передачи данных отмечается активным сигналом  = 0.

= 0.

.

Таким образом, синхронизация передатчика может быть выполнена или при помощи внешнего сигнала  , или приемником после того, как он сам синхронизируется.

, или приемником после того, как он сам синхронизируется.

Если в регистре GSMR установлен бит TXSY = 1, то работа приемника и передатчика синхронизирована. Если дополнительно установлен бит RSYN = 1, то передатчик будет синхронизирован только после получения активного сигнала  = 0 и после того, как будет синхронизирован приемник. Если сигнал

= 0 и после того, как будет синхронизирован приемник. Если сигнал  = 0, то передача начнется через восемь периодов тактовой частоты передатчика после того, как приемник начнет получать данные.

= 0, то передача начнется через восемь периодов тактовой частоты передатчика после того, как приемник начнет получать данные.

|

|

Передача сообщений. После включения в работу (бит ENT = 1 в регистре GSMR) передатчик начинает передавать в сеть символы IDLE и опрашивает готовность к передаче данных из первого буфера таблицы TxBD. Если данные готовы (бит R = 1 в слове состояния буфера), то они по каналам SDMA загружаются в буфер FIFO передатчика, и контроллер ожидает синхронизации для начала передач.

После того как передатчик будет синхронизирован, он начнет передачу данных из FIFO-буфера.

После передачи каждого буфера данных контроллер проверяет бит последнего буфера кадра (L = 1) в слове состояния буфера. Если бит L = 1, то контроллер записывает в слово состояния буфера биты статуса переданного кадра, сбрасывает бит R:= 0 v начинает передавать символы IDLE, пока следующие данные не будут подготовлены Если же бит L = 0, то контроллер сбрасывает бит готовности буфера к передаче R:= 0 и переходит к передаче следующего буфера данных текущего кадра без разрывов на линиях связи при передаче соседних буферов. Если очередной буфер данных еще не готов (его бит R = 0), то регистрируется ошибка underrun и устанавливается бит ТХЕ в регистре событий Transparent-контроллера.

Если в слове состояния буфера был установлен бит I = 1, то генерируется прерывание к центральному процессору по окончании передачи этого буфера.

При передаче может быть передано любое количество байт данных. Если в регистре GSMR бит REVD = 1, то Transparent-контроллер дополнительно будет менять порядок бит в байте. По умолчанию LSB-бит передается первым.

Пользователь может управлять размером буфера FIFO передатчика, программируя значение бита TFL в регистре GSMR. Если бит TFL = 0, то размер буфера равен 32 байт для SCCI-канала и 16 байт для других SCC-каналов. Если же бит TFL = 1, то размер буфера FIFO передатчика равен 1 байт. Этот режим используется для низкоскоростных каналов связи, так как при высоких скоростях возрастает вероятность возникновения ошибки underrun, когда центральный процессор не будет успевать заполнять FIFO-буфер по SDMA-каналам.

Пользователь может управлять работой передатчика с помощью команд STOP TRANSMIT, GRACEFUL STOP TRANSMIT, RESTART TRANSMIT, INIT TX PARAMETERS.

При передаче регистрируется два типа ошибок.

1. Незаполнение (underrun), когда RISC-контроллер не успевает заполнять ячейки буфера FIFO при передаче кадра данных. При возникновении этой ошибки контроллер прекращает передачу, закрывает буфер и устанавливает бит ошибки UN:= 1 в слове состояния буфера и бит ТХЕ:= 1 в регистре событий, вызывая прерывание процессора. Эта ошибка регистрируется только между передачей соседних кадров. Если ошибка произошла при передаче последнего буфера кадра (бит L = 1 в слове состояния), то устанавливается только бит ТХЕ:= 1 в регистре событий канала.

2. Ошибка потери сигнала  . Если во время передачи данных будет сброшен активный сигнал, и

. Если во время передачи данных будет сброшен активный сигнал, и  = 1, то регистрируется ошибка, контроллер прекращает передачу, закрывает буфер, устанавливает бит ошибки СТ:= 1 в слове состояния буфера и бит ТХЕ:= 1 в регистре событий, вызывая прерывание процессора.

= 1, то регистрируется ошибка, контроллер прекращает передачу, закрывает буфер, устанавливает бит ошибки СТ:= 1 в слове состояния буфера и бит ТХЕ:= 1 в регистре событий, вызывая прерывание процессора.

Прием сообщений. Для начала приема данных приемник SCC-канала должен пройти процедуру синхронизации. Синхронизация достигается или при приходе внешнего сигнала, или при приходе SYNC-последовательностей. По окончании синхронизации приемник начинает прием символов.

Когда текущий буфер приема полностью заполняется, SCC-контроллер сбрасывает бит пустого буфера Е:= 0 в слове состояния и генерирует прерывание, если установлен бит І = 1. Далее контроллер переходит к заполнению следующего буфера. Если этот буфер еще не подготовлен центральным процессором, то регистрируется ошибка занятости и устанавливается бит BSY:= 1 в регистре события Transparent-контроллера.

Если в регистре GSMR установлен бит REVD=1, то контроллер при записи данных в буфер меняет порядок битов в байтах.

Пользователь может управлять размером буфера FIFO приемника, программируя значение бита RFW в регистре GSMR. Если бит RFW = 0, то канал SCC1 имеет буфер FIFO 32 байта и 16 байт для других SCC-каналов. Размер каждой ячейки буфера - 32 бита. Этот режим используется для высокоскоростных сетей. Для низкоскоростных сетей используется установка бита RFW = 1. Канал SCC1 имеет буфер FIFO размером 8 байт и 4-байтный FIFO для других SCC-каналов, а размер каждой ячейки 8 бит, Но использование режима с битом RFW = 1 может привести к возникновению ошибки overrun (переполнения), если скорость работы сети выше скорости обработки данных в коммуникационном контроллере.

Приемник всегда проверяет и производит подсчет контрольной суммы CRC в принимаемом кадре. Тип контрольной суммы задается в бите TCRC регистра GSMR. Если контроль CRC