ѕри работе в нормальном режиме дл€ асинхронных протоколов сигнал  становитс€ ак≠тивным, когда данные дл€ передачи загружены в буфер FIFO и наступает отрицательный перепад тактового сигнала TCLK. ¬ыводы

становитс€ ак≠тивным, когда данные дл€ передачи загружены в буфер FIFO и наступает отрицательный перепад тактового сигнала TCLK. ¬ыводы  ,

,  могут использоватьс€ дл€ контро≠л€ передачи так же, как и в синхронных протоколах. ƒополнительно UART-контроллер имеет специальную опцию настройки дл€ контрол€ передачи с помощью

могут использоватьс€ дл€ контро≠л€ передачи так же, как и в синхронных протоколах. ƒополнительно UART-контроллер имеет специальную опцию настройки дл€ контрол€ передачи с помощью  -сигнала.

-сигнала.

≈сли сигнал  становитс€ активным, когда сигнал

становитс€ активным, когда сигнал  = 0, то передача начинаетс€ через два битовых интервала. ≈сли же сигнал

= 0, то передача начинаетс€ через два битовых интервала. ≈сли же сигнал  = 0, но сигнал

= 0, но сигнал  =1 и бит CTSS = ќ, то передача начнетс€ через три битовых интервала. ≈сли же сигнал

=1 и бит CTSS = ќ, то передача начнетс€ через три битовых интервала. ≈сли же сигнал  = 0, но сигнал

= 0, но сигнал  = 1 и бит CTSS = 1, то передача начнетс€ через два битовых интервала.

= 1 и бит CTSS = 1, то передача начнетс€ через два битовых интервала.

”правление буферами FIFO приемника и передатчика. Ѕит TFL определ€ет длину буфера FIFO передатчика. ≈сли бит“–1 = 0, то используетс€ стандартный размер буфера - 32 байта дл€ SCC1-контроллера и по 16 байт дл€ других SCC-контроллеров. –ежим TFL = 1 используетс€ дл€ символьно-ориентированных протоколов, например, UART или BISYNC, и устанавливает размер буфера FIFO в 1 байт. Ётот минимальный размер буфера используетс€ дл€ ускорени€ процесса обработки информации.

Ѕит RFW определ€ет ширину €чеек буфера FIFO приемника. ≈сли бит RFW = 0, то размер €чейки буфера равен 32 битам. ƒанные принимаютс€ бит за битом, пока не будет прин€то 32 бита информации, только затем они могут быть переданы в пам€ть по кана≠лам SDMA. Ёта конфигураци€ необходима дл€ протоколов, основанных на HDLC-типе кадра и протокола Ethernet, а также рекомендована дл€ высокоскоростных протоколов Ђпрозрачной передачиї. ¬ этом режиме размер €чейки FIFO дл€ SCd-канала равен 32 битам и 16 битам дл€ других каналов SCC.

–ежим работы с битом RFW = 1 предназначен дл€ низкоскоростных протоколов Ђпро≠зрачной передачиї и дл€ символьно-ориентированных протоколов. –азмер €чейки бу≠фера устанавливаетс€ равным 8 битам, буфер FIFO SCC1 канала имеет размер 8 байт, а у других SCC-каналов размер буфера - 4 байта. “аким образом, принимаемые данные передаютс€ в буферы данных в пам€ти по 8 бит, не дожида€сь приема всех 32 битов. Ётот режим может быть использован дл€ протоколов HDLC, HDLC bus, Apple Talk и Ethernet.

Ќастройка синхронизации. Ѕит TXSY определ€ет взаимную синхронизацию между приемником и передатчиком. ќбычно установка этого бита требуетс€ при работе с вне≠шним оборудованием, которое поддерживает стандарт ’.21. ѕри работе с обычным сетевым оборудованием бит TXSY = 0 и приемник с передатчиком работают независимо. ≈сли выбран режим с битом TXSY = 1, то передача начнетс€ только через 8 периодов тактовой частоты после начала приема данных. ƒополнительно, в режиме прозрачной передачи, если установлен бит RSYN = 1, то приемник предварительно должен быть синхронизирован с частотой входного потока битов и до начала передачи должен быть выставлен активный сигнал  = 0.

= 0.

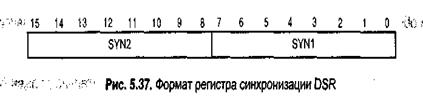

Ѕит SYNL используетс€ при настройке режимов работы BISYNC- и Transparent-кон-троллеров и служит дл€ задани€ длины синхросимволов (табл. 5.17). ‘ормат синхросимволов SYNC1 и SYNC2 дл€ синхронных протоколов обычно задаетс€ в регистре син≠хронизации DSR. ѕри передаче перед посылкой кадра передатчик добавл€ет к кадру данных заданное число символов синхронизации. ‘ормат дополнительных синхросим≠волов может быть определен в специальных €чейках протокол-ориентированной части пам€ти параметров SCC-канала.

|

|

|

Ќазначение битов в регистре синхронизации (рис. 5.37) различно дл€ разных коммуникационных протоколов (табл. 5.18). ѕосле системного сброса этот регистр настроен на работу с HDLC-протоколом. ≈сли регистр DSR содержит символы синхронизации, то содержимое регистра всегда передаетс€ по правилу ЂLSB бит - первымї.

Ѕит TCI при значении, равном 1, задает внутреннее инвертирование тактового сигна≠ла передатчика перед его использованием схемами SCC-контроллера. ¬ нормальном режиме работы данные выставл€ютс€ на линию TXD по отрицательному перепаду такто≠вого сигнала, а считываютс€ с линии RXD - по положительному перепаду тактового сиг≠нала. ”становка режима внутреннего инвертировани€ позвол€ет выдавать данные на полпериода раньше, т. е. по положительному перепаду тактового сигнала. ¬ данном слу≠чае внешним приемником эти же данные будут прин€ты на один период тактового сигна≠ла позже, т. е. по следующему положительному перепаду этого же тактового сигнала. »спользование этого режима работы рекомендовано дл€ контроллеров HDLC, Transparent и Ethernet-протоколов при высоких частотах передачи (больше чем 8 ћ√ц), так как этот режим обеспечивает дополнительное врем€ предустановки и настройки рабочей часто≠ты дл€ внешнего приемника.

Ќастройка режимов блока DPLL. аждый SCC-канал содержит блок DPLL (Digital Phase-Locked Loop), который выполн€ет кодирование/декодирование данных от SCC-канала. Ќиже приведены основные режимы кодировани€/декодировани€ (рис. 5.38).

ХRZ: Ђ1ї Ч кодируетс€ высоким уровнем сигнала на битовом интервале; Ђ0ї - кодируетс€ низким уровнем сигнала на битовом интервале.

ХNRZI MARK: Ђ1ї - кодируетс€ отсутствием перепадов и смен состо€ни€ сигналов на битовом интервале; Ђ0ї - кодируетс€ перепадом сигнала (сменой состо€ни€ сигнала на противоположное) в начале битового интервала.

ХNRZI SPACE: Ђ1ї - смена состо€ни€ сигнала на противоположное в начале битового интервала; Ђ0ї - нет смен и перепадов сигнала на битовом интервале.

ХFMO: Ђ1ї - кодируетс€ перепадом сигнала в начале битового интервала; Ђ0ї -кодируетс€ перепадом сигнала в начале и в центре битового интервала.

ХFM1: Ђ1ї - кодируетс€ перепадом сигнала в начале и в центре битового интервала; Ђ0ї - кодируетс€ перепадом сигнала в начале битового интервала.

ХManchester: Ђ1ї - кодируетс€ отрицательным перепадом сигнала в середине битового интервала; Ђ0ї - кодируетс€ положительным перепадом сигнала в середине битового интервала. ѕри этом допускаютс€ перепады сигналов на границах битового интерва≠ла, чтобы обеспечить правильную пол€рность перехода в середине.

ХDifferential Manchester: Ђ1ї - кодируетс€ сменой сигнала в середине битового интервала. Ќаправление перепада должно быть противоположным направлению перепада на предыдущем битовом интервале; Ђ0ї - кодируетс€ сменой сигнала в середине битового интервала. Ќаправление перепада должно быть аналогичным направлению перепада на предыдущем битовом интервале.

Ќастройка блока DPLL на определенный режим работы производитс€ при програм≠мировании регистра режима SCC-канала GSMR (табл. 5.19). Ѕиты RENC определ€ют способ декодировани€ данных при приеме, а биты TENC - способ кодировани€ данных при передаче. —пособ кодировани€ NRZ обычно используетс€ SCC-каналами, если блок DPLL не работает.

|

|

|

“аблица 5.19

Ѕлок DPLL может быть настроен на дополнительное инвертирование выходных дан≠ных при передаче, если бит TINV = 1, и на инвертирование входных данных при приеме, если бит RINV= 1. »нвертирование сигналов используетс€ дл€ получени€ дополнитель≠ных способов кодировани€. Ќапример, дл€ получени€ способа кодировани€ FM1, если выбран способ кодировани€ FMO, или дл€ получени€ способа кодировани€ NRZI SPACE, если выбрано кодирование NRZI MARK.

ќбычно преобразование сигналов в DPLL-блоке используетс€, если канал работает с самосинхронизирующимис€ кодами, в которых тактова€ частота передаетс€ внутри сиг≠налов данных, т. е. она заложена в специально кодированные данные. Ќо если пользо≠ватель желает работать с данными, которые тактируютс€ отдельной внешней частотой, то режим DPLL может быть выключен. DPLL-кодирование также не примен€етс€, если SCC-контроллер настроен на режим работы с протоколом Ethernet.

ѕри приеме DPLL-блок выдел€ет тактовую частоту из сигналов данных и передает ее и сами данные на обработку SCC-каналу. ѕри передаче DPLL-блок кодирует данные от SCC-каналов, использу€ самосинхронизирующее кодирование, и передает их по сети. ƒл€ оп≠ределени€ величины битового интервала блок DPLL использует или внешнюю тактовую частоту, или частоту от внутреннего BRG-генератора. –екомендуетс€, чтобы тактова€ час≠тота была в 8, 16 или 32 раза больше, чем частота передачи данных по каналам св€зи. Ѕиты TDCR и RDCR в регистре GSMR задают коэффициент отношени€ частоты передава≠емых/принимаемых данных и частоты тактировани€ блока DPLL (табл. 5.20). ≈сли блок DPLL не используетс€, то все протоколы, кроме UART, работают с коэффициентом 1х. ѕри работе с протоколом UART в асинхронном режиме значени€ этих битов всегда определ€ют коэффициенты 8х, 16х или 32х. ¬ыбор значений этих битов зависит от способа кодировани€, и обычно приемник и передатчик используют одинаковый коэффициент увеличени€ TDCR = = RDCR. ѕри использовании коэффициента 8х достигаетс€ максимальна€ скорость обра≠ботки данных в контроллере, а коэффициент 32х обеспечивает высокое разрешение и высо≠кую надежность приема/передачи данных.

ѕри начале работы блок DPLL находитс€ в режиме поиска и ожидает перепада сигна≠ла на лини€х данных. ѕервый перепад вызывает сброс внутренних счетчиков DPLL и начало рабочего режима работы. ƒалее блок DPLL запускает счетчики и ищет очередной перепад сигнала на лини€х данных. ≈сли следующий перепад сигнала обнаружен, то блок DPLL, зна€ используемый способ кодировани€ и анализиру€ значение счетчиков, определ€ет частоту передаваемых данных.

Ѕиты EDGE определ€ют, по какому фронту тактового сигнала блок DPLL будет анали≠зировать линии данных. ≈сли биты EDGE = 00, то состо€ние линии данных RXD будет анализироватьс€ и по положительному перепаду тактового сигнала, и по отрицательно≠му. ѕри приеме закодированного сигнала блок DPLL должен настроитьс€ на определе≠ние значени€ входных данных в определенных точках, чтобы проверить правильность кодировани€ данных и определить величину битового интервала. ≈сли EDGE = 01, то только положительный фронт тактового сигнала используетс€ дл€ опроса значени€ на линии RxD, а если EDGE = 10 - только отрицательный фронт. ≈сли EDGE = 10, то на≠стройка DPLL-блока не производитс€.

¬ регистре GSMR в бите TSNC пользователь может определить максимально до≠пустимый интервал без перепадов сигналов (табл. 5.21). ≈сли счетчик DPLL достиг указанного значени€, а перепада сигнала на линии RXD нет, то сигнал несущей такто≠вой частоты становитс€ пассивным. ≈сли на линии RXD есть передача, то сигнал несущей частоты активен.

«начение бита TSNC = 01 обычно примен€етс€, если SCC-контроллер работает с про≠токолом Apple Talk. Ёти биты могут быть использованы в протоколе, чтобы избежать воз≠никновени€ прерываний при изменении состо€ни€ сигнала  , которое может происхо≠дить в течение передачи последовательности синхронизации кадра, котора€ предшеству≠ет открывающему флагу кадра.

, которое может происхо≠дить в течение передачи последовательности синхронизации кадра, котора€ предшеству≠ет открывающему флагу кадра.

|

|

|

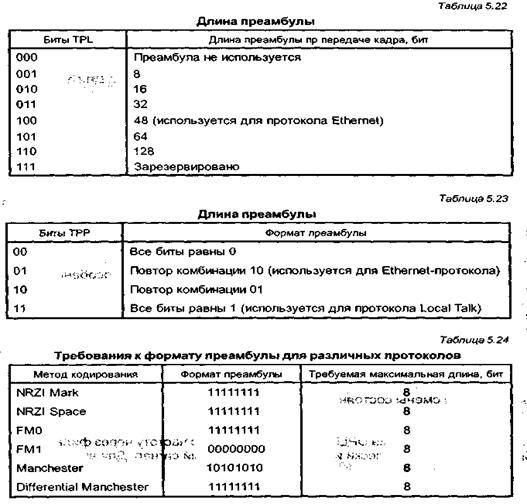

ƒл€ того чтобы блок DPLL мог заранее настроитьс€ на частоту приема данных, перед кадром данных обычно посылаютс€ специальные символы или преамбулы (preamble), или символы флага, или SYNC-символы синхронизации. ƒругие же протоколы требуют посылки специальных символов, состо€щих из чередующихс€ битов Ђ1ї и Ђ0ї. ѕри пе≠редаче данных каждый SCC-канал может быть настроен на передачу преамбулы. ƒлину преамбулы определ€ют значени€ битов TPL (табл. 5.22) в регистре GSMR, а формат преамбулы определ€ют значение битов “–– (табл. 5.23). «начени€ битов “–– и TPL иг≠норируютс€, если SCC-канал работает с протоколом UART.

¬ табл. 5.24 приведены требовани€ к формату и длине преамбулы дл€ различных методов кодировани€, соблюдение которых необходимо, чтобы блок DPLL смог распоз≠нать несущую частоту.

Ѕит TEND определ€ет состо€ние сигналов на выходах передатчика при пассивном состо€нии линии TxD при работе в NMSI-режиме. ≈сли бит TEND = 0, то кодировке под≠вергаютс€ только данные кадра, включа€ все флаги и синхропоследовательности. огда передачи нет, лини€ TxD= 1 (высокий уровень). ≈сли бит TEND = 1, то все данные, кото≠рые выдаютс€ на линию TxD, кодируютс€ выбранным способом. ѕри пассивном состо€≠нии линии передаютс€ закодированные единичные биты IDLE.

ћаксимальна€ частота передачи данных, которую может обеспечить блок DPLL при работе в режиме 8х и внешнем кварце в 25 ћ√ц, равна 25 ћ√ц/8 = 3,125 ћ√ц. “аким образом, частота, котора€ поступает с внешнего входа CLKx или от внутреннего BRG-генератора при работе с 25 ћ√ц контроллером, может быть более 25 ћ√ц, если DPLL работает в режиме 8х, 16х или 32х. ќграничение частоты тактировани€ SCC-каналов величиной SynCLK/2 не примен€етс€ к увеличению частоты блоком DPLL, так как частота дл€ тактировани€ SCC-каналов формируетс€ внутри, после того как блок DPLL сфор≠мирует частоту приемника. ѕоэтому даже сама€ быстра€ DPLL частота (8х) просто удов≠летвор€ет требованию 1:2.

Ќастройка режима кодировани€ в SIR-протоколе. ќсобый способ кодировани€ при≠мен€етс€ в протоколе Serial Infra-RED (SIR). анальный уровень этого протокола осно≠ван на стандарте передачи асинхронного протокола ASYNC HDLC. ƒл€ передачи данных по сети используетс€ формат UART-кадра: 1 старт-бит, 8 бит данных, 1 стоп-бит, битов контрол€ по четности нет (рис. 5.39). ѕри кодировке данных нулевой бит Ђ0ї кодируетс€ импульсом шириной 3/16 битового интервала по середине битового интервала, бит 1RP в регистре режима GSMR определ€ет пол€рность этого импульса. ≈диничный бит Ђ1ї кодируетс€ битовым интервалом без изменени€ сигнала. ≈сли бит IRP равен 0, то Ђ0ї кодируетс€ импульсом высокой пол€рности (high), если же IRP = 1, то импульсом отрица≠тельной пол€рности (low). —пособ кодировани€ SIR-протокола поддерживаетс€ только на канале SCC2. ƒл€ активации этого способа кодировани€ требуетс€ в битах RDCR и TDCR регистра режима GSMR задать коэффициент увеличени€ частоты 16х, а бит SIR установить в Ђ1ї.

”странение помех и ложных срабатываний. ѕомехи, которые воздействуют на так≠товые сигналы и привод€т к неправильному срабатыванию схем приемника и передатчи≠ка, €вл€ютс€ проблемой систем телекоммуникаций. —истемы, которые используют дл€ тактировани€ своих схем внешние источники тактовых сигналов, особенно подвержены этим ошибкам, которые могут возникать из-за сторонних шумов, из-за подключени€/разъе≠динени€ аппаратуры и кабелей или из-за неправильного волнового согласовани€ линий. аналы SCC-контроллеров в ћ–—860 содержат специальную схему, котора€ позвол€ет обнаруживать Ђглюкї (glitch) на лини€х тактового сигнала, который может вызвать пере≠ход SCC-контроллера в неправильное ошибочное состо€ние. Ёта схема позвол€ет вов≠рем€ известить систему о проблемах на физическом уровне управлени€. —хема обнару≠живает два типа Ђглюкаї. ѕервый тип (или всплеск) регистрируетс€, если перепад сигна≠ла между уровн€ми Ђ0ї и Ђ1ї состо€ни€ происходит быстрее, чем за минимальный допу≠стимый интервал смены состо€ни€ тактового сигнала. ¬торой тип регистрируетс€, когда смена состо€ни€ тактового сигнала происходит с нормальной скоростью, но присутству≠ет большой чрезмерный сторонний шум.

|

|

|

¬нутренние схемы блока DPLL пропускают входную частоту через фильтр шумов, что≠бы убрать паразитные всплески и оставить один чистый сигнал. ƒл€ включени€ этой схемы в работу в регистре GSMR введен дополнительный бит GDE.

≈сли этот бит равен 1, то схема обнаружени€ Ђглюкаї работает нормально и в случае возникновени€ ошибки будет установлен соответствующий бит в регистре событий SCC-канала. ≈сли этот бит равен 0, то схема обнаружени€ ошибок выключена и данный режим следует использовать, если каналы тактируютс€ от внутренних источников тактовых сигналов или если тактова€ часто≠та от внешних источников превышает максимальную частоту работы схемы обнаружени€, что составл€ет 6,25 ћ√ц при частоте кварца 25 ћ√ц.

ћеханизм прерываний. ”правление обработкой прерывани€ от SCC-каналов про≠изводитс€ контроллером прерывани€, который входит в состав —–ћ, с помощью регист≠ров запросов CIPR, регистра маски CIMR и регистра обслуживаемого прерывани€ CISR.

≈сли некоторый SCC-канал желает прервать работу центрального процессора, то он должен установить i бит в регистре запросов на прерывание CIPR (табл. 5.25), который соответствует прерыванию от этого канала. ѕри желании пользователь может замаски≠ровать прерывание от выбранного SCC-канала, сбросив в Ђ0ї i бит в регистре маски CIMR. ≈сли же центральный процессор в текущий момент времени зан€т обработкой прерывани€ от выбранного SCC-канала, то в регистре обслуживаемых прерываний CISR будет установлен в Ђ1ї i бит, соответствующий этому SCC-каналу. ¬о всех регистрах обслуживани€ прерывани€ i бит соответствует одному и тому же SCC-контроллеру.

¬заимные приоритеты запросов на прерывание между четырьм€ SCC-каналами в —–ћ программируютс€ в регистре конфигураций контроллера прерываний CICR (рис. 5.40). —ледует отметить, что регистр CICR производит настройку приоритетов толь≠ко SCC-каналов и не вли€ет на приоритеты других каналов ввода/вывода. »меетс€ четы≠ре позиции приоритетов (а, №, с, d), сама€ приоритетна€ - позици€ а.

Ѕиты SCCaP, SCbP, SCcP и SCdP определ€ют, какой SCC-канал занимает выбранную позицию в таблице приоритетов (табл. 5.26).

Ѕит SPS определ€ет абсолютные приоритеты запросов от SCC-каналов среди запро≠ сов от других модулей контроллера (табл. 5.27). ≈сли бит SPS = 0, то все запросы от SCC-каналов сгруппированы вместе и имеют высокий приоритет относительно других запросов. ≈сли бит SPS = 1, то запросы от SCC-каналов распределены по таблице при≠оритетов среди других запросов.

ќстальные биты в регистре CICR определ€ют работу самого контроллера прерыва≠ни€. Ѕит IEN при значении IEN = 1 разрешает работу контроллера прерывани€, а при значении IEN = 0 - запрещает.

Ѕиты IPL определ€ют уровень приоритета запросов на прерывание от контроллера прерывани€ к центральному процессору. ”ровень 0 соответствует самому высокому при≠оритету, а уровень 7 - самому низкому. ќбычно дл€ нормальной работы механизма пре≠рывани€ устанавливают уровень приоритетности запросов от контроллера прерывани€ равным IPL = 4.

Ѕиты HP определ€ют, запрос на прерывание от какого модул€ будет иметь самый высокий приоритет при обработке его контроллером прерывани€. «начени€ этих битов могут динамически мен€тьс€ во врем€ работы. ќбычно самым приоритетным устанавли≠вают запрос с вектором прерывани€, равным 11111 (1F), от линии 15 порта —.

–егистры событий. ѕри работе в канале св€зи каждого канала ввода/вывода проис≠ходит достаточно много различных событий, каждое из которых может требовать преры≠вани€ и вмешательства центрального процессора дл€ анализа сложившейс€ ситуации.

“ак, в контроллере ћ–—860 регистрируетс€ до 13 событий, которые могут требовать вы≠ставлени€ запросов на прерывание (рис. 5.41, 5.42). Ќабор событий в канале св€зи зави≠сит от типа протокола, с которым работает SCC-контроллер. ƒл€ регистрации этих собы≠тий каждый SCC-канал имеет собственный регистр событий SCCE. ѕри регистрации некоторого событи€ в SCC-канале происходит установка бита, соответствующего этому событию, в регистре SCCE.

|

|

|

”становка хот€ бы одного бита событи€ в этом регистре приводит к немедленной установке бита прерывани€ от данного SCC-канала в регистре регистрации прерываний CIPR. ѕрерывание от SCC-канала не регистрируетс€, если содержимое регистра SCCE равно 0. —ледует помнить, что прерывание от SCC-канала в регистре CIPR будет обна≠ружено контроллером прерываний, только если оно разрешено в регистре маски CIMR.

ќбработка регистров событий всех каналов производитс€ независимо друг от друга. ѕри обработке прерывани€ от SCC-канала следует сразу же сбрасывать соответствую≠щий бит событи€ в регистре SCCE, чтобы контроллер прерывани€ мог зарегистрировать и обработать запросы на прерывани€ от других событий. —брос бита событи€ в регистре SCCE производитс€ записью в этот бит Ђ1ї.

ѕрерывание от любого событи€ может быть замаскировано в регистре маски SCCM. –асположение битов событий в регистрах SCCE и SCCM аналогично. ѕри включении питани€ и при системном сбросе регистр регистрации событий SCCE равен 0 и все пре≠рывани€ от событий, происход€щих в SCC-канале, замаскированы.

»зменение состо€ни€ на линии приема RXD, т. е. идет прием данных или идет прием IDLE-последовательностей холостого хода, регистрируетс€ в бите IDL. Ќо дл€ того, что≠бы узнать новое состо€ние сигналов на линии RXD, пользователь должен прочитать со≠держимое регистра статуса SCCS.

—обытие приема по линии RXD BREAK символа будет зарегистрировано в бите BRK регистра событий SCCE. —обытие начала приема по линии RXD BREAK последователь≠ности (при этом начало каждого нового BREAK-символа в последовательности отдельно не регистрирует) будет зарегистрировано в бите BRKs регистра событий SCCE. —обытие обнаружени€ на линии RXD конца BREAK-последовательности (получени€ первого Ђединичного бита) будет зарегестрирована в бите.

≈сли во врем€ передачи данных в SCC-канале возникла ошибка или потери  -сигнала, или незаполнени€ буфера (underrun), то это событие регистрируетс€ в бите “’≈:= 1. Transparent-контроллер регистрирует только возникновение ошибки underrun. ƒл€ SPI-контроллера ошибка underrun регистрируетс€ только в slave-режиме работы.

-сигнала, или незаполнени€ буфера (underrun), то это событие регистрируетс€ в бите “’≈:= 1. Transparent-контроллер регистрирует только возникновение ошибки underrun. ƒл€ SPI-контроллера ошибка underrun регистрируетс€ только в slave-режиме работы.

UART-контроллер провер€ет, €вл€етс€ ли каждый принимаемый символ контрольным служебным символом, сравнива€ формат символа с заданными форматами служебных символов. ≈сли некоторый символ распознан как контрольный, и в €чейке таблицы слу≠жебных символов дл€ него установлен бит R = 1, то символ не сохран€етс€ в буфере пам€ти, а только записываетс€ в регистр временного хранени€ RCCR, и это событие регистрируетс€ в бите CCR.

¬ BISYNC-контроллере прием по каналу св€зи одного из заранее определенных слу≠жебных символов, который записываетс€ в буфер данных в пам€ти, регистрируетс€ в ре≠гистре событий установкой бита RCH. ¬ Transparent-контроллере в этом бите регистри≠руетс€ событие приема одного символа данных.

≈сли корректный символ данных был прин€т во внутренний регистр SCC-канала, но RISC-контроллер не обнаружил свободного буфера BD дл€ передачи в него данных, то регистрируетс€ состо€ние зан€тости и устанавливаетс€ бит событи€ BSY:= 1. ѕри приеме символа в UART-контроллере свободный буфер должен быть подготовлен не позднее середины приема стоп-бита, иначе прин€тый символ будет отброшен из-за возникшего состо€ни€ зан€тости. ѕриемник при этом переходит в режим поиска следующего кадра данных (режим Ђохотыї).

≈сли при приеме данных текущий буфер заполнилс€, то устанавливаетс€ бит RX = 1 в регистре SCCE и текущий буфер закрываетс€. –егистраци€ этого событи€ происходит в UART-контроллере и в UART SMC-контроллере не раньше середины приема первого стоп-бита последнего символа в буфере. ¬ Transparent-контроллере событие регист≠рируетс€ не раньше чем через 10 периодов тактового сигнала после приема последнего бита последнего байта данных из текущего буфера.

—обытие завершени€ приема полного кадра данных регистрируетс€ установкой бита RXF. ¬ контроллерах HDLC и ASYNC HDLC этот бит устанавливаетс€ не раньше, чем через два периода тактового сигнала после окончани€ приема последнего бита, закры≠вающего флага кадра.

—обытие приема одного из буферов данных (но не полного кадра или не полного законченного сообщени€ в DDCMP-контроллере) регистрируетс€ установкой бита RXB в регистре событий, обычно это имеет место, если в слове состо€ни€ дескриптора текущего буфера приема установлен бит I = 1 (Interrupt), т. е. пользователь настроил контроллер на прерывание после приема этого буфера данных. ¬ контроллерах SPI и I2C это событие регистрируетс€, когда последний символ записан в буфер приемника, и этот буфер закрыт.

—обытие передачи буфера данных регистрируетс€ в бите “’. ≈сли в слове состо€ни€ текущего буфера UART-контроллера был установлен бит CR = 1, то бит “’ будет уста≠новлен в Ђ1ї, когда передатчик начнет передачу последнего символа из буфера FIFO. ≈сли же бит CR=0 или с UART-протоколом работает канал SMC, то бит “’ будет установ≠лен, когда последний символ из буфера данных будет передан в буфер FIFO передатчи≠ка SCC-канала. ¬ BISYNC-контроллере этот бит устанавливаетс€, когда началась пере≠дача последнего бита данных или пол€ BCS. ¬ контроллере SMC, работающем с прото≠колом Transparent, если переданный буфер не был последним буфером кадра, то уста≠новка бита “’ производитс€ при записи в буфер FIFO передатчика последнего байта из буфера данных, и пользователь должен будет ждать два периода передачи символа, чтобы быть уверенным, что передача прошла успешно. ≈сли же это был последний бу≠фер текущего кадра, то бит устанавливаетс€ не раньше, чем начнетс€ передача после≠днего символа кадра, и пользователь должен будет ждать один период передачи симво≠ла, чтобы быть уверенным, что передача прошла успешно.

≈сли текущий буфер данных был передан по каналу св€зи и если в слове состо€ни€ переданного буфера был установлен бит прерывани€ l(lnterrupt), то устанавливаетс€ бит “’¬. ≈сли это был не последний буфер кадра или контроллер настроен на работу с интерфейсом SPI, то установка бита “’¬ производитс€ при записи в буфер FIFO пере≠датчика последнего байта из буфера данных. ≈сли же это был последний буфер текуще≠го кадра, то бит устанавливаетс€ не раньше, чем начнетс€ передача предпоследнего бита последнего байта кадра. ¬ контроллерах HDLC и ASYNC HDLC это будет байт зак≠рывающего флага, в Transparent-контроллере - последний байт данных. ¬ контроллере BISYNC бит событи€ “’¬ устанавливаетс€ после передачи последнего бита кадра. ¬ контроллерах SPI и I2— бит событи€ “’¬ устанавливаетс€ после передачи последнего символа кадра в буфер FIFO передатчика, и пользователь должен будет ждать два пери≠ода передачи символа, чтобы быть уверенным, что передача прошла успешно.

Ѕит GLr устанавливаетс€, когда внутренн€€ схема DPLL блока обнаруживает Ђглюкї на линии тактового сигнала приемника.

Ѕит GLt устанавливаетс€, когда внутренн€€ схема DPLL блока обнаруживает Ђглюкї на линии тактового сигнала передатчика.

Ѕит ј¬ устанавливаетс€, когда блок автоподстройки частоты обнаруживает отличие в частоте передачи и в частоте работы приемника, и процессор должен произвести запись новых значений в регистры настройки BRG-генератора.

Ѕит GRA устанавливаетс€, когда передатчик, завершив передачу текущего буфера, закончил выполнение команды GRACEFULL STOP TRANSMIT. ≈сли передатчик в теку≠щий момент времени не вел передачу, то бит GRA устанавливаетс€ немедленно.

»зменение состо€ни€ (контроллер начинает или заканчивает прием символов фла≠га) на линии приема RXD контроллера HDLC регистрируетс€ в бите FLG. Ќо дл€ того чтобы узнать новое состо€ние сигналов на линии RXD, пользователь должен прочитать содержимое регистра статуса SCCS.

»зменение состо€ни€ несущей частоты, генерируемой DPLL-блоком, регистрируетс€ в бите DCC. Ќо дл€ того чтобы узнать новое состо€ние сигналов на линии RXD, пользо≠ватель должен прочитать содержимое регистра статуса SCCS.

≈сли SPI-контроллер, работа€ в режиме master, обнаружил активный сигнал SPISEL от другого master-устройства, то регистрируетс€ ошибка режима multimaster и устанав≠ливаетс€ бит MIME:= 1.

ѕрограммирование SCC-контроллера. Ѕуферные дескрипторы. ƒанные дл€ каждо≠го канала хран€тс€ в буферах данных. ƒл€ управлени€ обменом данными с пам€тью ис≠пользуютс€ параметры, хран€щиес€ в буферных дескрипторах в области parameter RAM в двухпортовой пам€ти (dual-port RAM). ћесторасположение BD в пам€ти дл€ каждого ка≠нала и распределение их между каналами определ€етс€ пользователем. Ќапример, дл€ передатчика канала SCC1 можно выделить 200 BD, а дл€ приемника - только 24 BD.

¬се буферные дескрипторы дл€ приема и передачи имеют единый стандартный фор≠мат в 4 слова (рис. 5.43), который одинаков дл€ всех используемых коммуникационных протоколов. ѕервое слово - регистр статуса и контрол€, формат которого зависит от конкретного выбранного протокола. ¬торое слово определ€ет длину данных или размер текущего буфера данных. ћаксимальный размер составл€ет (64 -1) байт. “ретье и чет≠вертое слова содержат 32-битный указатель на расположение первой €чейки буфера данных в пам€ти.

ƒл€ упор€дочени€ доступа к буферам в —–ћ все BD сгруппированы в таблицу, в кото≠рой хран€тс€ ссылки на расположение в пам€ти отдельных буферов (рис. 5.44). ѕользова≠тель может запрограммировать стартовый адрес таблицы указателей BD во внутренней пам€ти контроллера и количество BD в таблице дл€ передачи или дл€ приема дл€ каждого канала. ƒл€ ограничени€ числа BD в таблице в слове состо€ни€ последнего BD пользова≠тель устанавливает бит конца таблицы W:= 1. ќбнаружив этот бит, RISC-контроллер пере≠ходит на работу с первым дескриптором в таблице.

ѕри приеме и передаче данные из буферов пам€ти через SDMA-каналы передаютс€ во внутренние FIFO-буферы канала. аждый SCC-канал имеет по два SDMA-канала, один из них используетс€ при передаче данных в пам€ть, другой - при чтении данных из пам€≠ти. ќбычно каналы хран€т таблицу BD во внутренней двухпортовой пам€ти, а сами буфе≠ры данных - во внешней пам€ти. Ќо существует возможность хранить небольшие по размеру буферы данных, например, буферы каналов SPI и PIP, в неиспользуемых обла≠ст€х внутренней двухпортовой пам€ти. ѕри любом варианте размещени€ буферов дан≠ных доступа к ним будет осуществл€тьс€ по внутренней шине контроллера.

ѕри доступе к внешней пам€ти всегда используютс€ специальные функциональные коды FC1-FC3, которые определ€ют тип адресного пространства. ‘ункциональные коды дл€ каждого канала определены в €чейках RFCR (при приеме) и TFCR (при передаче), которые расположены в протокол независимой области parameter RAM выбранного ка≠нала. ѕользователь может измен€ть значени€ в этих регистрах, только когда уверен, что канал не обращаетс€ к внешней пам€ти в текущий момент времени.

ƒл€ некоторых протоколов поддерживаетс€ мультибуферна€ структура (кадр может за≠нимать несколько буферов). ѕри этом обычно в слове состо€ни€ BD бит F (First) указывает первый буфер кадра данных и бит L (Last) - последний буфер кадра. ≈сли кадр занимает несколько буферов, то не об€зательно предварительно готовить в пам€ти все буферы перед началом приема/передачи кадра. ћожно подготовить/освободить несколько буферов дл€ начала работы с кадром, а в ходе работы параллельно подготавливать следующие буферы и их дескрипторы. ќднако при такой конфигурации буферов возможно возникновение оши≠бок незаполнени€ (underrun), если центральный процессор не успеет подготовить дл€ пере≠датчика следующие буферы данных текущего сетевого кадра, или ошибок переполнени€ (overrun или busy error), если центральный процессор не успеет освободить новые буферы при приеме следующих частей кадра или нового кадра.

¬ыборка из таблицы BD выполн€етс€ по круговой системе. ѕосле включени€ канала в работу RISC-контроллер опрашивает первый BD в таблице. ≈сли буфер, соответствую≠щий этому дескриптору, готов, то он обрабатываетс€. ѕри обработке текущего буфера RISC-контроллер периодически опрашивает готовность следующего буфера. јлгоритм опроса зависит от конфигурации канала. ≈сли после обработки текущего буфера N сле≠дующий буфер N+1 не готов к обработке (не заполнен дл€ передачи или не освобожден дл€ приема), то возникает ошибка переполнени€ (overrun) при приеме и ошибка неза≠полнени€ (underrun) при передаче. ¬ этой ситуации RISC-контроллер будет ждать готовности N+1 буфера и не перейдет к проверке готовности N+2 буфера, даже если он уже готов к обработке.

≈сли следующий буфер готов к обработке, то RISC-контроллер приступает или к его передаче, или к его заполнению при приеме. ѕри переходе к новому буферу контроллер провер€ет в слове состо€ни€ текущего буфера бит последнего BD в таблице W (Wrap). ≈сли этот бит установлен, то после текущего буфера будет прове≠р€тьс€ готовность первого BD в таблице. ≈сли этот бит равен 0, то будет обрабатыватьс€ следующий по пор€дку BD в таблице.

аждый SCC-контроллер содержит собственный FIFO дл€ передачи данных и FIFO дл€ приема данных. Ќаличие дополнительной пам€ти в виде FIFO позвол€ет согласовы≠вать по скорости работы внутренние каналы передачи данных по шинам контроллера и скорости передачи данных по сети, а также позвол€ет избежать потерь данных из-за переполнени€ буферов каналов. ” ћ–—860 в —–ћ-модуле объем FIFO не зависит от используемого протокола и составл€ет по 16 байт дл€ приема и передачи у каналов SCC2-SCC4 и по 32 байта дл€ приема и дл€ передачи у канала SCC1. –азмер буферов FIFO каналов SMC, а также портов SPI и I2C составл€ет по два символа дл€ приема и передачи. ¬ контроллере ћ–—860 порт PIP имеет FIFO приема и передачи размером по одному символу каждый.

ѕри передаче данных бит готовности буфера дл€ передачи R:= 1 (Ready) устанав≠ливаетс€ центральным процессором. ƒанные из этого буфера RISC-контроллер пере≠дает в буфер FIFO канала передачи. ѕо окончании передачи всех данных из буфера RISC-контроллер сбрасывает бит R:= 0. “аким образом, дважды содержимое одного буфера в нормальном режиме работы не передаетс€. Ќо у —–ћ существует одно ис≠ключение. ¬ слове состо€ни€ BD пользователь может установить бит повторной пере≠дачи —ћ:= 1 (Continuous Mode), при этом если RISC-контроллер снова через цикл оп≠роса обратитс€ к этому буферу, то его содержимое будет повторно передаватьс€, даже если бит готовности R = 0.

¬ режиме приема центральный процессор освобождает буфер дл€ приема новых данных и в слове состо€ни€ BD этих буферов устанавливает бит пустого буфера ≈:= 1 (Empty). ѕри приеме данных RISC-контроллер находит пустой буфер и записывает в него данные из буфера FIFO канала приемника. «аполненный буфер закрываетс€, а RISC-контроллер устанавливает бит зан€того буфера ≈:= 0 и переходит к заполнению очеред≠ного буфера. ≈сли текущий буфер заполнен, а следующий еще не освобожден централь≠ным процессором, то генерируетс€ ошибка зан€тости (busy error).

“аким образом, при приеме данных буфер считаетс€ зан€тым, пока центральный про≠цессор не обработает его данные и не установит бит незан€тости буфера ≈:= 1. ¬ нор≠мальном режиме RISC-контроллер не будет записывать новые данные в этот буфер, пока он не будет отмечен как пустой. Ќо в —–ћ пользователь может установить в слове состо€ни€ этого буфера бит повторной записи —ћ:= 1 (Continuous Mode), и RISC-кон≠троллер при повторном обращении к этому буферу будет записывать новые данные по≠верх старых, даже если буфер отмечен как зан€тый ≈ = 0.

огда буфер весь заполнен при приеме или весь передан при передаче и в его слове состо€ни€ установлен бит прерывани€ I = 1, RISC-контроллер посылает прерывание цен≠тральному процессору, чтобы он мог обрабатывать данные этого буфера при приеме или заполн€ть буфер новыми данными при передаче. ѕрерывание может быть также передано CPU, если при работе с буфером произошла одна из возможных ошибок. Ѕо≠лее точна€ причина ошибки будет установлена в регистре событий (events) SCC-канала и указана в слове состо€ни€ текущего буфера.

—уществует исключение в правилах обработки буфера при передаче в —–ћ. ѕри нор≠мальном алгоритме опроса готовности буфера к передаче RISC-контроллер анализиру≠ет бит готовности буфера R каждые 8-32 периода тактового сигнала. Ќо пользователь может заставить RISC-контроллер начать обработку буфера немедленно, не ожида€, когда наступит врем€ нового опроса готовности бита R у данного буфера. ƒл€ чего пользова≠тель должен установить бит R:= 1 в слове состо€ни€ BD этого буфера и установить бит TOD:= 1 в регистре TODR канала SCC (рис. 5.45). ”становка бита TOD:= 1 повышает приоритет текущего буфера и заставл€ет RISC-контроллер начать немедленно его обра≠ботку. ѕри нормальном алгоритме опроса готовности буфера бит TOD = 0.

ћеханизм программировани€ бита TOD позвол€ет повысить интенсивность передачи данных и часто примен€етс€ в протоколах, которые имеют временные ограничени€ на максимальный интервал между кадрами. ќднако использование такого механизма мо≠жет оказать негативное вли€ние на передачу данных, которые уже наход€тс€ в буфере FIFO передатчика. ѕоэтому рекомендуетс€ примен€ть программирование регистра TODR канала SCC, только когда буфер данных уже подготовлен и нет передачи на канале в текущий момент времени. ”становка бита TOD:= 1 в новом буфере не даст желаемого результата, если в текущий момент времени ведетс€ передача из другого буфера, по≠скольку вначале будет закончена передача из старого буфера, а затем будет опраши≠ватьс€ бит готовности нового буфера.

‘орматы слова состо€ни€ буферного дескриптора. ‘орматы слова состо€ни€ бу≠ферного дескриптора приемника дл€ различных коммуникационных протоколов приве≠дены в табл. 5.28, 5.29.

ѕри приеме биты с 15-го по 12-й и бит 9 заполн€ютс€ пользователем перед началом работы с контроллером. ќни содержат информацию об общих правилах обработки бу≠фера при приеме. Ѕиты с 11-го по 0-й часто называют битами статуса прин€того или переданного кадра. Ѕиты 11 и 10 обычно заполн€ютс€ при приеме и определ€ют тип записанной в буфер информации. ¬ биты с 8-го по 2-й записываютс€ коды ошибок, возникших при приеме в кадре данных, и завис€щие от типа коммуникационного прото≠кола. ¬ биты 1 и 0 записываетс€ код ошибки, возникшей при

приеме в канале св€зи или аппаратуре.

ѕри передаче биты с 15-го по 1-й заполн€ютс€ пользователем перед началом работы с контроллером. ќни содержат информацию об общих правилах обработки буфера при передаче и правилах передачи данных, которые завис€т от типа коммуникационного про≠токола, а также определ€ют тип передаваемой в буфере информации ¬ биты 1 и 0 запи≠сываетс€ код ошибки, возникшей при передаче в канале св€зи или аппаратуре.

Ќиже перечислены биты общего назначени€, которые определ€ют правила обработ≠ки и состо€ние текущего буфера BD.

ХЅит пустого буфера ≈ (Empty) устанавливает в Ђ1ї центральный процессор после того, как обработает данные из этого буфера, и буфер можно использовать дл€ приема новых данных. Ѕит ≈ = 0 записывает в слово состо€ни€ RISC-контроллер после заполнени€ буфера данными из сети.

ХЅит заполненного буфера R (Ready) устанавливает центральный процессор после того, как закончит подготовку в буфере данных дл€ передачи по сети. Ётот бит по≠сто€нно анализируетс€ RISC-контроллером дл€ начала передачи новых данных и

сбрасываетс€ (R = 0) после передачи всех данных из этого буфера.

ХЅит последнего буфера W (Wrap), равный 1, сообщает RISC-контроллеру, что текущий буфер - это последний буфер, выделенный этому каналу ввода/вывода, и после его обработки необходимо переходить дл€ работы к первому элементу BD в таблице буферных дескрипторов.

ХЅит прерывани€ I (Interrupt), равный 1, вызывает установку в регистре событий данного канала ввода/вывода бита запроса на прерывание RX или RXB при полном запол≠нении буфера при приеме данных и бита запроса на прерывание “’ или “’¬ при

передаче всех данных из буфера в сеть.

ХЅит продолжени€ работы CM (Continues Mode), равный 1, определ€ет, что содержимое этого буфера может быть передано в сеть, даже если не установлен бит готовности буфера R = 0, или что в этот буфер можно записывать данные при приеме,

даже если не установлен бит пустого буфера ≈ = 0.

—ледующа€ перечисленна€ группа битов регистрирует возникновение аппаратных оши≠бок при работе с любым из коммуникационных протоколов и заполн€етс€ после завер≠шени€ обработки текущего буфера.

ХЅит —“ (CIS Lost), равный 1, регистрирует ошибку, св€занную с потерей сигнала  = 0 при передаче данных из текущего буфера.

= 0 при передаче данных из текущего буфера.

ХЅит CD (Carrier Detect Lost), равный 1, регистрирует ошибку, св€занную с потерей сигнала  = 0 при приеме данных в этот буфер.

= 0 при приеме данных в этот буфер.

ХЅит переполнени€ буфера OV (Overrun), равный 1, регистрирует ошибку, св€занную с переполнением буфера FIFO приемника канала ввода/вывода из-за несогласовани€ скорости работы сети и скорости работы каналов SDMA, по которым данные из FIFO пересылаютс€ в пам€ть.

ХЅит незаполнени€ буфера UN (Underrun), равный 1, регистрирует ошибку, котора€ возникает при передаче кадра данных, занимающего несколько буферов, когда передатчик передал всю информацию из буфера FIFO, а новые данные дл€ передачи еще не поступили по каналам SDMA.

—ледующий набор битов определ€ет содержимое буферов.

ХЅит контрольного символа — (Control), равный 1, указывает, что последний прин€тый в буфер символ €вл€етс€ контрольным символом.

Х≈сли бит ¬ (BCS received) равен 1, то последний прин€тый байт в буфере данных содержит контрольную сумму блока (BCS) или части кадра данных.

ХЅит адреса A (Address), равный 1, при передаче указывает, что все данные из буфера должны быть переданы как адреса, а при приеме указывает, что первый прин€тый символ в буфере - это адрес.

ХЅит совпадени€ адреса AM (Address Match) указывает, содержимому какого адресного регистра: UADD1 (если бит AM = 1) или UADD2 (если бит AM = 0) равен адрес в прин€≠том пакете.

ХЅиты первого F (First) и последнего L (Last) буферов используютс€ в протоколах, где кадр данных может занимать несколько буферов, дл€ указани€ первого (если битF = 1) и последнего буфера кадра (если бит 1 = 1). ”казание первого и последнего буферов в кадре необходимо дл€ организации прерываний при начале и конце об≠работки всего кадра данных.

Х≈сли бит ¬ (BCS Enable) равен 1, то при работе с протоколом BISYNC содержимое буфера участвует в вычислении контрольной суммы BCS.

≈сли бит ¬ = 0, то содержи≠мое буфера исключаетс€ из подсчета контрольной суммы.

ƒалее перечислена группа битов, предназначенных дл€ указани€ ошибок, обнару≠женных при приеме кадра данных.

Х≈сли бит BR (Break received) равен 1, то при приеме данных в текущий буфер была получена BREAK-последовательность.

Х≈сли бит FR (Frame Error) равен 1, то при приеме кадра данных была обнаружена ошибка в формате кадра. Ќапример, UART-контроллер прин€л кадр без стоп-битов.

Х≈сли бит PR (Parity Error) равен 1, то при приеме кадра данных была обнаружена ошибка проверки четности/нечетности.

Х≈сли бит ID (IDLE received) равен 1, то текущий буфер был закрыт при получении максимально возможного запрограммированного числа IDLE-символов Ђхолостого ходаї.

Х≈сли бит DE (DPLL error) равен 1, то при приеме данных в буфер блоком DPLL была обнаружена ошибка в кодировании данных. Ќапример, при заданном способе кодировани€ данных перепад сигнала произошел не в центре битового интервала, а на его крае. ќбнаружение этой ошибки дополнительно позвол€ет избежать потери данных из-за сбо€ в синхронизации приемника и передатчика.

Х≈сли бит LG (Lenght Violation) равен 1, то прин€т кадр данных, длина которого превышает максимально допустимую запрограммированную дл€ данного канала ввода/вывода длину принимаемых кадров. ѕри этом в буфер будет записана только часть кад≠ра, размер которой равен установленному пределу.

Х≈сли бит ј¬ (Abort received) равен 1, то при приеме кадра в буфер была получена ABORT-последовательность минимум из семи последовательных единиц.

Х≈сли бит NO (Nonoctet Aligned Frame) равен 1, то прин€т кадр данных, длина которого не кратна 8 битам.

Х≈сли бит CR (CRC Error) равен 1, то получен кадр с ошибкой при проверке пол€ конт≠рольной суммы кадра CRC или пол€ контрольной суммы части кадра (блока) BCR.

Х≈сли бит SH (Short Frame) равен 1, то прин€т кадр, длина которого меньше минимальной длины кадра, установленной дл€ данного канала ввода/вывода.

Х≈сли бит CL (Collision) равен 1, то текущий буфер был закрыт из-за обнаружени€ коллизии при приеме данных.

Х≈сли бит ME (Multimaster Error) равен 1, то текущий буфер был закрыт, поскольку контроллер SPI, работа€ в текущий момент времени как master-станци€, обнаружил сигнал SPISEL от другой станции, действующей в таком же режиме.

Х≈сли бит DL (OLE character error) равен 1, то BISYNC-контроллер, работа€ в прозрачном режиме, прин€л служебный символ DLE, но следующий символ не был ни одним из установленных контрольных символов.

ќпишем набор битов, предназначенных дл€ управлени€ передачей данных из теку≠щего буфера.

Х≈сли бит – (Preamble) равен 1, то перед передачей в канал св€зи содержимого буфера в канал передаетс€ символ преамбулы, котора€ служит разделителем между передачей двух буферов и обеспечивает синхронизацию приемника и передатчика.

Х≈сли бит NS (No Stop Bit) равен 1, то UART-контроллер передает данные из этого буфера, не добавл€€ к ним единичные стоп-биты.

Х≈сли бит CR (CIS Report) равен 1, то при передаче двух соседних буферов данных между ними будет передана комбинаци€ из трех битов idle и сброшен сигнал  . ѕотер€ этого сигнала будет нормально зафиксирована в бите —“ слова состо€ни€ этого буфера BD. ≈сли бит CR = 0, то передача двух соседних буферов ведетс€ без пауз и сигнал

. ѕотер€ этого сигнала будет нормально зафиксирована в бите —“ слова состо€ни€ этого буфера BD. ≈сли бит CR = 0, то передача двух соседних буферов ведетс€ без пауз и сигнал  может не сбрасыватьс€, таким образом, бит —“ может быть не установлен, как положено по окончании передачи данного буфера.

может не сбрасыватьс€, таким образом, бит —“ может быть не установлен, как положено по окончании передачи данного буфера.

Х≈сли бит “— (“х CRC) равен 1 и если в BD установлен бит 1_=1, то после передачи последнего байта данных кадра контроллер передает в канал контрольную сумму кадра. ≈сли бит “— = 0, то контрольна€ сумма не передаетс€. ѕри этом контроллер HDLC может после передачи всех данных передавать закрывающий флаг. ќтсутствие в кадре данных пол€ контрольной суммы может использоватьс€ дл€ тестировани€ работы приемника.

`Х≈сли бит “¬ (“х BCS) равен 1 и если в BD установлен бит L=1, то после передачи последнего байта данных кадра BISYNC-контроллер передает в канал контрольную сумму блока. ≈сли бит “¬ = 0, то контрольна€ сумма не передаетс€. ѕри этом контроллер может после передачи всех данных передавать символы синхронизации или символы idle.

Х≈сли бит BCR (BCS Reset) равен 1, то перед передачей текущего буфера сбрасывает≠с€ счетчик контрол€ BCS суммы блока. ќбычно это выполн€етс€ при передаче новогоблока данных текущего кадра из нового буфера. ≈сли бит равен 0, то сброс счетчиков не производитс€.

Х≈сли бит TD (Transmit DLE) равен 1, то перед передачей этого буфера данных BISYNC-контроллер передает в канал служебный символ DLE.

Х≈сли бит TR (Transparent Mode) равен 1, то BISYNC-контроллер после передачи текущего буфера переходит в режим прозрачной передачи. ѕри возникновении ошибки незаполнени€ буфера underrun контроллер посылает в канал пары символов DLE-SYNC дл€ поддержани€ синхронизации в канале св€зи. ≈сли бит TR = 0, то после передачи текущего буфера контроллер переходит в нормальный режим работы и при возникновении ошибки underrun передает в канал символы синхронизации SYNC.

Х≈сли бит PAD (Short Frame Padding) равен 1 и в слове состо€ни€ буфера установлен бит L = 1, то Ethernet-контроллер после передачи всех данных текущего кадра допол≠н€ет короткие кадры заполнителем PAD, пока длина кадра не станет равной минимальной установленной длине кадра дл€ данного контроллера. ≈сли бит PAD = 0 и бит L = 1, то добавление заполнител€ не производитс€.

—ледующие перечисленные биты устанавливаютс€ Ethernet-контроллером после передачи текущего буфера данных,

ХЅит DEF (Defer Indication) устанавливаетс€, если при передаче текущего кадра была обнаружена коллизи€.

ХЅит Ќ¬ (Heartbeat) устанавливаетс€, если коллизи€ не произошла в течение 20 периодов тактового сигнала передатчика после завершени€ текущей передачи.

ХЅит LC (Late Collision) устанавливаетс€, если коллизи€ произошла после передачи определенного в контроллере (56 или 64) числа байтов. ѕередача прерываетс€. ћинимальна€ длина кадра в Ethernet-протоколе равна 64 байтам, поэтому после успеш≠ной, без коллизий, передачи такого кадра возможно возникновение поздней коллизии,котора€ характерна дл€ прот€женных сетей и св€зана со временем распространени€ сигналов по кабелю и их задержки в повторител€х.

ХЅит RL (Retransmission Limit) устанавливаетс€, если контроллер превысил установленное число попыток повторного выхода в сеть после очередного обнаружени€ коллизии.ќбычно число попыток равно 16.

Х„етыре бита RC (Retry Count) хран€т число повторных попыток выхода в сеть при возникновении коллизии, которые были сделаны до проведени€ успешной передачи кадра.

ХЅит CSL (Carrier Sence Lost) устанавливаетс€, если при передаче кадра была обнаружена потер€ несущей частоты, т. е. нарушена кодировка данных, например, при ман≠честерском кодировании.

ѕри работе с многоканальным QMC-протоколом вместе с основными стандартными битами в слове состо€ни€ буферных дескрипторов используютс€ дополнительные биты.

Х—пециальный бит UB (User Bit) используетс€ при работе с QMC-протоколом. ѕользо≠ватель самосто€тельно определ€ет назначение этого бита, который может служить, например, флагом обмена между протоколами верхних уровней управлени€, пока буфер данных обрабатываетс€ в процессоре. оммуникационный процессор не работает с этим битом.

Хѕри передаче биты PAD определ€ют число символов IDLE (0xFF) или FLAG (0x7E),которые передаютс€ после закрывающего флага. “ип символа определ€етс€ значением бита IDLM в регистре режима CHAMR контроллера QMC. ѕрерывание “’¬ будет выработано только после передачи заданного числа этих символов. ≈сли биты PAD = 0,то прерывание будет выработано сразу после передачи закрывающего флага. „исло

символов PAD зависит от размера €чейки буфера FIFO и числа занимаемых временных

слотов, например, число PAD = (размер €чейки FIFO/число временных слотов). “аким

образом, после кадра данных передаетс€ (PAD+1) число символов флага.

ѕротокол-независима€ часть пам€ти параметров. аждый SCC-канал имеет свою соб≠ственную пам€ть параметров (parameter RAM), котора€ состоит из двух частей. ¬ первой части (протокол-независима€ часть) хран€тс€ параметры настройки SCC-канала, общие дл€ всех каналов. ¬о второй (протокол-ориентированной) хран€тс€ параметры настройки SCC-канала на работу с определенным протоколом. —одержимое области parameter RAM может быть прочитано пользователем и CPU в любое врем€. ѕараметры, которые должны быть проинициализированы пользователем, необходимо записать до момента включени€ SCC-канала в работу.

ƒл€ каждого SCC-канала во внутренней двухпортовой пам€ти выделена сво€ область адресного пространства. Ќачальные адреса пам€ти, отведенной дл€ каждого канала, фик≠сированы и известны пользователю. ¬ контроллере ћ–—860 (табл. 5.30) смещение (offset) канала parameter RAM от базового адреса SCC base address составл€ет 0 байт.

¬нутри область parameter RAM разделена на две части: протокол-независимую (сме≠щение SCC base+OxOO) и протокол-ориентированную независимую (смещение SCC base+0х30). ‘ормат протокол-независимой пам€ти приведен в табл. 5.31.

ѕеременные RBASE и TBASE содержат базовый адрес начала таблицы буферов дескрипторов дл€ приема (RxBD) и дл€ передачи (TxBD). ¬ —–ћ таблицы BD могут распола≠гатьс€ в любом месте в двухпортовой пам€ти и иметь размер, который определ€ет сам пользователь (только установка бита W = 1 в слове состо€ни€ BD закрывает таблицу BD). ѕеременные RBASE и TBASE должны содержать значени€, кратные 8.

аждый SCC-канал имеет переменную MRBLR, определ€ющую максимальное число байт, которые канал может записать в буфер приема перед переходом на следующий пустой буфер. анал может записать в буфер меньшее число байт, например, при закры≠тии буфера из-за ошибки приема, но никогда не сможет записать больше данных, чем указано в MRBLR. ѕоэтому пользователь должен подготавливать буферы приема разме≠ром не меньше, чем величина, указанна€ в байтах €чейки MRBLR. »зменени€, которые пользователь вносит в переменную MRBLR во врем€ работы канала, вступают в силу только тогда, когда SCC-канал переходит к обработке нового буфера BD, т. е. на работу текущего BD изменени€ не оказывают вли€ни€.

–азмер буфера при передаче может быть любым. ќбщее число байт в буфере дл€ передачи указываетс€ в поле длины буфера во втором слове BD.

ѕеременные RBPTR и TBPTR указывают адреса текущих обрабатываемых буферов BD во внутренней пам€ти. ѕосле системного сброса или достижени€ конца таблицы в эти переменные записываютс€ значени€ RBASE и TBASE соответственно, а далее переход к следующему буферу означает смещени€ +0x08 (например, RBPTR: = RBPTR + 0x08).

–егистры функциональных кодов RFCR и TFCR имеют одинаковый формат (рис. 5.46) и определ€ют функциональные коды дл€ приемников и передатчиков SCC. ¬ битах ј“«-ј“1 содержитс€ код, который будет выставлен на внешних контактах функциональных кодов, чтобы идентифицировать тип доступа к пам€ти, когда SDMA-канал контроллера обратитс€ к буферам данных, расположенным в пам€ти. ≈сли в этих битах записан код 1, то канал SDMA обращаетс€ к пам€ти в режиме пр€мого доступа.

Ѕиты ¬ќ регистров RFCR и TFCR (табл. 5.31) определ€ют пор€док передачи байтов в словах при обмене по сети. ≈сли пользователь изменил значение этих битов при пере≠даче текущего кадра, то это изменение окажет вли€ние только при передаче следующе≠го кадра данных в протоколах Ethernet, HDLC и Transparent или следующего буфера дан≠ных дл€ других протоколов.

ќстальные параметры используютс€ только RISC-контроллером и могут потребоватьс€ пользователю лишь при отладке. ячейки RX-указатель, “’-указатель заполн€ютс€ дл€ SDMA-канала и указывают адрес следующей €чейки данных в буфере данных, котора€ должна быть записана/прочитана в режиме SDMA. —четчики Rx и “х - это вычитающие счетчики, значение которых уменьшаетс€ на единицу при передаче каждого байта по каналу SDMA. —четчик Rx инициализируетс€ значением MLBR, а счетчик “х - значением из пол€ длины BD передачи.

»нициализаци€ SCC-каналов. ѕосле включени€ питани€ все регистры настроек SCC-контроллера наход€тс€ в исходном состо€нии (состо€нии после системного сброса) и дл€ того, чтобы настроить SCC-канал дл€ приема/передачи информации, пользователь должен записать в эти регистры коды настроек. ќсновные этапы программировани€ ре≠гистров настроек каналов ввода/вывода приведены ниже.

1.Ќастроить регистры параллельных портов ввода/вывода, чтобы SCC мог использовать внешние контакты (выводы портов) дл€ передачи/приема информации.

¬ регистре PxPAR указываетс€, какие линии порта ввода/вывода будут использованы дл€ работы SCC-канала. ¬ регистре PxDIR указываетс€ назначение выбранной линии ввода (input) или вывода (output). ¬ регистре PxODR указываетс€ тип выходного каскада выбранной линии, например, выхода с открытым коллектором, с открытым истоком, с Z-состо€нием.

ƒополнительно дл€ параллельного порта — в его регистрах PCPAR, PCDIR, PCODR производитс€ настройка выводов  и

и  дл€ работы или как линии портов с возмож≠ностью регистрации сигналов по прерыванию, или как дополнительных модемных сигна≠лов дл€ SCC-канала.

дл€ работы или как линии портов с возмож≠ностью регистрации сигналов по прерыванию, или как дополнительных модемных сигна≠лов дл€ SCC-канала.

2.≈сли SCC-канал будет работать в режиме временного мультиплексировани€ с TSA,то необходимо произвести настройку регистров последовательного интерфейса SI. ¬ регистре SIGMR производитс€ выбор рабочего канала TDMa или TDMb и режимов его рабо≠ты при операци€х маршрутизации.

3.¬ регистре SIMODE производитс€ настройка рабочего или тестового режима работы каждого TDM-канала, определ€етс€, по каким фронтам и каких сигналов будут произ≠водитьс€ действи€ с данными, а также производитс€ настройка режимов работы SMC-контроллеров и выбор их источников тактировани€.

4.≈сли канал TDM будет работать с пам€тью маршрутизации, то проводитс€ настройка режимов работы €чеек пам€ти в SIRAM и настройка регистра команд SICMR.

5.≈сли SCC-контроллер будет работать в режиме NMSI, то проводитс€ выбор источников тактировани€ приемника и передатчика в регистре SICR.

6.¬ регистре конфигурации GSMR следует произвести настройки режимов работы блока кодировани€ и декодировани€ сигналов DPLL, выбрать 16/32-разр€дную сумму, настроить режимы работы с внешними сигналами  ,

,  ,

,  , определить размер FIFO-буфера дл€ временного хранени€ данных, выбрать режим кодировани€ данных и формат преамбулы. ¬ этом регистре производитс€ также выбор режима работы или тестового режима работы SCC-канала, но биты включени€ приемника и передатчика ENT и ENR пока не устанавливаютс€ в активное состо€ние.

, определить размер FIFO-буфера дл€ временного хранени€ данных, выбрать режим кодировани€ данных и формат преамбулы. ¬ этом регистре производитс€ также выбор режима работы или тестового режима работы SCC-канала, но биты включени€ приемника и передатчика ENT и ENR пока не устанавливаютс€ в активное состо€ние.

7.ƒл€ выбранного коммуникационного протокола необходимо провести настройку его режимов работы в регистре режима PSMR.

8.≈сли необходимо, дл€ выбранного протокола в регистре синхронизации DSR пользователь может определить формат SYNC-символов синхронизации.

9.ѕроизвести инициализацию параметров в протокол-независимой пам€ти параметров SCC-контроллера и в протокол-ориентированной пам€ти параметров в соответствии с особенност€ми выбранного протокола канального уровн€.

10.ќчистить все биты регистрации событий в регистре событий SCC-канала SCCE, дл€ того чтобы после включени€ канала в работу регистрировать событи€, которые бу≠дут происходить при приеме/передаче кадров данных.

11.ѕри необходимости замаскировать в регистре маски SCC-канала SCCM регистрацию прерываний при возникновении некоторых событий.

12.¬ регистре CICR требуетс€ установить приоритет запросов на прерывание от SCC-канала. ѕри необходимости запросы на прерывание от других источников можно отклю≠чить, уменьшив их приоритет до 0.

13.–азрешить прерывание от SCC-каналов в регистре маски CIMR-контроллера пре≠рываний.

14.ѕри необходимости в регистре регистрации прерывани€ CIPR можно сбросить зарегистрированные в текущий момент времени прерывани€ от других источников.

15.”становить биты ENT = ENR= 1 в регистре GSMR, разрешив работу передатчика и приемника выбранного SCC-канала.

16.ѕри работе с SCC-каналами пользователь может в любой момент времени произвести модификацию параметров канала, например, настроить его на работу с другой частотой или с другим коммуникационным протоколом. ƒл€ этого канал должен быть выключен из работы, а затем снова включен. ѕри этом текущие буферы данных, с которыми работает канал, закрываютс€, и после возобновлени€ работы канал будет рабо≠тать с другими буферами.

ѕоследовательность инициализации параметров приемника SCC-канала следующа€.

1.—бросить бит работоспособности (разрешени€ работы) приемника ENR= 0 в регистре GSMR. ѕрием будет немедленно прерван и приемник установлен в нормальное состо€ние.

2.ѕроизвести модификацию пам€ти параметров и регистров SCC-канала. ѕри желании пользователь может просто сбросить все параметры в исходное состо€ние, передав контроллеру команду INIT RX PARAMETERS.

3.≈сли необходимо, подготовить приемник канала к началу работы и поиску нового кадра данных, который будет записыватьс€ в новый буфер. Ёти действи€ выполн€ютс€ при передаче контроллеру команды ENTER HUNT MODE. ѕосле возобновлени€ приема данные будут записыватьс€ в буфер BD, адрес которого указан в €чейке RBPTR пам€ти параметров SCC-канала, но только если этот буфер помечен как пустой (бит ≈ = 1). оманда ENTER HUNT MODE об€зательно передаетс€, если на предыдущем этапе пользо≠ватель самосто€тельно настраивал новые параметры SCC-контроллера и не использовал команду INIT RX PARAMETERS.

4.”становить бит разрешени€ приема ENR:= 1 в регистре GSMR, разрешив контроллеру начать прием информации из канала св€зи.

ѕоследовательность инициализации параметров передатчика SCC-канала следующа€.

1.≈сли контроллер в текущий момент времени выполн€ет передачу кадра данных, то предварительно требуетс€ передать ему команду STOP TRANSMIT дл€ прерывани€ процесса передачи.

2.—бросить бит работоспособности (разрешени€ работы) передатчика ENT = 0 в регистре GSMR_L. ѕередатчик будет установлен в начальное состо€ние.

3.ѕроизвести модификацию пам€ти параметров и регистров SCC-канала. ѕри жела≠нии пользователь может просто сбросить все параметры в исходное состо€ние, передав контроллеру команду INIT TX PARAMETERS. ≈сли команда INIT TX PARAMETERS не используетс€, то необходимо передать команду RESTART TRANSMIT.

4.”становить бит разрешени€ передачи ENT:= 1 в регистре GSMR_L, разрешив контроллеру начать передачу в сеть информации из буфера данных, адрес которого указан в €чейке TBPTR.

≈сли пользователь решил изменить протокол, с которым работает в текущий момент времени SCC-контроллер, то он должен выполнить следующие шаги.

1.—бросить биты разрешени€ работы приемника и передатчика SCC-канала ENT = ENR = 0.

2.ѕередать каналу команду инициализации всех параметров приемника и передат≠чика в исходное состо€ние INIT TX and RX PARAMETERS. ѕроизвести настройку регистра GSMR и пам€ти параметров на работу с другим протоколом.

3.”становить биты ENR = ENT:= 1, разрешив SCC-контроллеру работать с новым протоколом.

¬ коммуникационных контроллерах реализовано полезное решение. огда биты ENR и ENT некоторого SCC-контроллера равны нулю, то этот контролл