КАНАЛОВ

Контроллер І2С. Контроллер I2C введен в состав СРМ-модуля коммуникационного контроллера МРС860 и позволяет ему обмениваться данными с другими І2С -устройствами, такими как микроконтроллеры, EEPROM, устройства реального времени, аналого-цифровые преобразователи.

I2C - это синхронный, двунаправленный интерфейс (линия данных SDA и линия тактовых сигналов SCL), который может работать в режимах master-slave и multimaster. Выбор режима выполняется в регистре команд I2COM (рис. 5.56). Если бит M/S = 0, то контроллер работает как slave-устройство, если M/S = 1, то - как master.

Оба вывода SCL и SDA являются двунаправленными и подсоединяются через резистор к положительному напряжению. Таким образом, поскольку контроллер имеет выводы типа «открытый исток» (open drain), то они могут быть объединены в единую шину для работы в конфигурации multimaster. Когда на Ι2С-шине нет передачи, то линии SCL и SDA находятся в пассивном «1» состоянии.

Настройка режимов работы І2С -контроллера производится в регистре режима I2MOD (рис. 5.57).

Включение контроллера в работу производится установкой бита EN:= 1. В выключенном режиме (бит EN = 0) контроллер работает в режиме пониженного энергопотребления.

Тактирование приемника и передатчика PC-контроллера выполняется одной частотой. Если устройство работает в режиме slave, то тактовые сигналы поступают от внешнего источника по линии SCL. Источником тактового сигнала для master-устройства является собственный внутренний генератор BRG. Тактовый сигнал BRGCLK для работы BRG-генератора поступает от системного синтезатора частоты и может быть предварительно изменен. Биты PDIV определяют коэффициент предварительного деления входной частоты (табл. 5.36).

BRG-генератор І2С -контроллера может также изменять входную частоту генератора. Коэффициент деления частоты задается пользователем в режиме I2BRG и рассчитывается как 2х (I2BRG+3). На выходе BRG-генератора тактовый сигнал представляет собой меандр. При системной частоте 25 МГц максимальная скорость передачи данных может достигать 520 КГц (BRGCLK/(4x2x(0+3)= BRGCLK/48),

Поскольку І2С -интерфейс используется для связи устройств на одной плате, в одном приборе, то на линии тактового сигнала может оказывать влияние посторонний шум. Установка бита FLT:= 1 позволяет пропустить тактовый сигнал через цифровой фильтр, чтобы убрать возможные наводки из-за шумов.

Бит REVD задает порядок передачи битов при обмене символами. Если бит REVD = 0, то первым передается SLB. Если REVD = 1, то первым передается MSB, этот режим является рабочим для контроллеров фирмы «Motorola».

Бит GCD в регистре I2MOD определяет, как должен вести себя приемник при получении общего запроса от master-станции. Если бит GCD = 1, то никакие действия не производятся. Если бит GCD = 0, то приемник посылает подтверждение на адрес общего вызова (general call address).

В контроллере МРС860 параметры І2С -контроллера хранятся на 1 -и странице памяти параметров (parameter RAM) со смещением + 0x1 С80 от начала двухпортовой памяти. Структура и состав памяти параметров І2С -контроллера совпадают со структурой таблицы протокол-независимых параметров (см. табл. 5.30). Отличие заключается только в том, что отсутствуют две последние ячейки таблицы со смещениями I2C base+28 и I2C base+2C.

Данные для І2С -канала хранятся в буферах памяти, которые организованы в таблицу TxBD (передачи) и RxBD (приема). Принцип организации таблицы аналогичен таблицам буферов для SCC-каналов ввода/вывода. Стартовый адрес таблиц в памяти контроллера хранится в ячейках RBASE и TBASE памяти параметров І2С -контроллера. Пользователь может ограничить число буферов в таблице, установив бит W:= 1 в слове состояния последнего необходимого буферного дескриптора. При подготовке обмена данными центральный процессор готовит данные для передачи в буферах памяти, заполняет соответствующие буферные дескрипторы и устанавливает в их слове состояния бит готовности к передаче R:= 1, а также заранее подготавливает буферы для приема данных.

Режимы работы І2С -контроллера. В режиме master І2С контроллер управляет обменом данными со slave-устройствами. Для этого он передает slave-устройству специальное сообщение, которое определяет режим работы (чтение или запись). Если это операция чтения, то после передачи первого сообщения направление передачи по линии SDA меняется, и передавать будет slave-устройство.

Для начала обмена сообщениями master-устройство должно подготовить данные для передачи в буферах TxBD, установив бит готовности R:= 1 в слове состояния буферного дескриптора, а также подготовить буферы приема RxBD. Затем центральный процессор должен установить бит STR:= 1 в регистре команд I2COM. Данные будут передаваться после того, как они будут загружены в буфер FIFO передатчика по SDMA-каналам из памяти, и после того, как І2С -шина будет свободна. Размер буфера FIFO приемника и передатчика установлен равным двум символам. При передаче MSB передается первым.

При начале передачи І2С -контроллер выставляет start-условия (адрес slave-устройства) на линии SDA и тактовые импульсы, число которых соответствует числу передаваемых битов, на линию SCL. Для каждого переданного бита на линию SDA контроллер производит его повторное чтение (контроль), чтобы обнаружить состояние коллизии (collision) с другим master-устройством. Поскольку выводы контроллера объединены по схеме «монтажное ИЛИ» в единую шину, то коллизии обнаруживаются, если была выставлена «1», а обнаружен «0». При этом передача прерывается и канал переводится в режим slave и генерируется маскируемое прерывание к центральному процессору.

После передачи каждого байта данных устройство master контролирует индикацию подтверждения от slave-станции. Если подтверждение не пришло, передача прерывается и условие «остановки» генерируется master-станцией. Регистрация stop- и start-условий всегда приводит к закрытию текущего буфера приемника.

Для передачи данных slave-устройству master-станция подготавливает в буфере n+1 байт данных, где первый байт содержит адрес slave-устройства и бит, определяющий режим чтение/запись. Остальные n байт - это данные, которые передаются slave-устройству. Если R/W = 1, то будет производиться чтение с устройства slave.

Если І2С -контроллер работает в режиме slave, то его адрес задается пользователем в регистре I2ADD (рис. 5.58) и имеет 7 разрядов, таким образом, в сети может быть до 128 slave-устройств. Если slave-устройство распознало свой адрес, то данные принимаются во внутренние буферы RxBD, на них передаются подтверждения, и так продолжается, пока по линии SDA не придет от master-станции новое start/stop-условие. Если совпадения адреса не произошло, slave-устройство ожидает следующего start-условия. Slave-контроллер подтверждает прием каждого байта, пока не обнаружит ошибку переполнения overrun своего буфера FIFO.

Если данные для передачи от master-устройства занимают несколько буферов ТхЕШ, то они будут передаваться байт за байтом, пока не будет достигнут последний буфер (бит L = 1 в его слове состояния), при этом бит STR = 1 повторно для каждого нового байта не устанавливается. Бит STR будет автоматически сбрасываться после передачи первого бита байта данных.

Если контроллер работает в режиме slave, то для начала обмена данными он ожидает команды и тактового сигнала SCL от master-устройства. Все принятые от master-станции сообщения тут же посылаются обратно, таким образом, обеспечивается подтверждение их приема.

Перед началом обмена центральный процессор slave-станции должен подготовить буферы данных для передачи (TxBD) и для приема данных (RxBD), затем установить бит STR:= 1 в регистре команд I2COM. Установка бита STR в slave-устройстве не начинает передачу, а только подготавливает схемы контроллера и данные для передачи. Передача начнется только после прихода команды от master-станции.

Если при начале передачи start-условия slave-станция в первом передаваемом байте распознала свой адрес (биты с 7-го по 1-й), то проверяется бит 0 -это бит команды R/W. Если R/W = 0, то происходит прием данных от master-станции, и эти данные принимаются в RxBD-буферы, пока не будут получены новые start- или stop-условия. Если R/W = 1, то данные из буфера FIFO передатчика slave-станции будут переданы master-станции. Если данные готовы, то они будут переданы по следующему импульсу тактового сигнала после передачи подтверждения на предыдущее сообщение. Если данные не готовы, то передача прерывается и генерируется маскируемое прерывание ТхЕ, которое уведомляет центральный процессор, что надо подготовить данные для передачи.

После передачи каждого байта передатчик проверяет бит подтверждения от master-станции. Если подтверждение не получено, то передача прерывается и генерируется прерывание центрального процессора. Прерывание также может генерироваться после передачи полного буфера, если возникла ошибка или произошло незаполнение underrun буфера FIFO передатчика. Если произошла ошибка незаполнения (underrun), то передатчик slave-станции будет передавать «1» биты, пока не получит stop-условие от master-станции.

Пользователь может управлять работой І2С -контроллера, передавая RISC-контроллеру команды INITTX PARAMETERS, CLOSE RX, INIT RX PARAMETERS, INITTX and RX PARAMETERS.

|

Рис. 5.59. Формат регистра режима SPIMODE SPI-интерфейса

Последовательный коммуникационный порт. Последовательный порт в контроллере МРС860 реализован в виде SPI (Serial Peripheral Interface). SPI -полнодуплексный, синхронный, символьно-ориентированный канал связи, использующий 4-проводной интерфейс (линия приема SPIMISO, линия передачи SPIMOSI, линия тактовых сигналов SPICLK и линия выбора slave-устройства SPISEL), предназначен для обмена данными между коммуникационными контроллерами, ISDN- и другими сетевыми устройствами. Конфигурирование режимов работы интерфейса выполняется в регистре режима SPIMODE (рис. 5.59).

Устройство, поддерживающее SPI-интерфейс, может работать в режиме master (бит M/S = 1) или slave (бит M/S = 0). Также поддерживается конфигурация multimaster для объединения нескольких SPI-устройств на общую шину, используя их выводы в режиме открытого стока (open-drain).

В режиме master SPI-контроллер передает данные для других slave-станций, которые обязаны немедленно вернуть принятый кадр (режим back-to-back). Это используется для обеспечения надежности передачи и подтверждения корректности передачи кадра.

Тактирование приемника и передатчика канала выполняется одной тактовой частотой. Если выбранное устройство работает в режиме master, то тактовый сигнал поступает от собственного независимого BRG-генератора. В режиме master устройство вырабатывает внешние сигналы выбора (разрешения работы) SPISEL для slave-устройства и сигнал SPICLK, который выставляется только во время передачи данных, для тактирования других slave-устройств. Если устройство работает в режиме slave, то тактовые сигналы поступают от внешнего источника.

Если контроллер работает в режиме master, то пользователь может управлять входной частотой для BGR-генератора. Генератор BRG для своей работы использует входную тактовую частоту от внутреннего синтезатора частоты микросхемы (SynCLK). Если бит DIV16 равен 1, то входная частота генератора BRGCLK перед поступлением на вход схемы генератора делится на 16 (BRGCLK = SynCLK/16). Если бит DIV16 = 0, то предварительного деления частоты нет.

Сам генератор может также делить входную частоту на коэффициент, который определен в битах РМ, перед тем как передать ее для тактирования схемам приемника и передатчика каналов связи. Входная частота BRGCLK делится на 4х([РМО-РМЗ])+1), таким образом, коэффициент внутреннего деления частоты может быть от 4 до 64. Сигнал на выходе генератора представляет собой меандр.

Максимальная скорость передачи отдельных символов в режиме master равна SynCLK/ 4, а в режиме slave - SynCLK/2. При передаче нескольких символов подряд интервал между ними не должен превышать значения SynCLK/50.

Особенности работы интерфейса. SPI-интерфейс выполняет полнодуплексные операции, т. е. прием данных и передача данных выполняются одновременно. При передаче наиболее значимый бит (MSB) передается первым, если бит REV = 1, и наоборот, первым передается LSB-бит, если бит REV = 0.

Размер передаваемых символов может колебаться от 4 до 16 бит. Биты LEN в регистре режима задают рабочую длину символа от 1 бита (код 0000) до 16 бит (код 1111), но, если пользователь выберет длину меньше 4 бит, будет зарегистрирована ошибка.

Как и все другие каналы ввода/вывода, SPI-интерфейс в выключенном состоянии потребляет минимум энергии, внутренний генератор не работает, и все регистры интерфейса находятся в исходном состоянии. Включение SPI-интерфейса в работу производится записью «1» в бит EN регистра SPIMODE, как показано на рис. 5.59. После установки этого бита изменять значения других битов в регистре режима пользователю запрещено.

Порт может работать или в нормальном режиме (если бит L00P = 0) или в тестовом петлевом режиме (бит L00P = 1). В петлевом режиме приемник и передатчик работают нормально, но выходы передатчика внутренне соединены со входом приемника, а данные на входных контактах приемника игнорируются.

Назначение выводов SPIMOSI и SPIMISO может меняться в зависимости от режима работы контроллера (табл. 5.37). Это сделано для упрощения объединения контроллеров в режиме multimaster.

Таблица 5.37

|

При помощи сигнала SPISEL master-станция активизирует работу slave-станции. Когда контроллер работает в режиме multimaster, вход SPISEL используется для обнаружения ошибки, когда несколько master-станций хотят работать одновременно. При этом, если контроллер работает как master-станция и обнаруживает на своем входе активный сигнал выбора slave-станции SPISEL от другого устройства master, то регистрируется ошибка.

Когда контроллер работает с несколькими slave-устройствами, следует использовать выводы параллельных портов ввода/вывода для формирования сигналов выбора slave-устройств.

Для инвертирования полярности тактового сигнала для SPI-порта используется бит CI. Если бит CI = 0, то данные выставляются на линию TXD по положительному перепаду тактового сигнала, а считываются с линии RXD - по отрицательному (рис. 5.60). Когда SPI-порт не передает данные, пассивное состояние линии тактового сигнала равно 0. Если же бит CI = 1, то данные передаются по отрицательному перепаду тактового сигнала, а считываются по положительному. Когда SPI-порт не передает данные, пассивное состояние линии тактового сигнала равно 1.

|

Бит СР определяет рабочую фазу тактового сигнала при передаче данных. Если бит СР = 0, то тактовый сигнал выставляется на линию SPICLK только в середине битового интервала передачи первого бита данных. Если бит СР = 1, то тактовый сигнал выставляется в начале битового интервала передачи первого бита данных.

Пользователь может управлять работой SPI-интерфейса при помощи команд INIT ТХ PARAMETERS, CLOSE RX BD и INIT RX PARAMETERS.

Прием и передача данных. В контроллере МРС860 параметры SPI-контроллера хранятся на 2-й странице памяти параметров (parameter RAM) со смещением + 0x1 D80 от начала двухпортовой памяти. Структура и состав памяти параметров SPI-контроллера совпадают со структурой таблицы протокол-независимых параметров (см. табл. 5.30). Отличие заключается только в том, что отсутствуют две последние ячейки таблицы со смещениями SPI base+28 и SPI base+2C.

Данные для SPI-канала хранятся в буферах памяти, которые организованы в таблицу ТхВО (передачи) и RxBD (приема). Принцип организации таблицы аналогичен таблицам буферов для SCC-каналов ввода/вывода. Стартовый адрес таблиц в памяти контроллера хранится в ячейках RBASE и TBASE памяти параметров SPI-контроллера. Число буферов в таблице пользователь может ограничить, установив бит W:= 1 в слове состояния последнего необходимого буферного дескриптора. Значения, хранящиеся в ячейках RBASE и TBASE, должны быть кратны 8.

Буферы данных могут быть расположены или во внешней памяти или во внутренней двухпортовой памяти, например, в области параметров неиспользуемых SCC-каналов.

При подготовке обмена данными центральный процессор готовит данные для передачи в буферах памяти, заполняет соответствующие буферные дескрипторы и устанавливает в их слове состояния бит готовности к передаче R:= 1, а также заранее подготавливает буферы для приема данных.

Для начала передачи данных необходимо установить бит STR в регистре команд SPICOM (рис. 5.61). Остальные биты регистра SPICOM должны быть сброшены в «0». Если SPI-интерфейс работает в режиме master, то при установке бита STR:= 1 контроллер начинает передавать и принимать данные. Данные начнут передаваться только тогда, когда они будут загружены по SDMA-каналам в буфер FIFO передатчика. Когда контроллер работает в режиме slave, то передача начнется только после прихода сигнала выбора SPISEL и внешнего тактового сигнала. Бит STR сбрасывается в «О» автоматически через один период системной тактовой частоты после начала передачи.

Размер буферов FIFO для приема и передачи ограничен двумя символами.

Master-станция начинает выдавать тактовые импульсы для каждого символа на контакт SPICLK и одновременно передавать данные на контакт SPIMOSI и принимать данные с контакта SPIMISO. Контроллер заканчивает прием и передачу, когда будут переданы все данные из буфера передачи или если при передаче возникла ошибка, а затем сбрасывает биты готовности буфера передачи R:= 0 и бит пустого буфера приема Е:= 0 и уведомляет центральный процессор об окончании передачи маскируемым прерыванием.

Если данные для передачи занимают несколько буферов в памяти, то они будут передаваться из нового буфера без задержек по окончании передачи из текущего буфера без ожидания повторной установки бита STR. Если в текущем буфере установлен бит последнего буфера кадра L = 1, то передача после передачи этого буфера будет остановлена. И текущий буфер приема данных будет закрыт, даже если он не заполнен.

7 6 5 4 3 2 1 0

| STR | Зарезервировано |

Рис. 5.61. Формат регистра команд SPICOM

При работе в режиме slave SPI-интерфейс принимает данные от SPI master-станций и немедленно передает их обратно. Для начала передачи slave-устройством центральный процессор должен подготовить данные в буферах памяти, заполнить слово состояния буферного дескриптора и установить для буферов TxBD бит готовности к передаче R:= 1. Кроме этого, процессор должен подготовить для обмена и буферы приема RxBD. Когда данные будут подготовлены, процессору необходимо установить бит STR:= 1 в регистре SPICOM, чтобы SPI-интерфейс мог подготовиться к возможному обмену данными. Обмен начнется, когда придет активный сигнал выбора SPISEL = 0 и поступят тактовые сигналы на вход SPICLK. Данные будут передаваться на контакт SPIMISO и приниматься с контакта SPIMOSI. Маскируемое прерывание может быть выставлено при завершении работы с текущим буфером или если в ходе обмена зарегистрирована ошибка. SPI-контроллер продолжает принимать данные в буферы приема RxBD, пока все подготовленные буферы не будут заполнены или не будет снят активный сигнал SPISEL.

Если сигнал SPISEL стал пассивным, но все данные из буфера передачи еще не переданы, то передача все равно будет прервана, а текущий буфер TxBD останется открытым. После прихода активного сигнала SPISEL и тактового сигнала SPICLK передача будет продолжена с точки остановки. Если же все данные переданы, а сигнал SPISEL остается активным, то контроллер будет продолжать передачу единичных битов «1».

При работе интерфейса в режиме multimaster одноименные выводы SPIMOSI, SPIMISO, SPICLK всех SPI-устройств соединяются вместе, а линии SPISEL присоединяются к каждому устройству по отдельности. При таком соединении в каждый момент времени только один SPI-контроллер может быть master-станцией, а все остальные - только устройствами slave. Если SPI-контроллер в текущий момент времени сконфигурирован как master-станция, и приходит активный сигнал SPISEL = 0 от другого master-устройства, то регистрируется ошибка совместной работы multimaster-станций, устанавливается бит MIME в регистре событий и генерируется маскируемое прерывание центрального процессора. Работа SPI-устройств останавливается, и для повторного использования контроллеров пользователь должен сбросить бит включения EN в регистре SPIMODE.

Контроллер доступа к шине USB. Основные сведения о USB-контроллере в МРС823. USB-контроллер в МРС823 состоит из четырех основных блоков: приемника, передатчика и двух автоматов для реализации протоколов обмена (protocol state machines). Оба автомата предназначены для управления работой блоков приемника и передатчика, один из них используется, когда контроллер работает в режиме function, а другой - когда контроллер работает в режиме host. Таким образом, USB-контроллер в МРС823 может работать или в режиме function, или в режиме host, или в обоих режимах сразу (это используется при loop-back диагностировании аппаратуры).

Для тактирования USB-контроллера в МРС823 должна быть использована частота (USB reference clock), которая в четыре раза превышает тактовую частоту передаваемых данных, т. е. при работе с шиной 12 Мбит/с тактовая частота должна составлять 48 МГц, а при работе с шиной 1,5 Мбит/с - 6 МГц.

В режиме function контроллер автоматически выполняет обработку контрольной суммы CRC16/CRC5, NRZI-кодирование/декодирование данных с операцией вставки/удаления бит-стаффинга (bit stuffing). В подчиненном режиме контроллер может работать со скоростями 12 или 1,5 Мбит/с и обеспечивает автоматическую повторную передачу в случае возникновения ошибок.

В режиме host контроллер автоматически выполняет обработку только контрольной суммы CRC16, NRZI-кодирование/декодирование данных с операцией вставки/удаления бит-стэффинга (bit stuffing). В режиме master контроллер может работать только со скоростью 12 Мбит/с и обеспечивает поддержку диагностического режима работы «внутренняя петля» (local loopback). Таким образом, при функционировании МРС823 в режиме host-контроллера существуют ряд нижеперечисленных ограничений.

• Не поддерживается обмен со скоростью 1,5 Мбит/с, так как передатчик не может вырабатывать биты преамбулы при низкоскоростном обмене.

• USB-контроллер в МРС823 не может выполнять функции корневого хаба (root hub).

• Некоторые функции удалены с аппаратного уровня и должны быть реализованы на программном уровне: генерация контрольной суммы CRC5 для кадров маркера (token);обнаружение ошибок и повторная передача кадра при ошибке; генерация и передача каждую 1 мс маркеров SOF tokens.

Обратите внимание, что в отличие от других коммуникационных каналов, в USB-контроллере изменена схема распределения буферов FIFO. USB-передатчик обслуживает -четыре независимых 16-байтных буфера FIFO, т. е. за каждой конечной точкой (endpoint) закреплен свой буфер передачи. А USB-приемник имеет один общий 16-байтный буфер - FIFO приема.

Настройка основных режимов работы USB-контроллера производится при программировании регистра режима USMOD (рис. 5.62), который расположен в памяти по адресу (IMMR&0xFFFF000)+0xA00.

Бит EN разрешает работу USB-контроллера. Если бит EN = 1, то контроллер работает в нормальном режиме, а если бит EN = 0, то контроллер находится в состоянии сброса. а его схемы - в режиме пониженного энергопотребления.

Бит LSS определяет скорость работы USB-контроллера. Если бит LSS = 0, то скорость передачи составляет 12 Мбит/с, а если LSS = 1, то 1,5 Мбит/с.

Бит HOST определяет режим работы USB-устройства. При значении бита HOST = 0.устройство работает как функция, а при значении HOST = 1 - как хост (host).

При установленном бите RESUME = 1 устройство-функция будет передавать по шине специальные сигналы при выходе из состояния «сон» (suspend mode).

Установка бита TEST = 1 переводит контроллер в тестовый режим внутренней петли. 3 тестовом режиме включается режим низкоскоростной передачи 1,5 Мбит/с, и, если установлен бит HOST = 1, то конечная точка Endpoint 0 работает как хост, a Endpoint 1-Endpoint 3 - как функции.

Контроллер поддерживает работу с четырьмя конечными точками (endpoints), каждая из которых может работать в одном из четырех режимов передачи (control, interrupt, bulk, sochronous). Обратите внимание, что точка Endpoint 0 должна быть сконфигурирована для control-обмена. Выбор режима работы каждой из конечных точек настраивается при программирова-нии регистров конфигурации USEPx конечной точки (рис. 5.63), которые расположены в памяти по адресу (IMMR&0xFFFF000)+0xA04 - USEP0, [IMMR&0xFFFF000)+0xA06 - USEP1, (IMMR& 0xFFFF0OO)+0xA08 - USEP2, (IMMR&0xFFFF000)+0xA0A - USEP3. Все регистры конфигурации имеют одинаковый формат.

Номер конечной точки, с которой связан тот или иной регистр USEPx, определяется в поле EPN (Endpoint Number). Биты ТМ (Transfer Mode) определяют, какой режим обмена использует конечная точка (00 - Control, 01 - Interrupt, 10 - Bulk, 11 - Isochronous).

Для того чтобы увеличить скорость передачи, пользователь может изменить бит MF (MultiFrame). Если бит MF = 0, то в буфере FIFO передатчика всегда могут быть данные только одного кадра. Если же бит MF = 1, то в буфер FIFO передатчика во время передачи данных текущего кадра может начаться загрузка данных следующего кадра.

|

Если таймер ожидания ответа на переданный пакет истек, а ответ-подтверждение не поступил, то USB-контроллер, если установлен бит RTE = 1, произведет повторную передачу текущего кадра данных.

Обратите внимание, что при работе в изохронном (isochronous) режиме передачи биты MF и RTE должны быть равны нулю.

Если USB-контроллер работает в режиме slave, то биты THS и RHS определяют, какой тип пакета-подтверждения будет выдаваться в ответ на прием маркера OUT или IN (табл. 5.38). Но следует обратить внимание, что посылка подтверждений NAK и STALL не разрешена для конечной точки Control.

|

Подключение USB-контроллера в МРС823. Поскольку коммуникационные контроллеры «Motorola» не реализуют в полном объеме функции физического уровня управления модели OSI, то для доступа к линиям D+ и D- USB-шины требуются дополнительные внешние трансиверы или драйверы линий. Для подключения к трансиверам используются следующие шесть сигналов контроллера МРС823 (рис. 5.64): USBOE - сигнал разрешения работы трансивера (активный уровень - низкий), когда

USB- контроллер передает данные по шине; USBRXD - принимаемые данные; USBRXP, USBRXN - служат для определения скорости обмена (USBRXP=1, USBRXN = 0 - скорость 12 Мбит/с, USBRXP = 0, USBRXN = 1-1,5 Мбит/с) и состояния асимметричного (singled ended) «0» (если USBRXP = USBRXN = 0);

USBTXP, USBTXN-определяют передаваемые данные (USBTXP = USBTXN = = 0 - передается singled ended «0», если USBTXP = 0 и USBTXN = 1, то передается логический «0», а если USBTXP = 1 и USBTXN = 0, то - логическая «1».

|

Рис. 5.64. Схема подключения USB-контроллера в МРС623 к внешнему трансиверу

Некоторые трансиверы имеют дополнительные линии определения текущей скорости передачи или перехода в режим пониженного энергопотребления (sleep, suspend), в этом случае управление данными сигналами можно выполнять программно через контакты параллельного порта ввода/вывода

Процесс приема и передачи в сети USB. USB - полностью контролируемая хостом шина. В системе USB может быть только один хост. Любая транзакция в ней осуществляется передачей до трех пакетов. Хост в соответствии с определенной временной диаграммой посылает USB-устройству пакет-маркер (token), описывающий тип и направление транзакции, адрес USB-устройства и номер конечной точки. Устройства USB проверяют, кому адресовано сообщение, декодируя соответствующие поля адреса. Направление передачи данных определено в маркерном пакете.

Устройства USB только отвечают на запросы хоста и не могут передавать информацию друг другу. Фактически может быть только один случай, когда устройство может инициировать передачу без активности хоста. После перевода хостом устройства в режим пониженного энергопотребления устройство может сигнализировать о своем пробуждении.

Затем источник транзакции посылает пакет данных (data packet) или сообщает, что данных для передачи нет. Получив пакет данных, адресат пакет квитирования (handshake packet), который сообщает, была ли передача успешной.

После системного сброса USB-контроллер имеет адрес 0x00 и хост должен определить новый адрес USB-устройства.

Для этого после разрешения работы USB-контроллер прослушивает шину и ожидает получение корректного кадра маркера (token). Некорректные маркеры игнорируются. Маркер считается некорректным, если его длина не равна 3 байтам, или в случае неправильной CRC (контрольной суммы), или если поле идентификаторов PID содержит некорректные данные. Маркеры могут быть четырех типов:

1) Setup token - при получении этого маркера начинается процедура конфигурирова

ния устройств или обмен информацией о статусе;

2)IN tokenm - при получении данного маркера начинается передача подготовленных

данных от USB-устройства к host-устройству;

3)OUT token - при получении этого маркера USB-устройство начинает прием данных;

4)SOF token.

Процесс реконфигурирования USB-устройства начинается при приеме маркера SETUP token, поступающего на конечную точку, которая определена как Control Endpoint. Маркер SETUP обычно содержит код команды, которую должно выполнить USB-устройство. Если тип SETUP-пакета требует приема последующих данных, то USB-контроллер выполняет прием данных так же, как и после приема маркера OUT. Если тип SETUP-пакета требует передачи некоторых данных хосту, то USB-контроллер выполняет передачу данных так же, как и после приема маркера IN.

При получении SETUP-маркера контроллер анализирует тип команды, которая содержится в маркере. Если это команда Set Address, и контроллер работает в режиме Slave, то контроллер принимает следующий пакет, который содержит назначенный хостом новый адрес USB-устройства и переписывает значение адреса в поля SAD регистра USAOR (рис. 5.65), который располагается в памяти по адресу (IMMR & 0xFFFF0000) + 0xA0l

|

Рис. 5.65. Формат регистра адреса Slave USB-устройства

Подключение USB-устройств в сеть. Все устройства USB присоединяются к USB-шине через порт специализированного устройства - USB-концентратора. Концентраторы анализируют состояние порта и определяют, присоединено или удалено устройство. Если обнаружено новое подключенное устройство, то концентратор уведомляет об этом хост. Далее хост посылает запрос концентратору, чтобы определить причину уведомления. Концентратор отвечает, указывая номер используемого порта, к которому присоединено USB-устройство. Хост через порт создает канал связи с USB-устройством, используя заданный по умолчанию адрес (Default Address = 0), который действовал при первом соединении или после сброса, и конечную точку с номером «0». Хост посылает запрос Get_Descriptor/Device на адрес «0» контрольной точки «0».

Устройство обязательно отвечает на запрос, посылая байты идентификатора обратно хосту, говорящие, какое устройство подключено.

Хост определяет, является ли недавно присоединенное устройство USB концентратором или функцией, и посылает устройству запрос Set_Address, передавая в этом пакете новый назначенный уникальный адрес устройства, позволяющий отличить это устройство от других подключенных к шине. Если присоединенное устройство - концентратор и есть USB-устройства, подключенные к его портам, то вышеупомянутая процедура сопровождается для каждого из присоединенных USB-устройств. Если присоединенное устройство - функция, то уведомление о подключении будет послано в программное обеспечение хоста.

Затем хост посылает еще запросы, запрашивая остальную информацию об устройстве. Из этих ответов хост узнает, как много каналов устройство имеет, его требования по питанию, необходимую пропускную способность канала и какой драйвер следует загрузить.

Отключение USB-устройств. Когда USB-устройство отключается от порта, концентратор автоматически отключает порт и сообщает на хост об удалении устройства. Если удаленное USB-устройство-функция, уведомления об удалении посылаются программному обеспечению хоста. Затем хост удаляет информацию относительно данного USB-устройства из всех своих структур данных. Если же удаленное USB-устройство - концентратор, процесс удаления должен быть выполнен для всех USB-устройств, которые были предварительно присоединены к концентратору.

Прием пакетов. После того как USB-контроллер получит маркер OUT token, он должен начать прием данных. Контроллер проверяет в таблице дескрипторов, которые связаны с данной конечной точкой, следующий буферный дескриптор и, если он свободен, начинает прием в буфер данных, адрес которого указан в дескрипторе. После заполнения текущего буфера контроллер закрывает буфер, сбрасывает бит незанятости Е:= 0 (Empty) в слове состояния его дескриптора и, если в слове состояния дескриптора установлен бит прерывания I = 1 (Interrupt), формирует запрос на прерывание.

Если длина принимаемого кадра данных превышает размер буфера, выделенного в памяти, то контроллер продолжает запись принимаемых данных в буфер, адрес которого указан в следующем дескрипторе, но только если у этого дескриптора установлен бит незанятости Е = 1. Если же следующий дескриптор окажется занятым, то будет зарегистрирована ошибка. После завершения приема всех данных из пакета в слове состояния буферного дескриптора последнего занятого буфера памяти устанавливается бит L = 1 (Last) и буфер закрывается.

Если принимаемый пакет содержит поле «идентификатор пакета» (DATAO/DATA1 packet ID (PID)), то в буфер будет записано только содержимое пакета, а содержимое поля PID будет занесено в соответствующие поля PID слова состояния дескриптора.

Протокол USB-шины предусматривает принцип «запрос-ответ» при реализации обмена по сети. Если при приеме пакета обнаружена ошибка, то пакет с подтверждениями не посылается и в слове состояния буферного дескриптора последнего буфера сданными из пакета устанавливаются соответствующие биты ошибок. Если же пакет принят без ошибок и проверка CRC контрольной суммы завершилась успешно, то содержимое пакета сохраняется в буфере памяти и в ответ на получение OUT-маркера может быть послано подтверждение. Тип пакета подтверждения определяется в битах RHS в регистре конфигурации конечной точки USEPx.

Протокол предусматривает обработку ошибок на аппаратном и программном уровнях. Аппаратная обработка включает в себя анализ целостности сообщения и повторение неудачных передач. Хост-контроллер повторит передачу ошибочного кадра данных три раза, а затем проинформирует клиентское программное обеспечение об ошибке.

Большинство ошибок, которые регистрирует USB-контроллер в МРС823 при своей работе, фиксируются установкой соответствующих битов ошибок в слове состояния буферных дескрипторов. Ниже перечислены ошибки, регистрируемые при приеме.

• Переполнение буфера FIFO приемника (Overrun). Данная ошибка регистрируется, если USB-контроллер не успел переписать данные из общего для всех конечных точек (endpoints) буфера FIFO приемника в буферы памяти, а по шине уже получены новые данные, которые были записаны в FIFO-буфер поверх старых. При возникновении этой ошибки контроллер закрывает буфер, устанавливает бит ошибки OV:= 1 в слове состояния дескриптора и устанавливает бит прерывания RXB в регистре событий USB-контроллера. Если новый пакет данных был принят без ошибок, то после завершения его приема USB-контроллер передает по шине отрицательное подтверждение NAK.

• Занятость (Busy). Данный тип ошибки регистрируется, если по шине принят корректный

кадр данных, но RISC-контроллер не обнаружил свободных буферов для приема данных.

При этом в регистре событий USB-контроллера устанавливается бит прерывания BSY.

• Нарушение формата кадра (Non Octet Aligned). Данный тип ошибки регистрируется,

если принят кадр, длина которого не кратна 8 битам. При возникновении этой ошибки

контроллер сохраняет принятый кадр данных в буферах памяти, закрывает буфер,

устанавливает бит ошибки NO:= 1 в слове состояния дескриптора и устанавливает

бит прерывания RXB в регистре событий USB-контроллера.

• Ошибка проверки контрольной суммы (CRC Error). При обнаружении этой ошибки кон-троллер закрывает буфер приема, устанавливает бит ошибки CR:= 1 в слове состояния дескриптора и устанавливает бит прерывания RXB в регистре событий USB-контроллера.

• Ошибка проверки алгоритма вставки/удаления бит-стаффинга. Если обнаруживается

данная ошибка, то принятый кадр сохраняется в буфере памяти, заполняется его сло-

во состояния и последним в нем устанавливается бит AB(Frame Aborted):= 1

Передача данных. При передаче данных пользователь должен предварительно загрузить данные в буфер FIFO выбранной конечной точки. Для этого пользователь должен подготовить данные для передачи в буферах памяти, заполнить слово состояния соответствующего буферного дескриптора и установить бит STR:= 1 в регистре команд USB-контроллера. Далее USB-контроллер перепишет данные в соответствующий FIFO-буфер конечной точки (endpoint) и будет ожидать появления маркера IN, при получении которого он начнет передачу данных в сеть

Если при получении IN-маркера данные в буфере FIFO не готовы или в регистре конфигурации выбранной Endpoint USEPx установлено значениебитов THS = 10, то в ответ на маркер IN посылается пакет с отрицательным подтверждением NAK. Значение битов THS определяет тип пакета подтверждения, который может быть передан в ответ на получение маркера IN.

Когда все данные текущего буферного дескриптора переданы и в слове состояния установлен бит последнего дескриптора пакета L = 1 (Last), то контроллер добавляет к пакету поле контрольной суммы и завершает передачу пакета.

В ответ на передачу пакета данных USB-контроллер ожидает от хоста получения пакета подтверждения. Если в течение определенного времени подтверждение не получено, то в слове состояния последнего дескриптора переданного пакета устанавливается бит ТО:= 1 (Time Out).

Обратите внимание, что пользователь должен самостоятельно заполнять поля DATAO/ DATA1 PID в передаваемом пакете.

Основные ошибки, регистрируемые при передаче, перечислены ниже.

• Незаполнение буфера FIFO передатчика (underrun). При возникновении этой ошибки

контроллер специально нарушает процедуру вставки бит-стаффинга, прекращает пе-

редачу из буфера, закрывает буфер, устанавливает бит ошибки UN:= 1 в слове состо-

яния дескриптора и устанавливает бит прерывания ТХЕ в регистре событий USB-кон-

троллера.

• Истек тайм-аут ожидания ответа (Timeout). Если установлен бит RTE = 1 в регистре

конфигурации, то при возникновении этой ошибки USB-контроллер делает попытку по

вторной передачи пакета, на который не пришло подтверждение. Если же бит RTE = 0

или вторая попытка повторной передачи тоже завершилась неудачей, то контроллер

закрывает буфер передачи, устанавливает бит ошибки ТО:= 1 в слове состояния деск-

риптора и устанавливает бит прерывания ТХЕ в регистре событий USB-контроллера.

•Данные для передачи не готовы (TxData not Ready). Данная ошибка возникает, когда

контроллер получил IN-маркер, а буфер FIFO передачи соответствующей конечной

точки пуст, или если конечная точка запрограммирована на посылку подтверждений

NAK или STALL. При обработке данной ошибки контроллер устанавливает бит преры-

вания ТХЕ в регистре событий USB-контроллера.

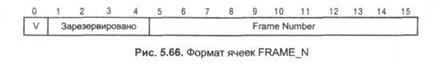

Прием служебных маркеров. При приеме маркера SOF (Start of Frame) USB-кон-троллер регистрирует маскируемое прерывание SOF и увеличивает значение в ячейке FRAME_N в памяти параметров (рис. 5.66), подсчитывая количество принятых маркеров SOF. Если SOF-маркер был принят без ошибок, то в ячейке FRAME_N будет установлен бит V:= 1.

Прием маркера PRE USB-контроллер выполняет (т. е. не игнорирует этот пакет) только при работе в режиме host (но генерировать PRE-маркеры в режиме host контроллер не может). Появление этого маркера сообщает о начале низкоскоростной передачи данных.

Настройка USB-контроллера в МРС823. Память параметров USB-контроллера. Память параметров USB-контроллера состоит из двух частей: память основных параметров USB-контроллера (табл. 5.39) и память параметров каждой из конечных точек (табл. 5.40). Память основных параметров обычно располагается в области протокол-независимых параметров 8СС2-контроллера по адресу, который вычисляется как USBBase = (IMMR & 0xFFFF0000)+0x3C.

|

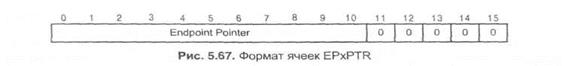

В ячейках EPxPTR (рис. 5.67) указываются адреса начала памяти каждой из исполь-з.емых конечных точек (требуется, чтобы адреса были кратны 32).

В USB-контроллере назначение переменных в ячейках памяти параметров отдельной контрольной точки (табл. 5.40) полностью совпадает с назначением одноименных -временных в SCC- и SMC-контроллерах.

Таблица 5.40

Дополнительно в ячейке TBCNT содержится внутренний вычитающий счетчик, в который при переходе к новому дескриптору передачи заносится длина буфера из соответствующего поля дескриптора и значение которого уменьшается на единицу при передаче очередного байта через SDMA-канал.

Однотипная же ячейка RBCNT имеется только в памяти параметров всего USB-koh-троллера и отсутствует среди параметров отдельных конечных точек, так как все конечные точки выполняют прием через общий FIFO буфер приема, и содержит внутренний вычитающий счетчик, в который при переходе к новому дескриптору приема заносится содержимое ячейки MRBLR и значение которого уменьшается на единицу при передаче очередного байта через SDMA-канал.

Управление USB-контроллером. Пользователь может управлять работой USB-koh-троллера, программируя его регистр команд CPCR (рис. 5.68), который расположен в ячейке памяти по адресу (IMMR & 0xFFFF0000)+0x9C0. Код команды управления записывается в биты USBCMD регистра команд (табл. 5.41). Указанная команда будет применена к конечной точке, номер которой указан в битах ENDPOINT (00-Endpoint0, 01— Endpointi, 10-Endpoint2, 11-Endpoint3). Для того чтобы USB-контроллер начал выполнять команду, необходимо установить бит FLG = 1. После выполнения команды контроллер автоматически сбросит этот бит.

Бит RST = 1 следует устанавливать, если требуется сбросить параметры всех коммуникационных каналов, регистры RISC-контроллера и RISC-таймера коммуникационного контроллера в исходное состояние. Процедура сброса выполняется RISC-контроллером в течение 60 тактов шины. Через два такта шины бит RST будет автоматически сброшен в «0».

При работе пользователь также имеет возможность управлять работой USB-контроллера, программируя регистр USB-команд (рис. 5.69), который расположен в ячейке памяти по адресу (IMMR & 0xFFFF0000)+0xA02. Если установить бит STR:= 1, то контроллер начнет подготовку данных к передаче и заполнение данными буфера FIFO передатчика конечной точки, номер которой указывается в битах ЕР. Реально передача этих данных в сеть начнется только после приема маркера IN.

При передаче данных пользователь может также, если необходимо, заменить содержимое буфера FIFO передатчика. Для этого следует передать контроллеру команду STOP ТХ ENDPOINT и установить бит FLUSH:= 1. Для возобновления передачи надо использовать команду RESTART TX ENDPOINT.

Буферные дескрипторы USB-контроллера. USB-контроллер использует такую же структуру буферных дескрипторов, что и большинство коммуникационных каналов, состоящую из четырех ячеек по 16 бит (первая ячейка - слово состояния дескриптора (рис. 5.70, 5.71), вторая -длина буфера данных в памяти, адрес которого указан в 3-й и 4-й ячейках дескриптора).

Большинство битов слов состояния имеют такое же функциональное назначение, что и

для других коммуникационных каналов.

Бит Е (Empty) - бит незанятого буфера («0» - буфер занят, «1» - не занят). Бит R (Ready) - бит готовности буфера к передаче («0» — не готов, «1» - готов или уже передается). Бит W (Wrap) - бит последнего дескриптора в таблице дескрипторов («0» - не последний дескриптор, «1» - последний). Бит I (Interrupt)- бит прерывания при завершении обработки данного буфера («0» - прерывание не регистрируется, «1» - регистрируется в регистре событий в бите RXB при приеме и ТХВ или ТХЕ при передаче). Биты F (First) и L (Last) первого и последнего буфера, в которых расположен первый (последний) бит текущего кадра данных («0» - это не первый и не последний буфер, «1» - это первый (последний) буфер кадра).

Если установлен бит ТС = 1 (Transmit CRC), то после завершения передачи содержимого последнего буфера кадра (установлен бит L = 1) сразу же будет передана контрольная сумма кадра. Если бит ТС = 0, то будет передан признак ЕОР (End of Packet).

После завершения передачи содержимого последнего буфера кадра (бит L = 1), если установлен бит CNF = 1, то контроллер будет ожидать получение подтверждения о доставке пакета. Если же бит CNF = 0, то, не ожидая ответа, будет загружать в буфер FIFO передатчика данные следующего пакета.

В бите NO (Non Octet) регистрируется ошибка приема кадра, длина которого не кратна байту. В бите АВ (Frame Aborted) регистрируется ошибка нарушения алгоритма работы с бит-стаффингом. Ошибка при проверке контрольной суммы регистрируется в бите CR (CRC Error). Ошибка переполнения буфера FIFO приемника регистрируется в бите OV (Overrun), а переполнение буфера FIFO передатчика - в бите UN (Underrun).

В биты PID (Packed ID) при приеме контроллер заносит тип принятого пакета. Биты PID заполняются только для первого дескриптора принимаемого кадра данных (бит F = 1). При передаче данных эти биты анализируются только для первого буфера (бит F = 1) передаваемого кадра и определяют тип передаваемого пакета. Если PID = 00, то буфер содержит пакет DATA0. Если же бит PID = 01, то буфер содержит пакет DATA1.

Если принятый пакет не содержит ошибок, но в настройках контрольной точки определенным образом определен тип пакета подтверждения, то будут установлены биты NAK (в ответ посылается пакет отрицательного подтверждения) или STALL (в ответ посылается пакет подтверждения STALL). Эти биты устанавливаются после завершения передачи соответствующего буфера данных.

Если после передачи конечная точка не дождалась подтверждения, то будет установлен бит ТО:= 1 (Time Out).

Регистр событий. Регистр событий USBER (рис. 5.72) расположен в ячейке памяти по адресу (IMMR&0xFFFF0000)+0xA10. Сброс битов событий в регистре событий производится записью единицы в соответствующий бит. Прерывание от любого события в USB-контроллере будет зарегистрировано, только если установлен в «1» бит регистра маски USBMR, соответствующий этому событию. Регистр маски расположен в ячейке памяти по адресу (IMMR&0xFFFFOO00)+0xA14 и имеет формат, аналогичный регистру событий.

Если USB-контроллер находится в состоянии «сброс», то будет установлен в «1» бит RESET регистра событий.

Бит IDLE регистра событий показывает, что изменилось состояние линий связи.

Биты ТХЕх регистра событий устанавливаются в «1», если произошла ошибка при передаче пакета данных: или не пришло подтверждение о получении пакета, или произошла ошибка незаполнения Underrun.

При приеме пакета SOF (Start of Frame) устанавливается бит SOF:= 1 регистра событий и увеличивается на единицу счетчик в ячейке FRAME_N памяти параметров.

Если USB-контроллер начал прием нового кадра данных, значит RISC-контроллер не нашел свободных буферных дескрипторов, а принимаемый кадр будет игнорирован и будет установлен бит BSY регистра событий.

Установка бита ТХВ регистра событий свидетельствует о том, что из текущего (но не последнего в кадре) буфера был передан в буфер FIFO передатчика последний символ, или если это последний буфер кадра, то бит будет установлен, только когда последний символ кадра будет передан в линию связи.

Установка бита RXB регистра событий свидетельствует о том, что при приеме данных текущий буфер заполнен и его дескриптор закрыт.

|