| Источник прерывания | Флаг | Адрес вектора прерывания |

| Внешнее прерывание 0 | IE0 | 0003H |

| Таймер/счетчик 0 | TF0 | 000BH |

| Внешнее прерывание 1 | IE1 | 0013H |

| Таймер/счетчик 1 | TF1 | 001BH |

| Последовательный порт | TI, RI | 0023H |

2.16.3. Контроллер прерываний имеет два регистра специальных функций (IE и IP), которые служат для программного управления системой прерываний.

Прерывание от каждого источника может быть индивидуально разрешено или запрещено путем программной установки или сброса соответствующего разряда в регистре разрешения прерываний IE (Interrupt Enable), формат которого приведен в табл. 2.13. Этот регистр также содержит разряд EA (Enable All interrupts), установка/сброс которого приводит к разрешению/запрету всех прерываний.

2.16.4. Каждому источнику прерываний индивидуально может быть присвоен один из двух уровней приоритета (1 – высокий уровень или 0 – низкий уровень) путем программирования соответствующего бита в регистре приоритетов прерываний IP (Interrupt Priority, табл. 2.14). Уровень приоритета определяет очередность обслуживания устройств в том случае, когда сигналы запросов прерываний от этих устройств приходят одновременно. Сначала обслуживаются устройства, имеющие высокий уровень приоритета, затем – все остальные.

Таблица 2.13

РЕГИСТР РАЗРЕШЕНИЯ ПРЕРЫВАНИЙ

| Обознач. | Разряд | Наименование и назначение |

| EX0 | IE.0 | Разряд разрешения внешнего прерывания 0. Устанавливается/сбрасывается программно. |

| ET0 | IE.1 | Разряд разрешения прерывания от таймера 0. Устанавливается/сбрасывается программно. |

| EX1 | IE.2 | Разряд разрешения внешнего прерывания 1. Устанавливается/сбрасывается программно. |

| ET1 | IE.3 | Разряд разрешения прерывания от таймера 1. Устанавливается/сбрасывается программно. |

| ES | IE.4 | Разряд разрешения прерывания от последовательного порта. Устанавливается/сбрасывается программно для разрешения запрета прерываний от флагов TI и RI. |

| – | IE.5 | Не используются. |

| – | IE.6 | |

| EA | IE.7 | Разряд разрешения всех прерываний. Устанавливается/ сбрасывается программно для разрешения /запрета всех прерываний. |

Таблица 2.14

РЕГИСТР ПРИОРИТЕТОВ ПРЕРЫВАНИЙ

| Обознач. | Разряд | Наименование и назначение |

| PX0 | IP.0 | Разряд приоритета внешнего прерывания 0. |

| PT0 | IP.1 | Разряд приоритета таймера 0. |

| PX1 | IP.2 | Разряд приоритета внешнего прерывания 1. |

| PT1 | IP.3 | Разряд приоритета таймера 1. |

| PS | IP.4 | Разряд приоритета последовательного порта. |

| – | IP.5 | |

| – | IP.6 | Не используются |

| – | IP.7 |

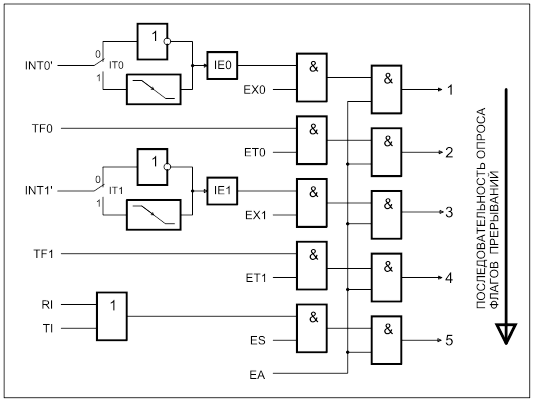

При равенстве уровней приоритета источники прерываний обслуживаются в порядке, показанном на рис. 2.14.

Рис. 2.14. Система прерываний МК 80С51

Подпрограмма обслуживания прерывания, которое было вызвано устройством, имеющим низкий уровень приоритета, сама может быть прервана другим устройством, имеющим высокий уровень приоритета. Подпрограмма обслуживания прерывания высокого уровня не может быть прервана никаким другим устройством. Программа, которая запускается при сбросе МК, имеет самый низкий приоритет, она может быть прервана устройством, имеющим любой уровень приоритета.

2.16.5. Внешнее прерывание 0 (внешнее прерывание 1) может быть инициировано как низким уровнем напряжения (уровнем логического 0), так и фронтом (переходом из 1 в 0) сигнала на соответствующем входе МК, в зависимости от значения управляющего бита IT0 (IT1) регистра TCON (см. табл. 2.8). Активный уровень сигнала на входе INT0’ (INT1’) устанавливает флаг IE0 (IE1) в регистре TCON. Если прерывание вызвано фронтом внешнего сигнала, то флаг IE0 (IE1) сбрасывается аппаратно при передаче управления подпрограмме обслуживания прерывания. Если прерывание вызвано уровнем сигнала, то флаг IE0 (IE1) сбрасывается источником внешнего прерывания.

Прерывание от таймера 0 (таймера 1) инициируется флагом TF0 (TF1), который устанавливается при переполнении соответствующего таймера, а сбрасывается аппаратно при передаче управления подпрограмме обслуживания прерывания.

Если таймер 0 работает в режиме 3 (см. п. 2.11.9), то флаг TF0 устанавливается счетчиком TH0, а флаг TF1 – счетчиком TH1.

Прерывание от последовательного порта инициируется флагом RI или флагом TI. Ни один из этих флагов не сбрасывается аппаратно при передаче управления программе обслуживания прерывания. Флаги должны сбрасываться программно.

Любой флаг, вызывающий прерывание, может быть установлен или сброшен программным путем. Результат будет таким же, как и при аппаратной установке или сбросе флага.

2.16.6. Запрос прерывания (interrupt request) формируется аппаратно при одновременном выполнении следующих условий:

1) установлен флаг готовности устройства (IE0, IE1, TF0, TF1, TI, RI),

2) установлен соответствующий управляющий бит в регистре разрешения прерываний (EX0, EX1, ET0, ET1, ES),

3) снята программная блокировка всех прерываний (установлен бит EA в регистре разрешения прерываний).

Алгоритм реакции МК на запрос прерывания представлен на рис. 2.15.

Запросы прерываний, поступившие от внутренних или внешних периферийных устройств МК, запоминаются контроллером прерываний в десятом такте (в фазе S5P2) каждого машинного цикла.

В каждом машинном цикле контроллер прерываний опрашивает и ранжирует запросы прерываний, зафиксированные в конце предыдущего цикла, в результате чего выбирается запрос, имеющий самый высокий приоритет. Ранжирование осуществляется по рассмотренной выше схеме (см. рис. 2.14) между запросами, которые относятся к одному уровню приоритета, начиная с высшего уровня. Если в предыдущем машинном цикле был зафиксирован хотя бы один запрос прерывания, а также отсутствует аппаратная блокировка прерываний, то в течение двух последующих машинных циклов управление передается программе обслуживания прерывания. Результат данной операции такой же, как при выполнении команды LCALL (см. п. 2.15.2.): в стеке сохраняется адрес возврата в прерванную программу, а в счетчик команд загружается 16-битный начальный адрес программы обслуживания прерывания (адрес вектора прерывания).

Аппаратная блокировка прерывания возможна по одной из следующих причин:

1) прерываемая программа сама является подпрограммой обслуживания прерывания равного или более высокого уровня приоритета,

2) текущий цикл (т.е. тот цикл, в котором выполняется опрос и ранжирование запросов прерываний) не является последним циклом команды, выполняемой процессором,

3) выполняемая процессором команда является командой возврата из подпрограммы обслуживания прерывания (RTI) или же командой записи в регистр разрешения прерываний IE или регистр приоритетов прерываний IP.

Таким образом от момента формирования запроса прерывания до начала выполнения подпрограммы обслуживания прерывания проходит не менее 3-х машинных циклов.

Рис. 2.15. Алгоритм реакции МК на запрос прерывания

Реакция МК на запрос прерывания будет самой быстрой, если запрос прерывания поступит к концу 9 такта машинного цикла, который является последним циклом выполнения команды, при условии, что это не команда RTI и не команда обращения к регистрам IE и IP.

Подпрограмма обслуживания прерывания должна заканчиваться командой RTI (Return from Interrupt), по которой восстанавливается из стека и загружается в счетчик команд адрес возврата в прерванную программу и снимается аппаратная блокировка прерываний.

Сигналы запросов прерываний запоминаются контроллером прерываний только на время одного машинного цикла. В каждом новом цикле будут опрашиваться и ранжироваться запросы, зафиксированные в предыдущем цикле. Если запрос прерывания не получил обслуживания из-за аппаратной блокировки прерываний по одной из рассмотренных выше причин, а к моменту окончания блокировки запрос уже был снят, то этот запрос не получит обслуживания, поскольку тот факт, что запрос не был обслужен, нигде не запоминается.

Аппаратный сброс

Сброс МК осуществляется с помощью внешнего сигнала RST, поступающего на одноименный вход МК, который является входом встроенного триггера Шмитта. Сигнал RST должен иметь длительность не менее двух машинных циклов, а напряжение этого сигнала для МК 80С51 должно быть равно напряжению логической единицы.

По сигналу RST в МК формируется внутренний сигнал сброса, по которому обнуляется содержимое всех регистров специальных функций, кроме регистров-защелок параллельных портов, регистра-указателя стека и буферного регистра последовательного порта. В регистры-защелки параллельных портов записываются коды FFH, в регистр-указатель стека SP – код 07H, а состояние регистра SBUF не определено. На внутреннюю память данных сигнал RST не действует.

Пока на входе RST присутствует логический сигнал 1, сигналы ALE и PSEN’ не вырабатываются (ALE = PSEN’ =1). МК начинает формировать эти сигналы через 1 ¸ 2 машинных цикла после сброса сигналы RST.

Для того, чтобы происходил автоматический сброс МК при включении электропитания, можно включить внешний конденсатор ко входам RST и Vcc, как показано на рис. 2.16. В момент подачи напряжения питания на вход Vcc начинается заряд конденсатора, и ток заряда, протекающий по внутреннему резистору, подключенному между входами RST и Vss, формирует на входе RST положительное напряжение экспоненциальной формы, скорость спада которого зависит от емкости конденсатора и сопротивления цепи заряда. Для того, чтобы обеспечить надежный сброс МК, время в течение которого на входе RST удерживается напряжение логической единицы должно быть не меньше, чем время запуска внутреннего тактового генератора МК, которое составляет от 1 мс до 10 мс в зависимости от частоты кварцевого резонатора, плюс два машинных цикла, необходимые для формирования внутреннего сигнала сброса. Отрицательное напряжение, формируемое на входе RST при отключении электропитания, не опасно для МК, поскольку оно ограничивается внутренними цепями защиты.

При проектировании контроллеров на базе МК 80С51 следует помнить о том, что до тех пор, пока не запустится внутренний тактовый генератор МК, и в регистры-защелки параллельных портов не будут записаны коды FFH, состояние этих портов не определено. Состояние внутренней памяти данных после включения электропитания также не определено.

Рис. 2.16. Цепь автоматического сброса микроконтроллера при

Включении электропитания