Общие сведения о микроконтроллерах 80C51

80С51 – это название одного из десяти подсемейств микроконтроллерного семейства MCS-51 фирмы Intel [ 2 ]. В состав подсемейства 80С51 входят микросхемы пяти типов (рис. 2.1), некоторые из которых могут выпускаться в различных корпусах. Тип корпуса обозначается буквой, стоящей на первом месте в обозначении типа микросхемы: P – PDIP-40, D – CerDIP-40, N – PLCC-44, S – PQFP-44.

Рис. 2.1. Микросхемы подсемейства 80С51 микроконтроллерного семейства MCS-51 фирмы Intel

Архитектура микроконтроллеров подсемейства 80С51 (в дальнейшем МК 80С51) в основном повторяет базовую архитектуру семейства MCS-51. Микросхемы разных типов отличаются друг от друга только типом и объемом внутренней программной памяти, объемом адресного пространства внешней памяти данных и максимальной тактовой частотой. Все микросхемы выполнены по одной технологии (CHMOS – Complementary High-performance Metal-Oxide-Semiconductor) и имеют общую конфигурацию (количество и функциональное назначение) внешних выводов

(рис. 2.2). Номера выводов зависят от типа корпуса микросхемы.

Рис. 2.2. Конфигурация внешних выводов МК 80С51 (корпус DIP-40)

Особенности архитектуры

2.2.1. Архитектурой вычислительной системы (computing architecture) называется общая логическая организация цифровой вычислительной системы, определяющая процесс обработки данных в конкретной вычислительной системе и включающая методы кодирования данных, состав, назначение, принципы взаимодействия технических средств и программного обеспечения [ 3 ].

2.2.2. Архитектура МК 80C51 имеет следующие особенности [ 5 ]:

1) 8-разрядный процессор, оптимизированный для управляющих применений,

2) обширные возможности обработки логических сигналов,

3) адресное пространство программной памяти объемом 64К байт,

4) адресное пространство внешней памяти данных объемом 64К байт,

5) внутренняя программная память объемом 4К байт,

6) внутренняя память данных объемом 128 байт,

7) 32 двунаправленных и индивидуально адресуемых входа/выхода

8) два 16-разрядных таймера/счетчика,

9) встроенный последовательный порт,

10) двухуровневая векторная система прерываний (6 источников/5 векторов),

11) встроенный тактовый генератор.

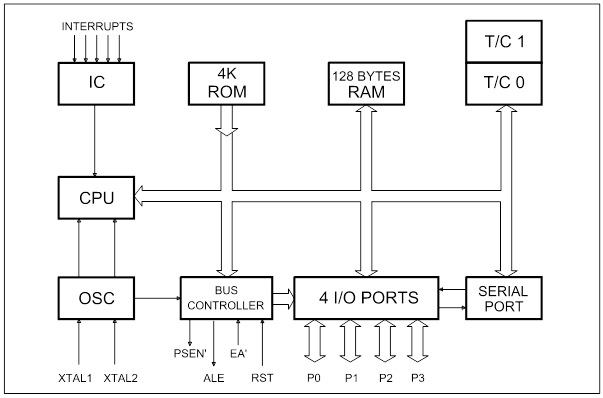

2.2.3. Упрощенная структурная схема МК 80С51 приведена на рис. 2.3, где CPU – центральный процессор, OSC – тактовый генератор, XTAL1, XTAL2 – входы подключения внешнего кварцевого резонатора, BUS CONTROLLER – контроллер шины, PSEN’ – строб чтения из внешней программной памяти, ALE – сигнал разрешения “защелкивания” адреса, EA’ – сигнал запрещения доступа CPU к внутренней программной памяти, RST – внешний сигнал сброса МК, I/O PORTS – параллельные порты ввода/вывода, P0, P1, P2, P3 – внешние линии параллельных портов ввода/вывода, SERIAL PORT – последовательный порт, T/С 0, T/C 1 – таймеры/счетчики, 128 BYTES RAM – память данных объемом 128 байт, 4K ROM –программная память объемом 4К байт, IC – контроллер прерываний, INTERRUPTS – сигналы запросов прерываний.

Рис. 2.3. Упрощенная структурная схема МК 80С51

Примечание. В тексте данного учебного пособия для обозначения инверсии логического сигнала используется апостроф (’).

Организация памяти

2.3.1. При организации взаимодействия CPU с памятью и другими функциональными устройствами используется единый принцип идентификации устройств – выбор по адресу. Совокупность всех возможных адресов называется адресным пространством.

2.3.2. МК 80C51 имеют четыре раздельных адресных пространства: адресное пространство программной памяти (program memory) объемом 64К байт, адресное пространство внешней памяти данных (external data memory) объемом 64К байт, адресное пространство внутренней памяти данных (internal data memory) объемом 128 байт и адресное пространство регистров специальных функций (SFR – Special Function Register) объемом 128 байт (рис. 2.4).

Микроконтроллеры типа 80С51BHP отличаются от микроконтроллеров других типов тем, что имеют объемы адресных пространств программной памяти и внешней памяти данных по 4К байт.

2.3.3. Программная память предназначена для хранения кодов команд или констант. Это постоянная память, она доступна только для чтения и недоступна для записи (ROM – Read Only Memory). МК 80C51 выпускаются четырех типов (см.

рис. 2.1): без внутренней постоянной памяти (80С31BH), с внутренней постоянной памятью масочного типа (80C51BH), с внутренней постоянной памятью масочного типа, защищенной от внешнего считывания (80C51BHP), с внутренней программируемой постоянной памятью, стираемой ультрафиолетовым светом (D87C51), и с однократно программируемой внутренней постоянной памятью (P87C51). Микросхема P87C51 отличается от микросхемы D87C51 только тем, что она выпускается в пластмассовом корпусе, не имеющем окна для стирания памяти, в то время как микросхема D87C51 имеет керамический корпус с окном, через которое осуществляется ультрафиолетовое облучение кристалла.

Для того, чтобы запретить доступ CPU к внутренней программной памяти, на МК требуется подать внешний логический сигнал EA’=0 (External Access).

При чтении информации из внешней программной памяти МК вырабатывает строб PSEN’ (Program Storage Enable).

Для разрешения доступа к внутренней программной памяти необходимо выполнение условия EA’=1. При обращении CPU к внутренней программной памяти строб PSEN’ не вырабатывается.

Рис. 2.4. Структура памяти МК 80C51

2.3.4. Память данных (data memory) предназначена для хранения переменных в процессе выполнения программы. Это оперативная память, она доступна как для чтения, так и для записи (RAM – Random Access Memory). При обращении к внешней памяти данных МК вырабатывает строб чтения RD’ (read) и строб записи WR’ (write).

2.3.5. Адресные пространства внешней памяти программ и внешней памяти данных могут быть объединены. Для этого нужно подать сигналы RD’ и PSEN’ на входы логического элемента И, выходной сигнал которого следует использовать в качестве строба чтения из единой внешней памяти программ/данных.

Программная память

2.4.1. При сбросе МК (по внешнему сигналу RST) CPU начинает выполнение программы с адреса 0000H. В том случае, когда EA’=1 (см. рис. 2.4), начальный участок программы (младшие 4К байт) извлекается процессором из внутренней постоянной памяти, а остальная часть программы – из внешней памяти. Если МК не имеет внутренней постоянной памяти (или она не используется), то на вход EA’ следует подать логический сигнал 0. При этом выборка всей программы будет осуществляться из внешней памяти

2.4.2. Область адресного пространства программной памяти, начиная с адреса 0003Н, отводится для размещения начальных участков подпрограмм обслуживания прерываний (8 байтов на каждую из пяти программ). Адрес первого байта подпрограммы обслуживания прерывания (0003Н, 000BH, 0013H, 001BH, 0023Н), называемый адресом вектора прерывания, формируется контроллером прерываний МК аппаратно при обработке соответствующего запроса прерывания (см. подраздел 2.17).

2.4.3. Подключение к МК микросхемы внешней программной памяти показано на рис. 2.5, где A0 ¸ A7 – входы младших разрядов адреса, A8 ¸ A15 – входы старших разрядов адреса, OE’ и CS’ – управляющие входы, DATA – данные, считываемые из памяти, LATCH – регистр-защелка младшего байта адреса (8-разрядный параллельный регистр памяти, тактируемый уровнем).

При обращении к внешней программной памяти порт P0 МК работает в режиме временного мультиплексирования и служит как для вывода младшего байта адреса ячейки внешней памяти, так и для ввода в МК байта данных. Порт P2 используется для вывода старшего байта адреса.

Временным мультиплексированием (time-division multiplexing) называется предоставление канала ввода/вывода информации различным устройствам в разные промежутки времени.

Стробирование ввода/вывода информации через порт P0 при чтении данных из внешней программной памяти осуществляется с помощью управляющих сигналов ALE и PSEN’, вырабатываемых МК. Сигнал ALE (Address Latch Enable), поступающий с соответствующего выхода МК на тактовый вход регистра-защелки, предназначен для “защелкивания” младшего байта адреса, т.е. запоминания в регистре-защелке того кода, который был на выходах порта P0 в момент окончания сигнала ALE. Сигнал PSEN’ служит для управления считыванием данных из микросхемы памяти. Если на управляющий вход CS’ (Chip Select) микросхемы памяти поступает сигнал CS’=0, то подача сигнала PSEN’=0 на управляющий вход OE’ (Output Enable) микросхемы приведет к тому, что байт данных (DATA) из адресуемой ячейки памяти поступит на вход порта P0 МК.

Рис. 2.5. Подключение микросхемы EPROM к МК 80C51

Временные диаграммы работы МК при выборке кодов команд из внешней программной памяти приведены в подразделе 2.9.

2.4.4. При обращении к внешней программной памяти всегда вырабатывается

16-разрядный адрес (даже тогда, когда объем исполняемой программы меньше, чем 64К байт), поэтому в тех случаях, когда для хранения программы или значений констант используется внешняя программная память, приходится “жертвовать” двумя портами МК.

Память данных

2.5.1. К любому микроконтроллеру подсемейства 80С51 (за исключением 80С51BHP) можно подключить внешнюю память данных объемом до 64 К байт

(к 80С51BHP– до 4К байт). Пример подключения микросхемы памяти объемом 32К байт приведен на рис. 2.6.

Так же, как и при чтении данных из внешней программной памяти, при обращении к внешней памяти данных порт P0 МК работает в режиме временного мультиплексирования. Через этот порт из МК выводится младший байт адреса ячейки внешней памяти и осуществляется ввод/вывод байта данных. Порт P2 используется для вывода старшего байта адреса. Синхронизация операций обращения к внешней памяти данных осуществляется с помощью строба записи WR’ и строба чтения RD’, которые формируются, соответственно, на выходах Р3.6 и P3.7 МК (см. рис. 2.2). Временные диаграммы сигналов приведены в подразделе 2.9.

Рис. 2.6. Подключение микросхемы 32K RAM к МК 80С51

2.5.2. Если объем внешней памяти данных меньше, чем 64К байт, то старшие разряды порта Р2 можно использовать для того, чтобы разделить адресное пространство 64К байт между несколькими устройствами, например, между двумя микросхемами памяти объемом 32К байт каждая или микросхемой памяти и другими устройствами ввода/вывода информации (аналого-цифровым преобразователем, жидкокристаллическим индикатором и т.д.). Выбор устройства осуществляется путем подачи логического сигнала 0 на управляющий вход CS’. Например, подключение входа CS’ микросхемы памяти к выходу Р2.7, как показано на рис. 2.6, приведет к тому, что эта микросхема памяти будет реагировать только на обращение по адресам 0000Н ¸ 7FFFH, а адресное пространство 8000Н ¸ FFFFH может быть использовано другими внешними устройствами.

2.5.3. Адресное пространство внутренней памяти данных МК 80С51 имеет объем 128 байт (рис. 2.7). Для доступа к этой памяти можно использовать прямую или косвенную адресацию (см. подраздел 2.8).

Рис. 2.7. Организация внутренней памяти данных

К тридцати двум ячейкам внутренней памяти данных, имеющим адреса от 00Н до 1FН, можно обращаться как к регистрам. Все регистры объединены в 4 банка по 8 регистров в каждом. В пределах банка регистрам присвоены имена R0 ¸ R7. Один из четырех регистровых банков может быть активным. К регистру активного банка можно обратиться по имени (номеру) с помощью регистровой адресации (см. подраздел 2.8.). Номер активного банка (в двоичном виде) задается путем программирования двух разрядов слова состояния программы (см. подраздел 2.6).

Ячейки памяти, имеющие адреса от 20Н до 2FН доступны для побитовой адресации (табл.2.1). Система команд микроконтроллеров семейства MCS-51 содержит специальные команды операций с битами (см. подраздел 2.7).

Таблица 2.1