| Обозначение | Разряд | Наименование и назначение |

| A0/D0 | P0.0 | Разряд 0 шины адреса/данных. |

| A1/D1 | P0.1 | Разряд 1 шины адреса/данных |

| A2/D2 | P0.2 | Разряд 2 шины адреса/данных |

| A3/D3 | P0.3 | Разряд 3 шины адреса/данных |

| A4/D4 | P0.4 | Разряд 4 шины адреса/данных. |

| A5/D5 | P0.5 | Разряд 5 шины адреса/данных. |

| A6/D6 | P0.6 | Разряд 6 шины адреса/данных. |

| A7/D7 | P0.7 | Разряд 7 шины адреса/данных. |

| A8 | P2.0 | Разряд 8 шины адреса |

| A9 | P2.1 | Разряд 9 шины адреса |

| A10 | P2.2 | Разряд 10 шины адреса |

| A11 | P2.3 | Разряд 11 шины адреса |

| A12 | P2.4 | Разряд 12 шины адреса |

| A13 | P2.5 | Разряд 13 шины адреса |

| A14 | P2.6 | Разряд 14 шины адреса |

| A15 | P2.7 | Разряд 15 шины адреса |

| RXD | P3.0 | Вход приемника последовательного порта в режиме UART. Ввод/вывод данных в синхронном режиме |

| TXD | P3.1 | Выход передатчика последовательного порта в режиме UART. Выход синхронизации в синхронном режиме |

| INT0’ | P3.2 | Вход запроса прерывания 0. Активным является сигнал низкого уровня (логический 0) или перепад 1 ® 0 |

| INT1’ | P3.3 | Вход запроса прерывания 1. Активным является сигнал низкого уровня (логический 0) или перепад 1 ® 0 |

| T0 | P3.4 | Вход таймера/счетчика 0 |

| T1 | P3.5 | Вход таймера/счетчика 1 |

| WR’ | P3.6 | Выход “ЗАПИСЬ”. Активный сигнал низкого уровня формируется при обращении к внешней памяти данных |

| RD’ | P3.7 | Выход “ЧТЕНИЕ”. Активный сигнал низкого уровня формируется при обращении к внешней памяти данных |

В режиме таймера (т.е. счетчика времени) содержимое счетчика инкрементируется в каждом машинном цикле. В режиме счета внешних событий содержимое счетчика инкрементируется под воздействием перехода из 1 в 0 внешнего логического сигнала, поступающего на соответствующий вход микроконтроллера.

2.11.2. При работе таймера/счетчика в режиме счетчика внешних событий максимальная частота входных импульсов не должна превышать 1/24 тактовой частоты микроконтроллера, поскольку для распознавания перехода внешнего сигнала из 1 в 0 требуется два машинных цикла. Для того, чтобы обеспечить надежное считывание значения внешнего входного сигнала, сигнал не должен изменяться в течение одного полного машинного цикла. Длительность периода входного сигнала сверху не ограничена.

2.11.3. Для управления работой таймеров/счетчиков и организации взаимодействия таймеров/счетчиков с системой прерываний используются два регистра специальных функций – регистр управления режимом TMOD (Timer/Counter Mode Control Register) и регистр управления TCON (Timer/Counter Control Register), форматы которых приведены в табл. 2.7 и табл. 2.8, соответственно.

2.11.4. Выбор функционального назначения таймера/счетчика (“таймер” или “счетчик внешних событий”) осуществляется программированием бита C/T’ регистра TMOD (см. табл. 2.7).

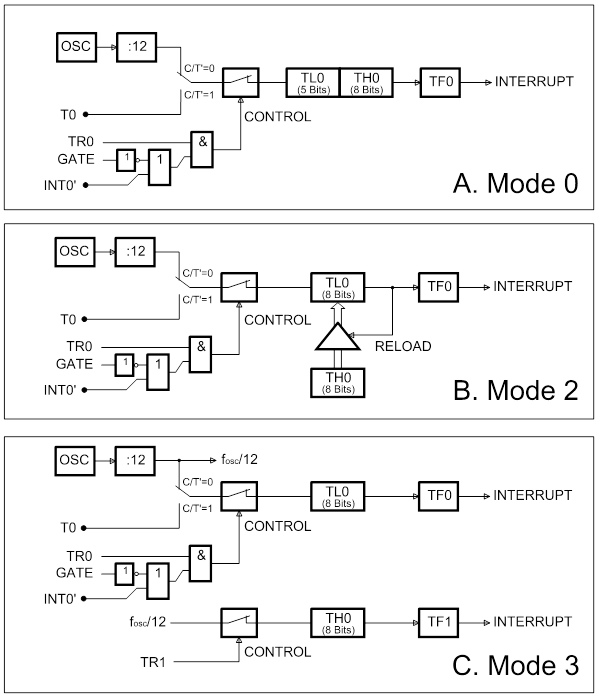

2.11.5. Каждый таймер/счетчик (в дальнейшем таймер) имеет четыре режима работы, индивидуально программируемых с помощью битов M0 и M1 регистра TMOD (см. табл. 2.7). Выбранный режим определяет не только алгоритм работы таймера, но также и его внутреннюю структуру (рис. 2.11). Режимы 0, 1 и 2 одинаковы для обоих таймеров. В режиме 3 таймеры работают по-разному. Ниже рассмотрены все режимы работы таймеров на примере таймера 0.

2.11.6. В режиме 0 таймер 0 представляет собой программно управляемый

13-разрядный двоичный счетчик импульсов, состоящий из 8-разрядного счетчика TH0, вход которого подключен к выходу 5-разрядного делителя частоты TL0 (рис. 2.11, А). При переполнении счетчика (когда счетчик переходит из состояния “все единицы” в состояние “все нули”) таймер устанавливает флаг TF0 (см. табл. 2.8).

Таблица 2.7

РЕГИСТР УПРАВЛЕНИЯ РЕЖИМОМ ТАЙМЕРА/СЧЕТЧИКА

| Обозначение | Разряд | Наименование и назначение |

| M0 | TMOD.0 | Режим работы таймера/счетчика 0: |

| M1 | TMOD.1 | M1=0, M0=0 – 13-разрядный таймер/счетчик (TL0 - 5 бит, TH0 - 8 бит); M1=0, M0=1 – 16-разрядный таймер/счетчик (TL0 - 8 бит, TH0 - 8 бит); M1=1, M0=0 – 8-разрядный таймер/счетчик TL0 с авто- перезагрузкой. При переполнении TL0 в TL0 загружается содержимое TH0; M1=1, M0=1 – TL0 – 8-разрядный таймер/счетчик, TH0 – 8-разрядный таймер, управляемый сигналом TR1 и устанавливающий флаг переполнения TF1. |

| C/T’ | TMOD.2 | Выбор режима таймера/счетчика 0: C/T’=1 – режим счетчика внешних событий. Содержимое счетчика инкрементируется при перепаде 1 ® 0 на входе T0 (в следующем машинном цикле), C/T’=0 – режим таймера. Инкрементируется в каждом машинном цикле. |

| GATE | TMOD.3 | Управление блокировкой таймера/счетчика 0. Если бит установлен, то сигнал на вход таймера/счетчика 0 поступает только при условии INT0’=1 |

| M0 | TMOD.4 | Режим работы таймера/счетчика 1: |

| M1 | TMOD.5 | M1=0, M0=0 – 13-разрядный таймер/счетчик (TL1 - 5 бит, TH1 - 8 бит); M1=0, M0=1 – 16-разрядный таймер/счетчик (TL1 - 8 бит, TH1 - 8 бит); M1=1, M0=0 – 8-разрядный таймер/счетчик TL1 с авто- перезагрузкой. При переполнении TL1 в TL1 загружается содержимое TH1; M1=1, M0=1 – останов таймера/счетчика 1. |

| C/T’ | TMOD.6 | Выбор режима таймера/счетчика 1: C/T’=1 – режим счетчика внешних событий. Содержимое счетчика инкрементируется при перепаде 1 ® 0 на входе T1 (в следующем машинном цикле), C/T’=0 – режим таймера. Инкрементируется в каждом машинном цикле. |

| GATE | TMOD.7 | Управление блокировкой таймера/счетчика 1. Если бит установлен, то сигнал на вход таймера/счетчика 1 поступает только при условии INT1’=1 |

Таблица 2.8

РЕГИСТР УПРАВЛЕНИЯ ТАЙМЕРА/СЧЕТЧИКА

| Обознач. | Разряд | Наименование и назначение |

| IT0 | TCON.0 | Бит управления типом внешнего прерывания 0: IT0=1 - активным сигналом на входе INT0’ является перепад 1 ® 0; IT0=0 - активным сигналом на входе INT0’ является 0. |

| IE0 | TCON.1 | Флаг фронта внешнего прерывания 0. Устанавливается по перепаду 1 ® 0 на входе INT0’. Сбрасывается аппаратно при обслуживании прерывания. |

| IT1 | TCON.2 | Бит управления типом внешнего прерывания 1: IT0=1 - активным сигналом на входе INT1’ является перепад 1 ® 0; IT0=0 - активным сигналом на входе INT1’ является 0. |

| IE1 | TCON.3 | Флаг фронта внешнего прерывания 1. Устанавливается по перепаду 1 ® 0 на входе INT1’. Сбрасывается аппаратно при обслуживании прерывания. |

| TR0 | TCON.4 | Бит управления таймером 0. Устанавливается/сбрасывается программно для пуска/останова таймера/счетчика 0. |

| TF0 | TCON.5 | Флаг переполнения таймера 0. Устанавливается аппаратно при переполнении таймера 0. Сбрасывается аппаратно при обслуживании прерывания. |

| TR1 | TCON.6 | Бит управления таймером 1. Устанавливается/сбрасывается программно для пуска/останова таймера/счетчика 1. |

| TF1 | TCON.7 | Флаг переполнения таймера 1. Устанавливается аппаратно при переполнении таймера 1. Сбрасывается аппаратно при обслуживании прерывания. |

Рис. 2.11. Таймер-счетчик 0 в разных режимах работы:

А. Режим 0: 13-разрядный счетчик,

В. Режим 2: 8-разрядный счетчик с автоперезагрузкой,

С: Режим 3: два 8-разрядных счетчика

Счетные импульсы поступают на вход счетчика TL0, когда TR0=1 и либо GATE=0, либо INT0’=1, где TR0 – управляющий бит регистра TCON (см. табл. 2.8), GATE – бит 3 регистра TMOD (см. табл. 2.7), а INT0’ – внешний сигнал запроса прерывания.

2.11.7. Режим 1 отличается от режима 0 (см. рис. 2.11, А) только тем, что счетчик TL0 имеет разрядность 8 бит, а весь таймер, в структуру которого входят два последовательно включенных счетчика TL0 и TH0, имеет разрядность 16 бит.

2.11.8. В режиме 2 таймер 0 представляет собой 8-разрядный счетчик с автоперезагрузкой (см. рис. 2.11, В). При переполнении счетчика TL0 не только устанавливается флаг TF0, но и автоматически загружается в TL0 содержимое счетчика TH0. После перезагрузки содержимое счетчика TH0 остается прежним. Начальная установка счетчика TH0 выполняется программным путем.

2.11.9. В режиме 3 таймеры 0 и 1 работают по-разному.

Содержимое таймера 1 в режиме 3 сохраняется неизменным (эффект такой же, как при TR1=0).

Счетчики TL0 и TH0 таймера 0 работают как два независимых 8-разрядных счетчика (см. рис. 2.11, С). Счетчик TL0 использует управляющие биты таймера 0: C/T’, GATE, TR0, INT0’ и TF0. Счетчик TH0, который может выполнять только функции таймера (считать машинные циклы), использует управляющий бит TR1 и флаг TF1 таймера 1.

Режим 3 используется тогда, когда для реализации требуемого алгоритма нужен дополнительный 8-разрядный таймер или счетчик. Если таймер 0 работает в режиме 3, в составе МК 80С51 имеется три таймера. При этом таймер 1 может быть выключен путем перевода в свой собственный режим 3, может быть использован последовательным портом в качестве формирователя частоты синхронизации, а также может быть использован в любом применении, не требующем прерывания.

Последовательный порт

2.12.1. Последовательный порт предназначен для приема и передачи данных в последовательном коде. Преобразование параллельного кода в последовательный и обратно осуществляется с помощью сдвигающих регистров универсального асинхронного приемопередатчика (UART – Universal Asynchronous Receiver/Transmitter), принцип работы которого представлен на рис. 2.12, где: Data Bits – параллельный код передаваемых (принятых) данных, Serial Data – последовательный код данных, D0 ¸ D8 – разряды сдвигающих регистров приемопередатчика, Shift – сигнал управления сдвигом, LSB (Least Significant Bit) – младший бит, MSB (Most Significant Bit) – старший бит, Start Bit – стартовый бит, Stop Bit – стоп-бит, TXD – выход передатчика, RXD – вход приемника,

1-to-0 DETECTOR – устройство обнаружения стартового бита (перехода входного сигнала из 1 в 0).

Рис. 2.12. Работа универсального асинхронного приемопередатчика в режиме передачи данных (A) и в режиме приема данных (B)

В режиме передачи данных UART не только преобразует параллельный код в последовательный, но также добавляет к каждому передаваемому байту данных два служебных бита – стартовый бит и стоп-бит, которые служат для определения границ байта данных.

2.12.2. Последовательный порт МК 80С51 может работать в полном дуплексном режиме, т.е. он может осуществлять передачу и прием данных одновременно.

Сдвигающие регистры приемника и передатчика последовательного порта имеют доступ к одному и тому же регистру специальных функций SBUF. Запись байта в регистр SBUF приводит к автоматической загрузке сдвигающего регистра передатчика и инициирует начало передачи. По окончании приема байта в сдвигающий регистр приемника, содержимое этого регистра загружается в SBUF

Наличие в структуре микроконтроллера буферного регистра позволяет совмещать операции приема очередного байта данных с чтением ранее принятого байта. Однако, для того, чтобы не произошло потери информации, к моменту окончания приема очередного байта, предыдущий байт должен быть считан из SBUF.

2.12.3.Последовательный порт имеет 4 режима работы. Выбор режима осуществляется путем программирования соответствующих разрядов регистра управления последовательного порта SCON (Serial Port Control Register), формат которого представлен в табл. 2.9.

Во всех четырех режимах работы последовательного порта передача данных инициируется любой командой микроконтроллера в которой регистр SBUF выступает в качестве регистра-приемника результата. По окончании передачи байта данных устанавливается флаг прерывания передатчика TI в регистре SCON.

2.12.4. Режим 0 – синхронный режим с постоянной скоростью обмена (Baud Rate), определяемой выражением:

BR0 = fosc / 12, (2.1)

где BR0 – скорость обмена в режиме 0, бод;

fosc – частота тактового генератора МК, Гц.

В режиме 0 разряд Р3.0/RXD порта 3 микроконтроллера используется для ввода/вывода последовательных данных (8 бит), а разряд Р3.1/TXD – для формирования выходных импульсов синхронизации. За один машинный цикл передается (принимается) один бит данных. В конце передачи 8-го бита устанавливается флаг прерывания передатчика TI в регистре SCON.

Таблица 2.9