Основные сведения о ЗУ.

Память ЭВМ - совокупность запоминающих устройств, предназначенных для записи, хранения и выдачи информации, представленной в виде цифровых кодов. Запись в ЗУ или считывание из него информации называют обращением к ЗУ.

Основными характеристиками ЗУ являются ёмкость и быстродействие:

1. Ёмкость памяти - максимальное количество информации, которое одновременно может в нём храниться. В настоящее время ёмкость ЗУ принято измерять в битах и байтах (1байт = 8 бит; 1 К = 1024 байт).

2. Быстродействие ЗУ оценивают его временными характеристиками. К таким характеристикам относят время обращения (доступа) к ЗУ и время цикла обращения. Время обращения к ЗУ - время, которое необходимо для вывода информации из памяти на шину данных после адресации нужной области памяти. Время цикла - минимальный интервал времени между двумя последовательными обращениями к ЗУ.

Особенности построения и функционирования определяют классификацию ЗУ следующим образом:

I. По использованию, на:

а) внешние;

б) внутренние ЗУ;

II. По физическим принципам действия, на:

а) полупроводниковые;

б) магнитные;

в) оптические ЗУ;

В качестве носителя информации в полупроводниковых ЗУ используются полупроводниковые элементы, а в магнитных - плёночные элементы, ферритовые сердечники, МБ, МЛ, МД. В оптических ЗУ используются различные оптические среды.

III.По технологии изготовления, на:

а) дискретные (ферритовые сердечники);

б) интегральные ЗУ;

IV.По способу хранения информации, на:

а)статические;

б) динамические ЗУ;

В статических ЗУ хранимая информация остаётся неподвижной по отношению к носителю информации, а в динамических информация находится в движении относительно носителя.

V. По способу доступа к заданной ячейке, с:

а) последовательным;

б) циклическим;

в) произвольным доступом;

В ЗУ с последовательным доступом осуществляется последовательное обращение к ячейкам памяти до тех пор, пока не произойдёт обращение к заданной ячейке. В ЗУ с циклическим доступом информация из заданной ячейки считывается только в определённые моменты, разделённые интервалом времени. В ЗУ с произвольным доступом информация записывается и считывается по любому адресу.

VI.По характеру обращения, с:

а) адресным;

б) ассоциативным обращением:

В ЗУ с адресным обращением выбор ячейки памяти производится по её адресу, указанному в коде выполняемой команды. В ЗУ с ассоциативным обращением поиск информации производится не по адресу, а по некоторому признаку, содержащемуся в самом хранимом слове путём сравнения и совпадения.

VII. По назначению, на:

а) сверхоперативные (СОЗУ);

6} оперативные (ОЗУ);

в) постоянные (ПЗУ);

г) буферные (БЗУ);

д) внешние (ВЗУ);

СОЗУ имеют быстродействие, соизмеримое с быстродействием процессора (10-100нс). ёмкость СОЗУ невелика. Они служат для хранения операндов, необходимых для выполнения текущей последовательности команд программы, служебной информации, используемой при выполнении вычислительным процессом.

ОЗУ предназначены для хранения данных и программ текущих вычислений, а также программ, к которым следует быстро перейти. Они имеют ёмкость от нескольких тысяч до сотен тысяч слов и период обращения от долей до нескольких микросекунд.

ПЗУ предназначены для хранения и считывания информации, которая не изменяется в процессе вычислений. Это различные константы, табличные значения, тестовые программы и др. ПЗУ менее сложны чем ОЗУ.

БЗУ используются для промежуточного хранения данных при обмене между устройствами с разным быстродействием, например между ОЗУ и ВЗУ. По ёмкости и быстродействию БЗУ занимают промежуточное положение между ОЗУ и ВЗУ,

ВЗУ предназначены для хранения больших массивов информации. Объём данных в ВЗУ обычно превышает сотни миллионов слов, однако период обращения к ним составляет от нескольких миллисекунд до нескольких десятков секунд.

|

|

При изучении ЗУ будем рассматривать только интегральные схемы полупроводниковых ЗУ. Такие схемы позволяют создавать устройства памяти с большой информационной ёмкостью.

Рис.91. Классификация ЗУ.

На рис.91 буквами РУ, РЕ, РТ, РР, РФ отмечены условные обозначения вида изделия по функциональному назначению; буквами RAM, ROM, PROM, EEPROM, EPROM отмечены условные обозначения ИС ЗУ на условном графическом обозначении.

5.2. Схемотехника запоминающих устройств.

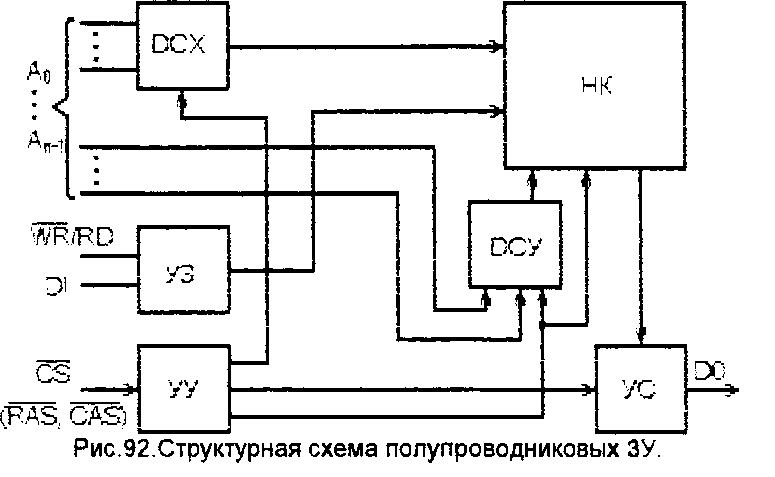

Типовая структурная схема полупроводниковых БИС ЗУ (ОЗУ, ПЗУ, РПЗУ) приведена на рис.92.

|

|

Рис.92.Структурная схема полупроводниковых ЗУ.

Такая схема включает накопитель НК (матрица запоминающих элементов - ЗЭ), дешифратор строк DCX, дешифратор столбцов DCY, устройство записи УЗ, устройство считывания УС. устройство управления УУ.

Входные информационные сигналы DI поступают в устройство записи УЗ, которое служит для записи информации в ЗЭ накопителя. Выходные информационные сигналы DO считываются из БИС ЗУ через устройство считывания УС.

Управляющие сигналы C̅S̅ R̅A̅S̅, C̅A̅S̅, W̅R̅/RD поступают в устройство управления УУ и устройство записи УЗ и определяют режим работы БИС ЗУ (запись, хранение, считывание информации).

Адресные сигналы A0,...,An-1 поступают на схемы дешифрации DCX и ОСУ, которые определяют к какому элементу памяти накопителя производится обращение в соответствии с заданным кодом адреса. Таким образом DCX и ОСУ указывают номер строки и номер столбца, где располагается ЗЭ. Выходные схемы связаны с устройством считывания УС, которое служит для усиления считанной из накопителя информации и передачи её на выход DO. Во многих случаях выходные схемы имеют возможность передачи трёх логических состояний: 1; 0; и состояния высокого сопротивления на выходе ZК что облегчает объединение по выходу БИС ЗУ в системах с шинной организацией передачи данных.

Входы и выходы ЗУ имеют следующие обозначения:

DI - данные входные;

D0 - данные выходные;

CS - выбор микросхемы;

WR - писать;

RD - читать;

RAS - выбор адреса строки;

CAS - выбор адреса столбца.

Входы записи и считывания объединены. Поэтому сигнал WR/RD на входе микросхемы означает, что нулём (W̅R̅) осуществляется режим записи, а единицей по этому же входу (RD) - режим чтения.

Структурная схема ПЗУ отличается от приведённой лишь отсутствием устройства записи УЗ.

5.3. Оперативные запоминающие устройства (ОЗУ).

ОЗУ предназначены для записи, хранения и считывания информации. Они используются для введения в процессор текущих результатов или данных, полученных в процессе работы. По способу хранения информации ЗУ подразделяются на статические и динамические.

Элементы памяти статических ОЗУ представляют собой бистабильные элементы. Они управляются потенциальными сигналами. Считывание информации производится без её разрушения.

В динамических ОЗУ в качестве запоминающего элемента используется конденсатор, в котором информация хранится в виде заряда. Заряд на запоминающем конденсаторе с течением времени уменьшается за счёт токов утечки. Для восстановления заряда требуется периодическая подзарядка (регенерация) накопительного конденсатора, т.е. для управления требуются импульсно-потенциальные сигналы. При считывании информация, как правило, разрушается, но за счёт регенерации снова восстанавливается. Динамические ОЗУ выполняются на п-МОП-транзисторах, имеют высокую степень интеграции, эффективны для построения ОЗУ большой ёмкости.

Статические ОЗУ на биполярных транзисторах.

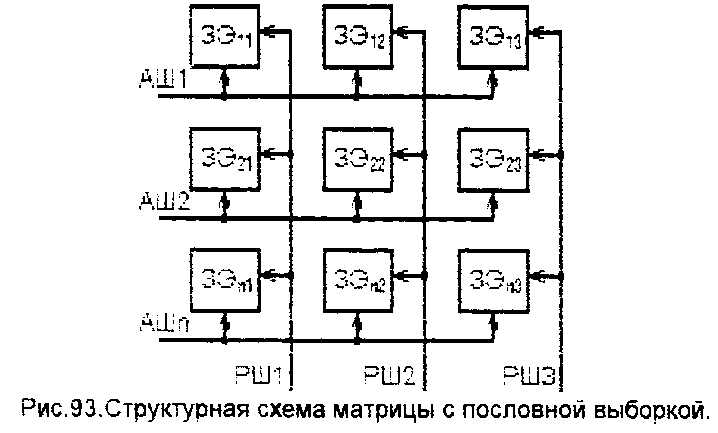

Такие ОЗУ представляют собой матрицу запоминающих элементов, каждый из которых может быть установлен в одно из двух устойчивых состояний. Таким элементом обычно является триггер. Из ЗЭ строится накопительная матрица памяти. Построение матрицы определяется способом выборки ЗЭ для записи или считывания информации. Структурная схема матрицы с пословной выборкой и одной ступенью дешифрации приведена на рис.93.

|

|

Рис.93.Структурная схема матрицы с пословной выборкой.

Одна строка образует слово из m разрядов. Выходами дешифратора строк DCX служат адресные шины АШ.

Как видно из схемы (рис.93), АШ связаны с каждым ЗЭ одного слова, в то время как разрядные шины РШ имеют связь с ЗЭ одноимённого разряда всех слов.

При наличии на адресной шине сигнала выборки, соответствующего высокому уровню, состояние каждого из ЗЭ в этом слове может быть считано по разрядным шинам. Если необходимо записать информацию по выбранному адресу, то в режиме записи на разрядные шины подаётся записываемая информация (электрические сигналы "Гили "О"), которые попадают на каждый из запоминающих элементов i-й строки.

При двухкоординатной выборке (см.рис.94) применяют две ступени дешифрации (DCX и DCY).

|

|

Рис.94.Структурная схема матрицы с двухкоординатной выборкой.

Как видно из схемы ЗЭ выбирается с помощью двух адресных шин АХ и АУ. Сигналом выборки является сигнал высокого уровня на адресных шинах АХ и АУ. При наличии АХ1=АУ1=”1” в режиме считывания будет выбран только ЗЭ1. Его состояние (0 или 1) считывается по общей разрядной шине РШ. Чтобы записать информацию в тот же элемент ЗЭ1, необходимо при АХ1=АУ1=”1” в режиме записи на разрядную шину РШ подать необходимый уровень напряжения.

Запоминающие элементы ОЗУ.

Статический элемент.

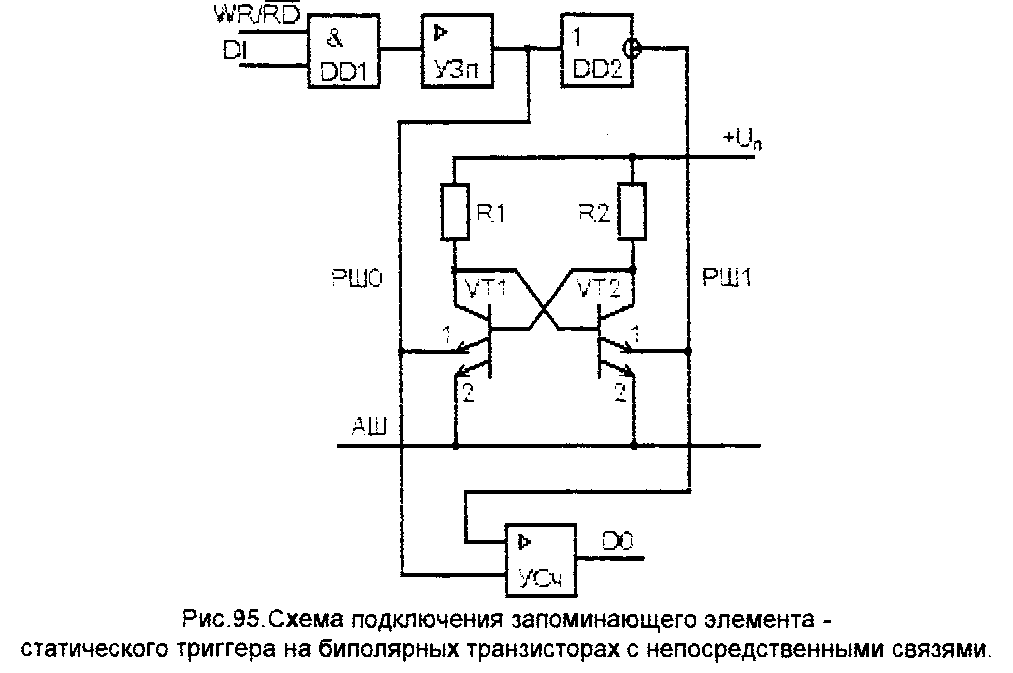

В полупроводниковых ОЗУ широко используются запоминающие элементы. Рассмотрим статический запоминающий элемент памяти (рис.95).

Записываемая информация подаётся на вход DI. Выходная информация считывается по линии DO. WR/RD - вход разрешения записи или считывания. Разрядные шины РШО и РШ1 служат для записи и считывания кода 0 или 1 соответственно. К каждой разрядной шине подключены усилитель записи (УЗп) и усилитель считывания (УСч). Адресная шина АШ служит для выборки информации из запоминающего элемента ОЗУ.

Примем, что триггер находится в состоянии 0, если транзистор VT1 открыт, aVT2 - закрыт; а если триггер находится в состоянии 1, то транзистор VT1 закрыт, aVT2 - открыт.

Режим хранения - в этом режиме ЗЭ не выбран и адресная шина имеет уровень логического 0. Разрядные шины имеют более высокий потенциал, поступающий с выхода усилителя записи (УЗп). Поэтому ток открытого транзистора протекает через нижний (адресный) эмиттер 2 на адресную шину и на "землю".

Режим записи - в этом режиме происходит выборка ЗЭ и на адресную шину подаётся уровень логической 1. Адресный эмиттер заперт, а коллекторный ток открытого транзистора протекает через его разрядный эмиттер 1, что даёт возможность выполнить операцию записи информации.

Если, например, триггер хранит 0, то при записи 0 с выхода усилителя записи на разрядный эмиттер 1 открытого транзистора VT1 поступает потенциал U0, под воздействием которого триггер не изменит своего состояния, т.е. останется в состоянии 0.

При записи 1 в триггер, хранящий код О, за счёт элемента DD2 на разрядный эмиттер 1 закрытого транзистора VT2 будет поступать потенциал U0 и транзистор VT2 откроется. При этом транзистор VT1 закроется, т.е. триггер установится в состояние 1.

Рис.95.Схема подключения запоминающего элемента-статического триггера на биполярных транзисторах с непосредственными связями

Режим считывания - в этом режиме вновь происходит выборка ЗЭ - адресная шина получает высокий потенциал и при считывании информации (кода 0 или 1) коллекторный ток открытого транзистора (VT1 или VT2) будет протекать через его разрядный эмиттер 1 и входную цепь усилителя считывания (УСч), формирующего на выходе сигнал, соответствующий уровню логического 0 или 1. Для того чтобы при считывании бита информации коллекторный ток открытого транзистора не ответвлялся в цепь усилителя записи (УЗп), на его входе устанавливают потенциал, запирающий усилитель записи (УЗп). При считывании разрушение информации в запоминающем элементе - триггере не происходит.

В случае необходимости микросхемы ЗУ можно объединить, увеличивая тем самым ёмкость памяти. Для этого они имеют специальный вывод - "Выбор микросхемы" - (CS).

Статический элемент на КМДП-транзисторах.

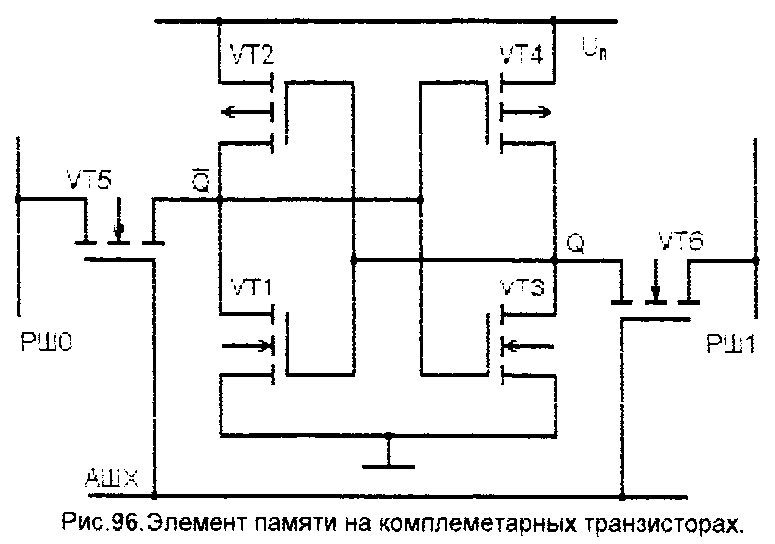

Элемент статического типа на КМДП-транзисторах приведён на рис.96.

Рис.96.Элемент памяти на комплеметарных транзисторах.

Наиболее распространённый вариант ЭП - триггер, образованный двумя перекрёстно соединёнными инверторами на КМДП-транзисторах.

Режим хранения - в этом режиме дешифратор OCX поддерживает на адресной шине АШХ низкий потенциал. Проходные транзисторы VT5, VT6 закрыты и элемент памяти сохраняет ранее установленное состояние.

Режим записи - в режиме выборки потенциал на шине АШХ выбираемой строки повышается, открывая проходные транзисторы VT5 и VT6. При записи информации дешифратор DCY в зависимости от значения поступившего сигнала DI формирует на шинах РШО и РШ1 выбранного столбца парафазные сигналы. Через открытые транзисторы VT5, VT6 эти сигналы поступают на входы запоминающего элемента, устанавливая его в требуемое состояние Q = DI. Если DI = 0, то на РШ0 устанавливается высокий потенциал U0≈ Un а на РШ1 - низкий потенциал U1≈ 0. При этом открываются транзисторы VT2 и VT3. В результате устанавливается требуемое состояние ЭП: Q = 0.

Если Dl = 1, то на РШ0 устанавливается низкий потенциал U0 ≈ 0, а на РШ1 - высокий потенциал U1≈ Un. При этом открываются транзисторы VT1 и VT4, запираются VT2 и VT3. И элемент памяти ЭП устанавливается в состояние: Q = 1. Выходы дешифратора DCY, соединённые с разрядными шинами невыбираемых столбцов, в режиме записи устанавливаются в отключенное состояние. Поэтому на выходе DCY используются каскады с тремя состояниями.

Режим считывания - в этом режиме потенциал на шине АШХ выбираемой строки повышается, открываются транзисторы VT5, VT6. При этом на шинах РШО и РШ1 устанавливаются потенциалы, соответствующие состоянию элемента памяти, который подключается к выходу DO микросхемы.

В режиме хранения такой элемент памяти потребляет ничтожно малую мощность, что является важнейшим преимуществом микросхем памяти на комплеметарных структурах.

Однако значительно превосходя остальные микросхемы памяти по экономичности. КМДП-микросхемы уступают биполярным микросхемам по быстродействию.

В настоящее время информационная ёмкость статических КМДП-микросхем памяти достигает сотен килобит.

Элемент памяти динамического типа.

Принцип действия элементов памяти динамического типа основан на хранении информации

с помощью конденсаторов. Схема такого элемента приведена на рис.97.

Рис.97.Динамический запоминающий элемент на МДП-транзисторах.

Паразитная ёмкость Сn затвора транзистора VT3 определяет содержимое хранимой запоминающим элементом информации. Отсутствие заряда означает хранение 0, а его наличие - хранение 1.

АХ - адресная шина элемента. D - информационная шина У. УСч - усилитель считывания.

Режим хранения - в этом режиме напряжение на адресной шине близко к нулю. Поэтому транзисторы VT1 и VT2 закрыты и конденсатор Сп отключен от шины. У на конденсаторе сохраняется установленное при записи напряжение U1 или U0. В случае хранения 1 конденсатор будет постепенно разряжатся вследствие существования токов утечки в подложку. Обычно это обратный ток р-п перехода транзистора.

Если же хранится логический 0, а напряжение на шине У положительно, конденсатор будет постепенно заряжаться предпороговым током транзистора. Поэтому необходимо периодическое восстановление исходного напряжения U1 или U0 на конденсаторе, называемое регенерацией. Она осуществляется путём считывания информации с элемента памяти, преобразования её в напряжение U1 или U0 с помощью усилителя считывания и в последующей записи этого напряжения в элемент памяти. Регенерация производится одновременно для всех элементов одной строки.

Режим записи - в этом режиме на шине У устанавливается напряжение U1 или U0, а затем подаётся положительный импульс выборки на шину АХ. Транзистор VT1 открывается, и на конденсаторе устанавливается то же напряжение, что и на шине У.

При записи кода 0 на информационную шину У подаётся уровень логического О (D = 0) и ёмкость Сп, если она имела заряд, будет разряжаться через открытый транзистор VT1, т.е. потенциал точки А становится равным 0 и транзистор VT3 будет закрыт.

При записи кода 1 на D = 1 и ёмкость Сn заряжается через открытый транзистор VT1 до потенциала, превышающего пороговое напряжение транзистора VT3. Транзистор VT3 открывается и удерживается в открытом состоянии положительным потенциалом точки А. При записи кода транзистор VT2 остаётся в закрытом состоянии.

Режим считывания - при считывании бита информации на шине АХ устанавливается напряжение считывания – UСч которое открывает транзистор VT2. При считывании 1 ёмкость Сп будет разряжатьсячерез открытые транзисторы VT2 и VT3. Происходит изменение потенциала точки В. что воспринимается усилителем считывания как сигнал кода 1.

При считывании кода 0 ёмкость Сп разряжена и транзистор VT3 закрыт. Поэтому при открытом транзисторе VT2 потенциал в точке В не изменяется и с выхода усилителя считывания (УСч) будет выдан код 0 на информационную шину.

Усилитель считывания является дифференциальным, на один его вход подаётся опорное напряжение, а на другой - сигнал с шины столбца (информационная шина У). Поэтому приведённая схема элемента динамического типа (рис.97) является упрощённой.

Динамические элементы памяти потребляют мощность только во время переходных процессов перезарядки конденсатора Сп при регенерации, записи или считывании. Поэтому БИС памяти динамического типа характеризуются малой мощностью, потребляемой главным образом схемами управления и считывания. Простота элемента памяти обуславливает его малую площадь и высокую информационную ёмкость БИС.