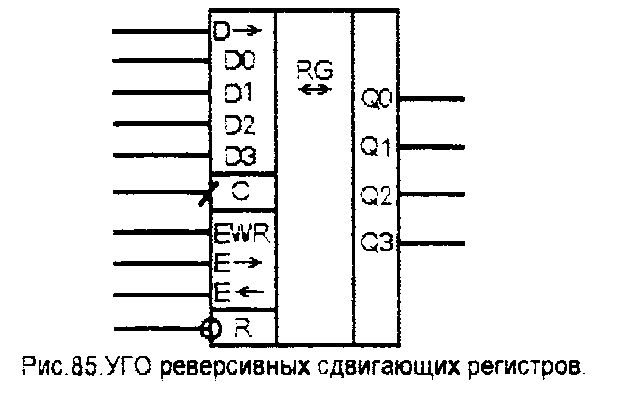

Комбинационная схема задана полностью, если известен закон функционирования, который представляется системой переключательных функций.

Рис.33. УГО комбинационной схемы

Рассмотрим комбинационную схему. Закон функционирования данной КС описывается переключательными функциями:

Анализ комбинационной схемы - это описание функционирования заданной схемы переключательными функциями. Анализ комбинационной схемы производится в следующем порядке:

1. Последовательно описывая работу каждого элемента КС переключательной функцией, получаютпереключательные функции, которые описывают закон функционирования всей КС.

2. Проводится анализ полученных переключательных функций с целью упрощения схемы.

Синтез - это проектирование схемы, реализующий заданный закон функционирования комбинационной схемы. Синтез КС проводится в следующем порядке:

1. Записать переключательную функцию КС в полном базисе.

2. Произвести минимизацию записанной переключательной функции.

3. Записать полученную после минимизации функцию в необходимом базисе.

4. Построить полученную переключательную функцию.

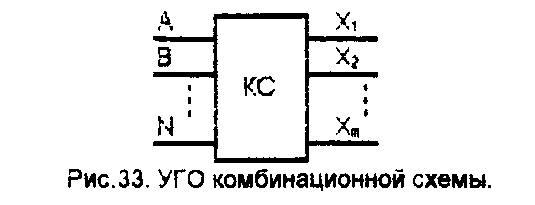

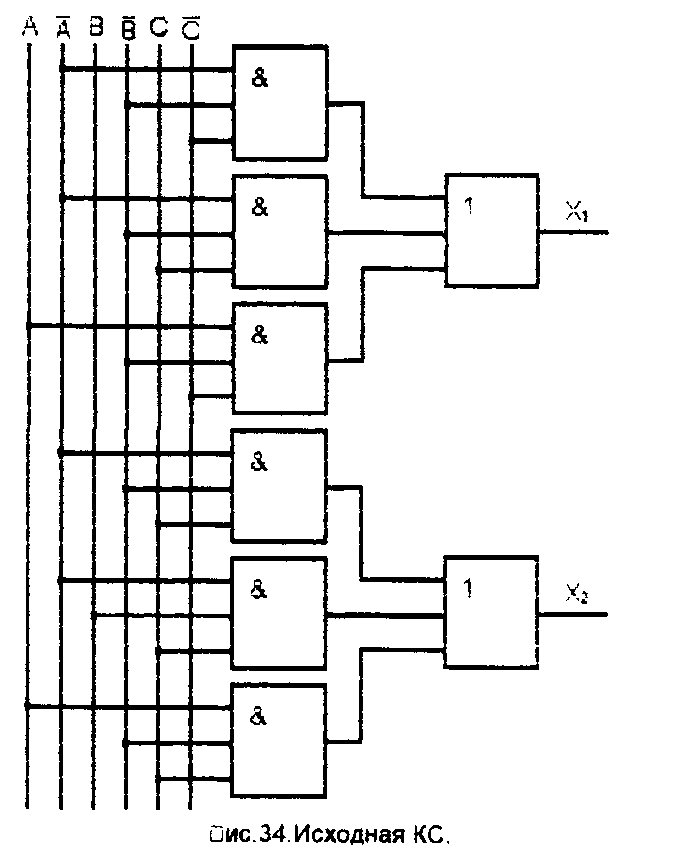

Пример: Произвести анализ комбинационной схемы: (см.рис.34).

Описываем работу каждого логического элемента КС переключательной функцией:

X1=A̅B̅C̅vA̅B̅CvAB̅C̅

X2=A̅B̅CvA̅BCvAB̅C

1. Производим анализ полученных выражений:

2. Строим электрическую схему: (см.рис.35)

Рис.34.Исходная КС. Рис.35.КС после анализа

Раздел 3. Комбинационные устройства.

3.1. Дешифратор.

Дешифратор - комбинационная схема, содержащая п входов и 2П выходов и преобразующая n-разрядное двоичное число в соответствующий управляющий сигнал, который возникает только на одном из его выходов. Дешифратор представляет собой совокупность схем совпадений, формирующих управляющий сигнал на одном из выходов, в то время как на остальных выходах сигналы отсутствуют. Выходы дешифратора имеют нумерацию, совпадающую с десятичным представлением двоичного числа.

Число элементов одноступенчатого дешифратора определяется числом выходов.

По способу организации дешифрации слова дешифраторы подразделяются на:

1. Одноступенчатые (линейные).

2. Многоступенчатые (прямоугольные, пирамидальные).

Дешифратор, имеющий для n-разрядного числа 2П выходных шин, называется полным дешифратором.

Дешифраторы используются для преобразования двоичных кодов в управляющие сигналы для различных устройств ЭВМ.

Матричные или линейные дешифраторы.

Линейный дешифратор является одноступенчатым, т.к. при его построении используют конъюнкторы, число входов которых равно разрядности входного слова.

Прямые и инверсные значения переменных обычно поступают на входы дешифратора с прямых и инверсных выходов триггеров, регистра, на котором записывается входная комбинация переменных.

Схема, представленная на рис.36, реализует следующие переключательные функции:

Y0=X̅2X̅1X̅0 Y4=X2X̅1X̅0

Y1=X̅2X̅1X0 Y5=X2X̅1X0

Y2=X̅2X1X̅0 Y6=X2X1X̅0

Y3=X̅2X1X0 Y7=X2X1X0

В интегральном исполнении матричные дешифраторы строятся на 3-4 входа.

На рис.36.37 приведены: функциональная схема матричного 3-х разрядного дешифратора, таблица возможных состояний дешифратора и его условное графическое обозначение.

Возможно построение дешифратора, у которого дешифрация входного слова осуществляется синхронизирующими сигналами. Такие дешифраторы принято называть синхронными дешифраторами.

Рис.36. Функциональная схема (а) и таблица переключений (б) линейного дешифратора

Шифратор.

Шифратор - это узел, преобразующий унитарный код на входе в некоторый позиционный код на выходе. Если выходной код является двоичным, то шифратор называется двоичным.

Рассмотрим принцип построения 8-входового двоичного шифратора. Закон функционирования такого шифратора можно задать таблицей истинности (таб.3.2)

|

|

Назначение такого шифратора - преобразовать входной код, изображающий десятичную цифру 0,1,2,...,7 логической "1" на соответствующем входе, в двоичный код.Переключательные функции, описывающие работу дешифратора, имеют вид:

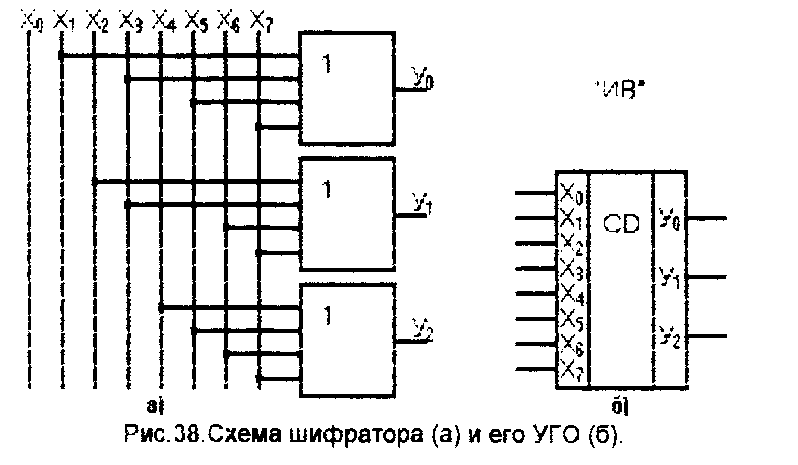

На рис.38 приведена схема шифратора на восемь входов и его условное обозначение.

Рис.38.Схема шифратора (а) и его УГО (б)

С помощью шифратора возможно преобразование цифр десятичных чисел в двоичное представление с использованием любого другого двоично-десятичного кода.

Мультиплексоры.

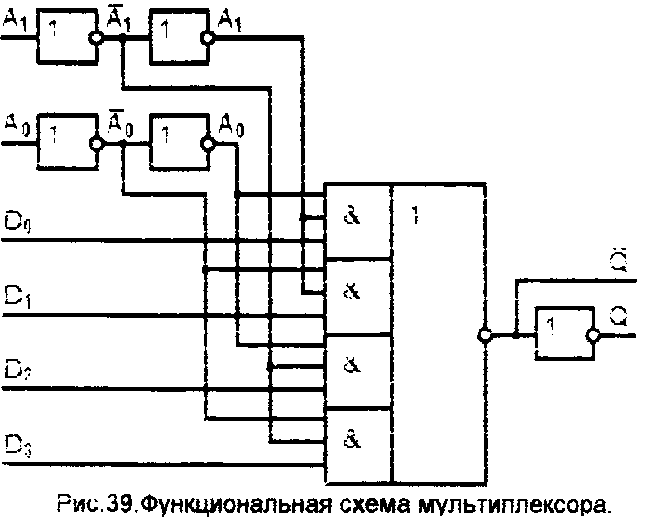

Мультиплексором называется функциональный узел, обеспечивающий передачу информации, поступающей по нескольким входным линиям связи на одну выходную линию. Выбор той или иной входной линии Di; осуществляется в соответствии с поступающим адресным кодом A0, А1…. При наличии п адресных входов можно реализовать М = 2П комбинаций адресных сигналов А|, каждая из которых обеспечивает выбор одной из М входных линий.

Каждому из информационных входов Dl мультиплексора присваивается номер, называемый адресом. Мультиплексор подключает один из входов, адрес которого задаётся двоичным кодом на адресных Аl входах, к выходу. Т о., подавая на адресные входы адреса информационных входов, можно передавать параллельные М-разрядные коды с этих входов на выход в последовательном коде.

Рассмотрим синтез 4-разрядного мультиплексора. Составим таблицу истинности:

На основании таб.3.3 составим переключательную функцию для его выхода:

Q=D0(A̅1A̅0)vD1(A̅1A0)vD2(A1A̅0)vD3(A1A0)

Рис.39.Функцианальная схема мультиплексора.

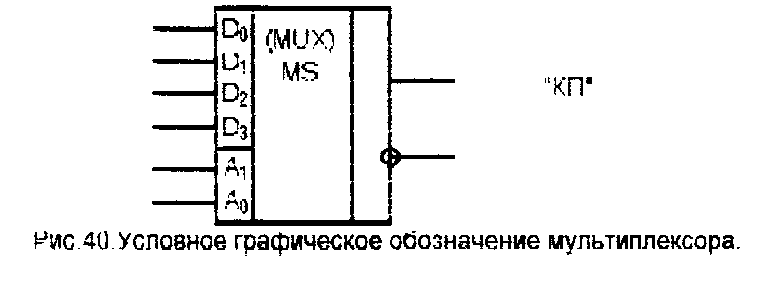

Рис.40.Условное графическое обозначение мультиплексора.

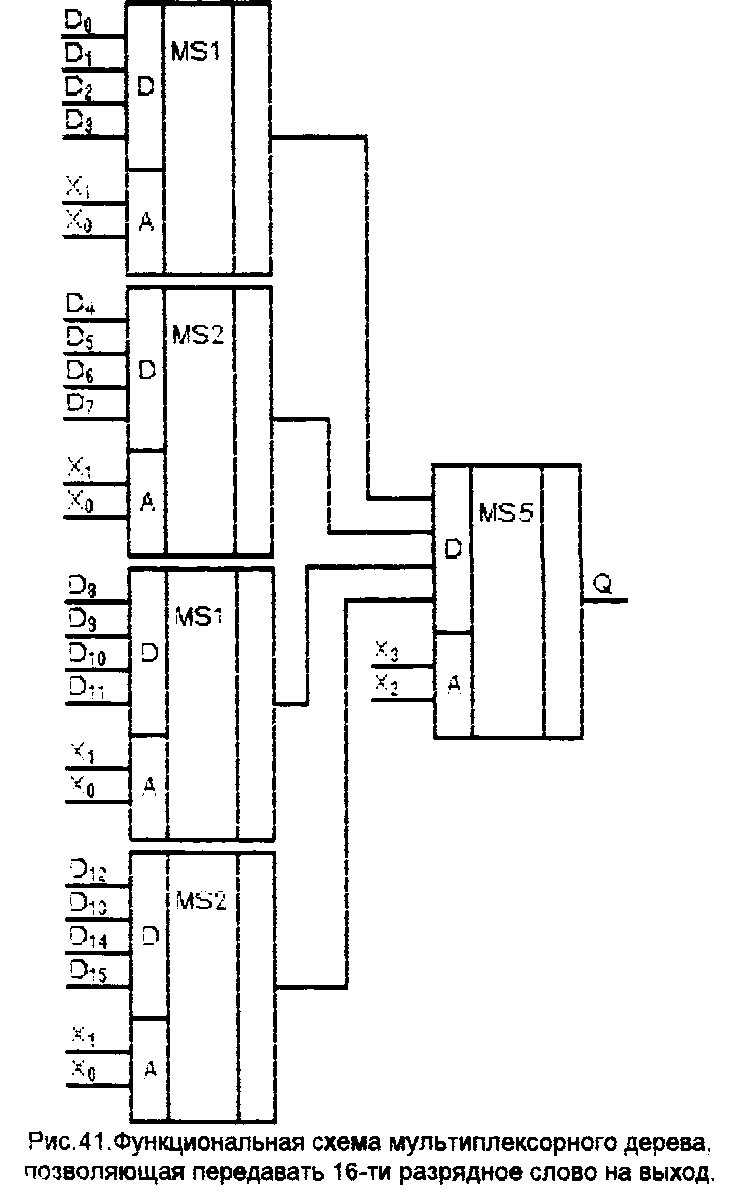

Рис.41.Функциональная схема мультиплексорного дерева,позволяющая передавать 16-ти разрядное слово на выход

Функциональные схемы мультиплексоров достаточно просты, они выпускаются в виде интегральных микросхем с четырьмя двухвходовыми, двумя четырёхвходовыми и одним восьмивходовым мультиплексорами в одном корпусе.

Для передачи на выход многоразрядных входных данных в параллельной форме используется параллельное включение мультиплексоров по числу разрядов передаваемых данных. Такое включение мультиплексоров называется мультиплексорным деревом(рис.41).

Например, чтобы передать на выход седьмой разряд следует подать на MS2 XiXq = 11 и на MS5 Х3Х2 = 01

Демультиплексоры.

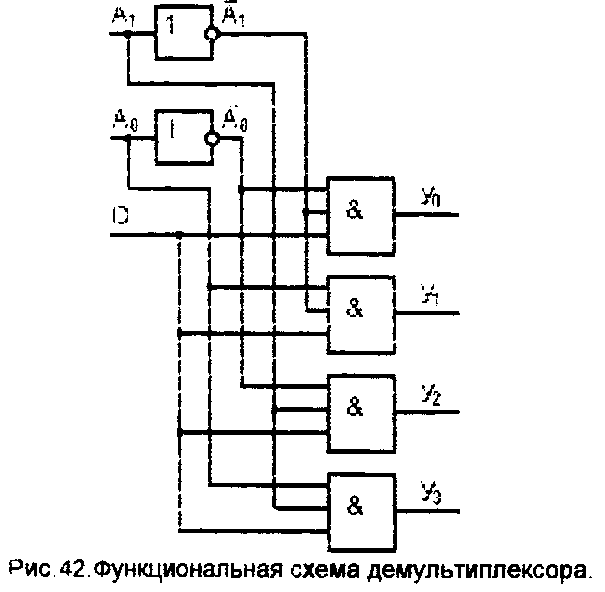

Демультиплексором называется функциональный узел, обеспечивающий передачу информации в одну из выходных линий в соответствии с принятым адресом. При этом на остальных выходных линиях поддерживается логический "О". То., демультиплексоры используются для восстановления мультиплексированной информации.

Демультиплексор имеет один информационный вход и несколько выходов. В этом случае вход подключается к выходу, имеющему заданный адрес. Рассмотрим принцип построения и работу демультиплексора, имеющего один вход и четыре выхода. Закон функционирования такого демультиплексора задан таблицей истинности:

Рассмотрим принцип построения и работу демультиплексора, имеющего один вход и четыре выхода. Закон функционирования такого демультиплексора задан таблицей истинности:

|

Используя таб. 3.4 можно легко записать переключательные функции для выходов приведённой на рис.42 схемы демультиплексора: |

Рис.42.Функциональная схема демультиплексора.

Условное обозначение демультиплексора имеет вид (рис.43).

Рис.43.УГО демультиплексора.

При D = 1 демультиплексор выполняет функции полного дешифратора, реализуя на на выходах минтермы адресных переменных А0,…,Аn-1.

Путём последовательного включения мультиплексоров и демультиплексоров реализуются различные схемы коммутаторов, соединяющих источники и приёмники информации в соответствии с поступающими адресами. На рис.44 представлена схема простейшего коммутирующего устройства.

Демультиплексоры выполняются в виде отдельных интегральных схем. Если общее число выходов проектируемого демультиплексора превышает имеющееся в выпускаемых интегральных микросхемах, то используют параллельное подключение нескольких схем.

Рис.44.Пример коммутирующей схемы.

Рис.45.Функциональная схема 16-ти разрядного демультиплексорного дерева.

Сумматоры.

Основной операцией при выполнении арифметических действий в современных цифровых системах является сложение. Поэтому основным блоком операционных устройств обычно является сумматор.

Сумматор - это узел, в котором выполняется арифметическая операция суммирования цифровых кодов двух чисел.

Числа в любой позиционной системе счисления складываются поразрядно. Поэтому сложить любые двоичные числа можно при наличии узлов, реализующих суммирование цифр одного разряда слагаемых с учётом возможного переноса из соседнего младшего разряда.

По принятой системе счисления и кодирования различают сумматоры:

1. Двоичные.

2. Десятичные.

3. Двоично-десятичные.

По способу организации суммирования сумматоры могут быть:

1. Комбинационные.

2. Накапливающие.

По способу обработки многоразрядных чисел различают сумматоры:

1. Последовательные.

2. Параллельные.

3. Параллельно-последовательные.

Комбинационный полусумматор.

Полусумматор служит для сложения двух двоичных одноразрядных чисел. Схемы полусумматора строятся на простых логических элементах И. ИЛИ. НЕ. Искл. ИЛИ (рис.46)

Рис.46. Схемы (а,в) и таблица значений (б) для полусумматора.

По таблице значений переключательные функции для Si и Рi+1 в СДНФ имеют вид:

Полусумматор имеет два входа Ai и Вi и два выхода Si и Pi+1.

На выходе S; формируется цифра суммы данного разряда в соответствии с правилами сложения в двоичной системе счисления, а на выходе Pj+-| - единица переноса в старший

разряд

|

|

Рис.47.Условное графическое обозначение полусумматора.

Одноразрядный комбинационный сумматор.

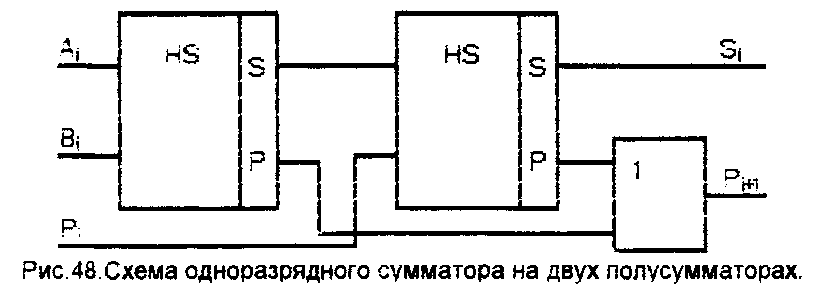

Одноразрядный комбинационный сумматор предназначен для суммирования трёх одноразрядных двоичных чисел.

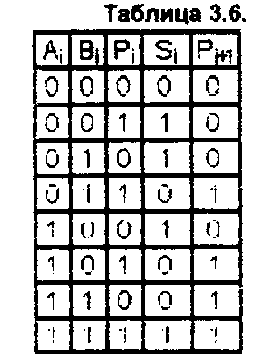

Таблица переключения для одноразрядного сумматора имеет вид (таб.3.6).

На основе таблицы переключений (таб.3.6) переключательные функции в СДНФ для Si и Pi+1 имеют следующий вид;

Схема сумматора состоит из двух последовательно соединённых полусумматоров, каждый из которых суммирует только два аргумента. Схемы приведены на рис.48.49.

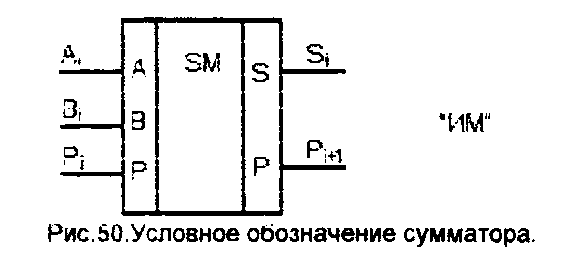

Сумматор имеет три входа Ai,Bi,Piи два выхода Siи Pi+1. На входы Aiи Biпоступают значения суммируемых цифрданного разряда, а на вход Pi - значение переноса из соседнего младшего разряда. Сумматор имеет два выхода, по одному из которых выдаётся сумма Si, а по второму Pi+1 - перенос в старший разряд.

Рис.48.Схема одноразрядного сумматора на двух полусумматорах.

Рис.49.Схема одноразрядного сумматора на простых логических элементах

Рис.50.Условное обозначение сумматора

Промышленные сумматоры строятся на сложных логических элементах; И-ИЛИ-НЕ, ИЛИ-HE, И-НЕ.

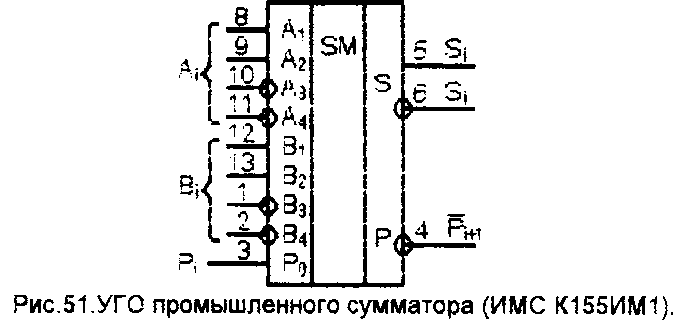

Сумматоры выпускаются в интегральном исполнении. Рассмотрим микросхему К155ИМ1, которая представляет собой быстродействующий одноразрядный сумматор.

Рис.51.УГО промышленного сумматора (ИМС К155ИМ1)

Сумматор имеет четыре входа А и В, обеспечивающие приём информации, вход переноса Pj с предыдущего разряда, прямой и инверсный выходы суммы Si и инверсный выход переноса Pj+1 в следующий разряд. Наличие у микросхемы инверсных входов A3, А4 и В3, В4 даёт возможность использовать сумматор для выполнении операции вычитания. В этом случае вычитаемое в прямом коде подаётся на один из инверсных входов, инвертирование входных сигналов производится внутри схемы.

При выполнении операции сложения на инверсные входы А3, А4 и В3, В4 подаётся уровень логической "1", при выполнении операции вычитания прямые входы А1, А2 и B1, В2 соединяются с "землёй".

Многоразрядные комбинационные сумматоры.

В цифровых системах обычно обрабатываются многоразрядные числа, поэтому в их состав включаются многоразрядные сумматоры, которые строятся на базе одноразрядных сумматоров, соединённых цепями переноса.

Многоразрядные сумматоры могут быть параллельными и последовательными.

Параллельный сумматор комбинационного типа строится на основе каскадного соединения одноразрядных комбинационных сумматоров. Различают схемы с последовательным, параллельным и групповым переносом.

Рис.52.Структурная схема n-разрядного двоичного сумматора с последовательным переносом.

На практике для построения многоразрядного сумматора пользуются чередующей структурой, при которой в нечётных разрядах сумматора используются прямые входы A1t А2и В-|, В2и прямые выходы суммы Sj, а в чётных - инверсные входы А3, Д4 и В3, В4 и инверсные выходы суммы Sj. При выполнении операции суммирования на входе Р0 должен быть логический "0". Управляющий сигнал УС соответствует логической «1».

Поданный на управляющий вход сигнал УС = "0" переводит каждый из выходов сумматора в состояние логического "0" и сохраняет это состояние независимо от состояния информационных входов каждого разряда сумматоров.

Рис.53.Структурная схема 3-разрядного двоичного сумматора с последовательным переносом на ИМС

Последовательный сумматор преобразует последовательные коды слагаемых в последовательный код их суммы.

Десятичные сумматоры.

Принципиально возможно построение схем сумматоров, работающих в любой системе счисления, отличной от двоичной. На практике наибольшее распространение получили

двоично-кодированные десятичные сумматоры.

|

|

Рис.54.УГО одноразрядного десятичного сумматора.

На входы А0-А3 сумматора подаётся двоичный код одной из суммируемых десятичных цифр, на входы BQ-B3 - двоичный код второй десятичной цифры и на вход Pj - значение переноса из соседнего младшего десятичного разряда. На выходах S0-S3 образуется двоичный код десятичной цифры данного разряда суммы, а на выходе Pi+1 - значение переноса в соседний старший десятичный разряд.

Для выполнения действий над десятичными числами наиболее широко используется код с избытком 6. При выполнении логических операций в этот код преобразуются числа, хранящиеся в оперативной памяти в коде 8-4-2-1. Результат операции также передаётся в ОП в коде 8-4-2-1.

Для сложения многоразрядных десятичных чисел могут быть использованы как параллельные, так и последовательные сумматоры, в этом случае схемы десятичных сумматоров выполняют функции, аналогичные функциям двоичных сумматоров в многоразрядных схемах.

3.6. Арифметико-логические блоки.

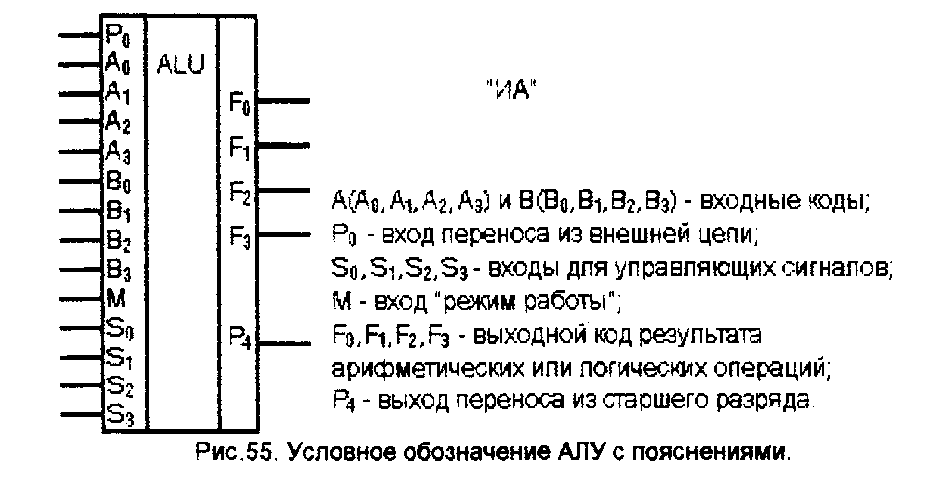

Арифметико-логическим устройством (АЛУ) называется функциональный блок, выполняющий заданный набор арифметических и логических операций над двумя многоразрядными операндами. АЛУ является основным блоком операционных устройств большинства современных цифровых систем.

Набор операций, выполняемых АЛУ, определяется в зависимости от предполагаемой области его использования. Обычно АЛУ выполняют полный набор логических функций двух переменных или его часть, состоящую из наиболее часто используемых функций: инверсии, конъюнкции, дизъюнкции, исключающего ИЛИ. В состав арифметических операций обязательно входят сложение и вычитание. В виде отдельных микросхем либо в составе БИС выпускаются секции АЛУ. выполняющие операции над 2-. 4-. 8-. 16разрядными операндами. Для обработки операндов большей разрядности параллельно включаются несколько секций АЛУ. На рис.55 приведено УГО АЛУ.

Рис.55.Условное обозначение АЛУ с пояснениями.

При управляющем сигнале М="0" АЛУ выполняет арифметические операции над п- разрядными входными двоичными числами А и В.

При М="Г АЛУ выполняет логические операции над функциями А и В (во всех разрядах выполняется одна и та же логическая операция).

Комбинация сигналов Sq,...,S3 определяет, какая именно математическая или логическая операция выполняется.

|

|

Типовой набор из 16 логических и 16 арифметических операций над операндами А и В, серийно выпущенных микросхем АЛУ имеет вид:

Преобразователи кодов.

Преобразователи двоичного кода.

|

|

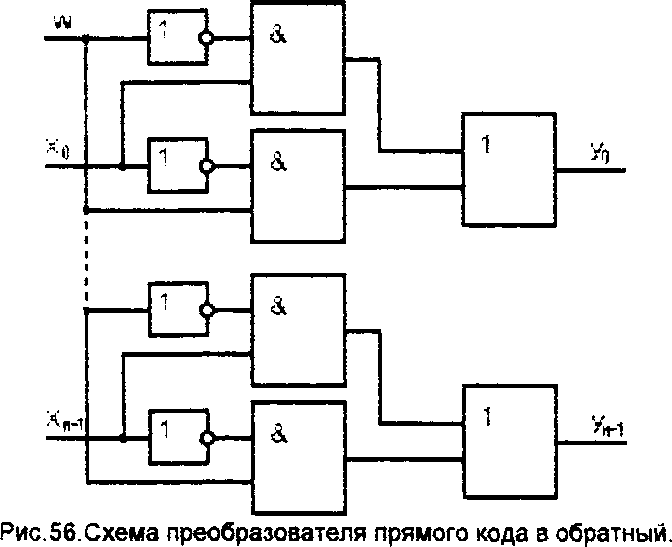

Рис.56.Схема преобразователя прямого кода в обратный.

Это узел, на выходе которого в зависимости от знака числа может быть получено двоичное

число как в прямом, так и в обратном или дополнительном кодах.

Рис.56.Схема преобразователя прямого кода в обратный.

Если на входы Xj преобразователя поступают положительные числа (w="0"), то с выходов У-, снимаются прямые коды двоичных чисел X. Если на входы Xj преобразователя поступают отрицательные числа (w=T), то с его выходов У-, снимаются обратные коды двоичных чисел.

Закон функционирования любого i-ro разряда преобразователя прямого кода в обратный можно представить таблицей переключений:

Рис.57.УГО преобразователя прямого кода в обратный.

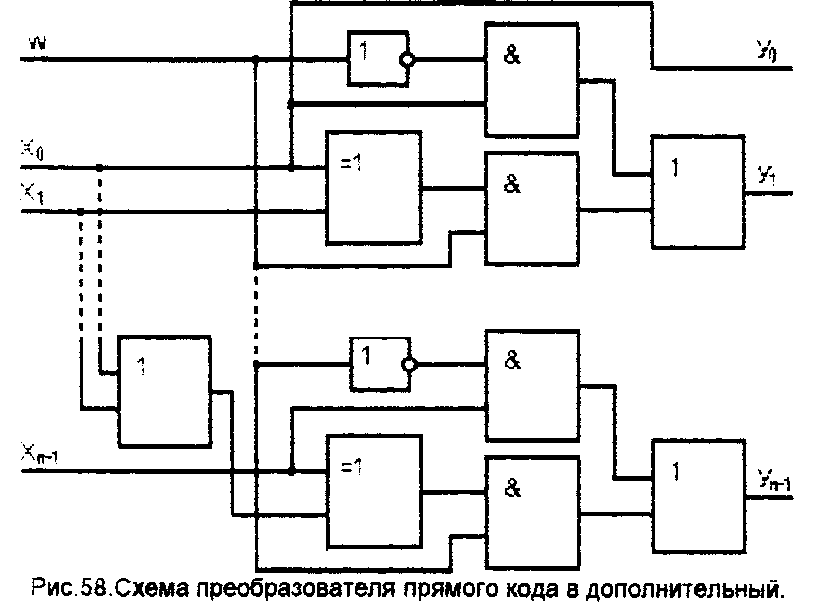

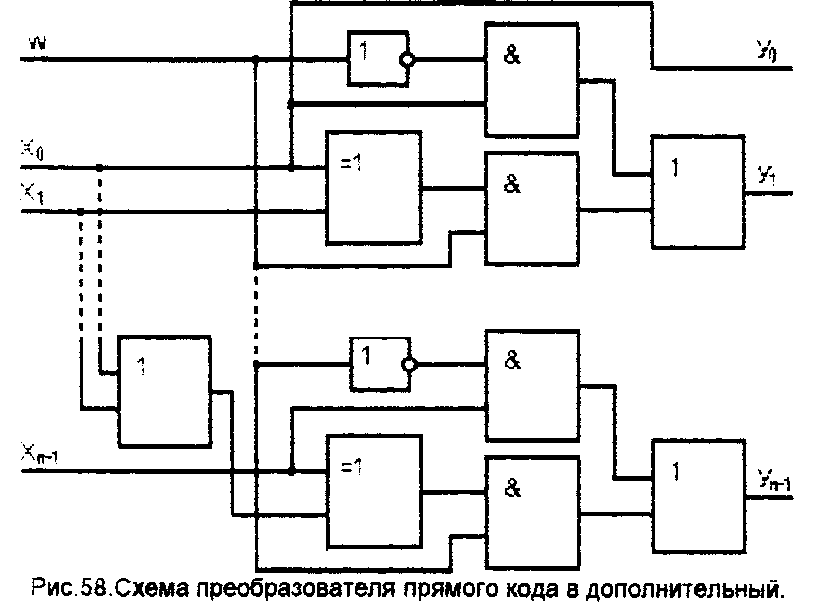

Можно построить схему преобразователя для преобразования прямого двоичного кода в дополнительный. Для образования дополнения отрицательного п-разрядного числа до величины 2П необходимо к инверсному значению кода числа прибавить единицу в младший разряд.

Для i-ro разряда преобразователя прямого кода в дополнительный с учётом знака числа переключательная функция имеет вид:

Рис.58.Схема преобразователя прямого кода в дополнительный.

При проектировании устройств ЭВМ различного назначения и для обеспечения совместной работы отдельных устройств используются и другие преобразователи кодов. С помощью преобразователей кодов можно преобразовать двоичный код в двоичнодесятичный, либо двоично-десятичный в двоичный.

Преобразователи для цифровой индикации.

В знакосинтезирующих устройствах печати, дисплеях цифровая информация образуется методом синтеза фигур из нескольких отрезков прямых. На рисунке показано, как получить

изображение всех десятичных цифр в виде отрезков прямых.

Каждый элемент фигуры светится либо не светится, в зависимости от значения соответствующей логической переменной, управляющей свечением данного элемента фигуры.

Десятичные цифры, отображение которых необходимо вызывать, задаются в десятичном коде. Таблица истинности для логических переменных, управляющих элементами индикации, имеет вид (таб.3.9).

|

|

С помощью карт Карно можно получить значения переключательных функций для управления элементами индикации.

На примере рассмотрим получение значения переключательной функции для управления элементом УЗ индикации.

|

|

Функциональная схема, реализующая выражение для УЗ может быть построена на логических элементах в любом базисе.

Раздел 4. Последовательностные устройства.

Триггеры.

Триггером называют элементарный цифровой автомат, который имеет два устойчивых состояния. Одному из этих состояний присваивается значение 1, а другому - 0, Состояние триггера и значение хранимой двоичной информации определяются прямым и инверсным выходными сигналами. Если на прямом выходе Q имеется потенциал соответствующий логической 1, то триггер находится в единичном состоянии, если О-в нулевом состоянии. Потенциал на инверсном выходе противоположен главному выходу.

Триггеры классифицируются по следующим признакам:

1. По способу записи информации различают асинхронные и синхронные триггеры. В асинхронных триггерах изменение состояния происходит при подаче сигналов на информационные входы. В синхронных (тактируемых) триггерах имеются кроме информационных входов один или несколько дополнительных для сигналов управления. Состояние таких триггеров изменяется при подаче синхронизирующих сигналов в соответствии со значением сигналов на информационных входах.

2. По способу управления информацией различают триггеры со статическим, динамическим, одноступенчатым и многоступенчатым управлением.

При статическом управлении переключение триггеров вызывается уровнями сигналов, поступающих на информационные входы; при динамическом управлении - изменением уровней сигналов на информационных входах. Триггеры с одноступенчатым управлением имеют одну ступень управления, а с двухступенчатым - две ступени запоминания информации. Синхронные триггеры с одноступенчатым управлением называются однотактными. а с двухступенчатым - двухтактными.

3. По способу организации логических связей, определяющих особенности функционирования, различают RS,D,T,JK и другие типы триггеров.

Основными параметрами триггеров являются:

1. Максимальная длительность входного сигнала;

2. Время задержки переключения триггера;

3. Разрешающее время триггера

Триггер на дискретных элементах.

Схема триггера на дискретных элементах имеет вид (рис. 59).

|

|

Рис.59.Триггер на дискретных элементах.

Если на вход А подать сигнал высокого уровня, то транзистор VT1 будет находится в закрытом состоянии и с выхода Q будет сниматься сигнал низкого уровня (примерно -Еп).

Этот же сигнал будет открывать транзистор VT2, и с инверсного выхода будет сниматься сигнал высокого уровня (более положительный, чем -Еп).

Если на вход В подать сигнал высокого уровня, то это приведёт к тому, что транзистор VT2 закроется, а транзистор VT1 откроется, и на главном выходе Q будет сигнал высокого уровня, а на инверсном выходе - низкого уровня. Эти два состояния будут устойчивыми в период отсутствия управляющих сигналов на входах А и В. Подача сигналов высокого уровня на входы А и В одновременно приводит триггер в неустойчивое состояние работы.

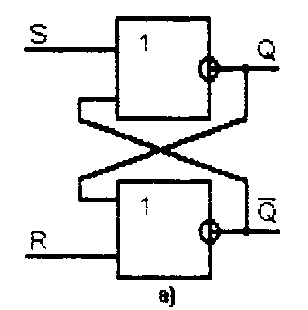

Триггер на логических элементах.

Выше рассмотренный триггер можно построить на элементах типа ИЛИ-HE, либо И-НЕ

Выше рассмотренный триггер можно построить на элементах типа ИЛИ-HE, либо И-НЕ

Рис.60.Схема(а),таблица значений(в) и временные диаграммы(г) асинхронного RS-триггера на логических элементах ИЛИ-НЕ

|

|

Рис.61.Схема (а), УГО (б), таблица значений (в) и временные диаграммы (г) асихронного RS-триггера на логических элементах И-НЕ.

На рис.60 при R=1 и S=0 триггер устанавливается в нулевое состояние (Q=0), при R=0 и S=1 - в единичное состояние (Q=1), при R=S=0 триггер сохраняет состояние, в котором он находился до поступления на его входы нулевых сигналов. При R=S=1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггерная схема превращается в два независимых инвертора, и при переходе к хранению информации триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

На рис.61 при R=1 при 5=0 триггер устанавливается в единичное состояние (0=1), при R=0 и 3=1 - в нулевое состояние (Q=Cty, при R=5=1 триггер сохраняет предыдущее состояние. Комбинация входных сигналов R=3=0 является запретной для данного триггера.

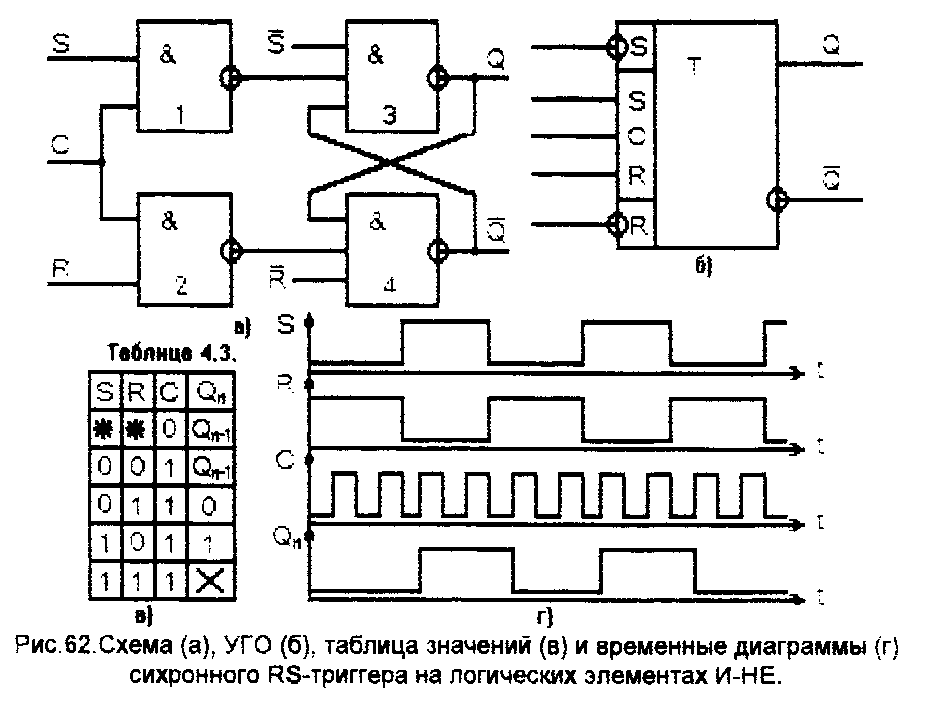

Синхронный однотактный RS-триггер.

На входы логического элемента сигналы не всегда поступают одновременно, т.к. перед этим могут проходить через разное число узлов, не обладающих к тому же одинаковой задержкой. Это явление называют состязаниями или гонками. В результате таких состязаний новые значения одних сигналов будут сочетатся с предыдущими значениями других сигналов, что может привести к ложному срабатыванию.

Это отрицательное явление можно устранить временным стробированием. когда на элемент кроме информационных сигналов подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы успевают установиться на входах.

|

|

Рис.62.Схема(а),УГО(б),таблица значений(в) и временные диаграммы (г) синхронного RS-триггера на логических элементах И-НЕ

Здесь элементы 1 и 2 образуют схемы входной логики синхронного управления RS- триггера. построенного на элементах 3 и 4.

Поскольку входная информация поступает через дополнительные элементы 1 и 2, то она может быть записана в триггер только при поступлении на синхронизирующий вход тактирующего сигнала. Т.о. синхронный триггер кроме входов R и S имеет вход синхронизации С. Закон функционирования данного триггера следующий: если на синхронизирующем входе действует уровень С=0, то триггер сохраняет своё состояние, т.е. триггер находится в режиме хранения, а если на синхронизирующем входе С=1, то триггер работает в режиме асинхронного RS-триггера. При отсутствии сигнала синхронизации триггер может быть установлен в состояние 0 или 1 подачей на дополнительные несинхронизирующие входы R-инверсное и S-инверсное сигналов, соответствующих логическому "О".

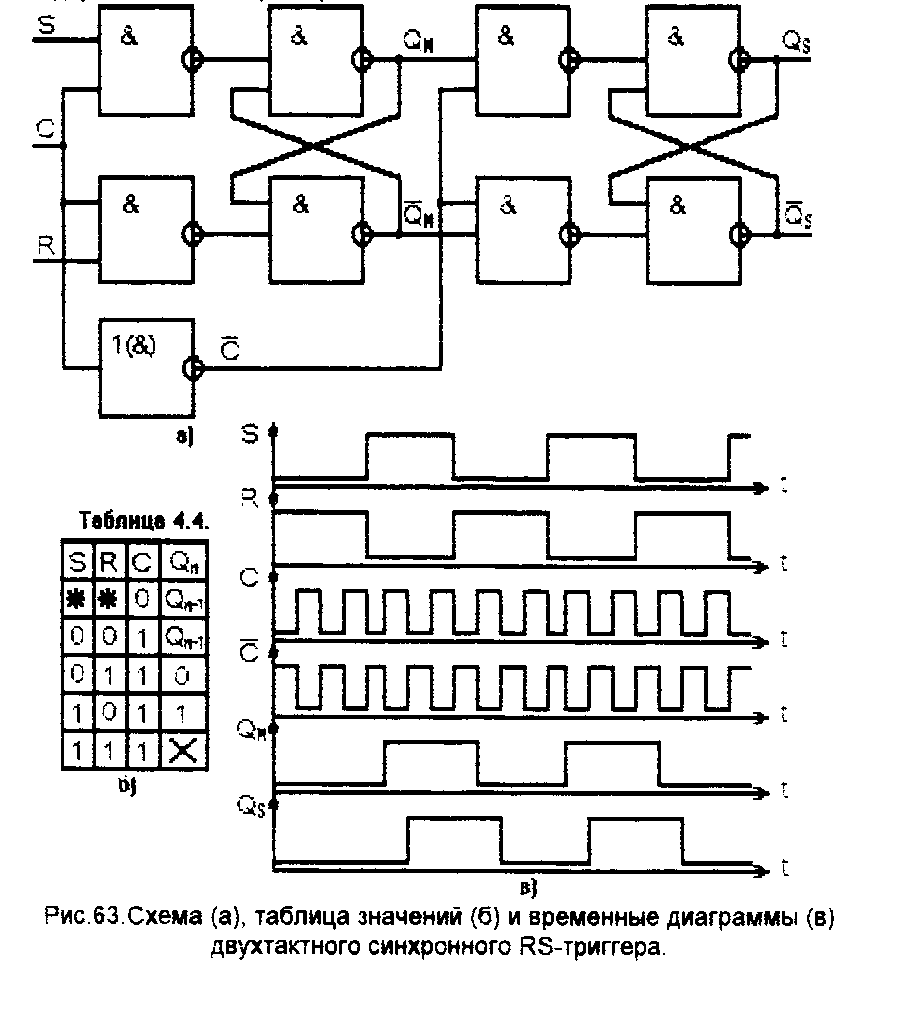

Синхронный двухтактный RS -триггер.

Устойчивая работа однотактных RS-триггеров в любой схеме возможно только при условии, что информация в триггер заносится после завершения передачи информации о прежнем его состоянии в другой триггер. Для этого приходится использовать две серии находящихся в противофазе синхроимпульсов. Подобный принцип обмена информацией реализован в двухтактных RS-триггерах.

Рис.63.Схема(а),таблица значений(б) и временные диаграммы(в) двухтактного синхронного RS-Триггера

Схема двухтактного синхронного RS-триггера состоит из двух однотактных RS- триггеров и инвертора в цепи синхронизации. Если на синхронизирующий вход триггера подаётся сигнал С=1, то входная информация, определяемая сигналами на R и S входах, заносится только в первый триггер. При этом второй триггер будет хранить предыдущюю информацию.

Как только импульс синхронизации примет значение С=0, первый RS-триггер перейдёт в режим хранения, а с инвертора уровень С-инверсное равный "1” запишет информационное состояние первого RS-триггера во второй RS-триггер.

Синхронный двухтактный триггер обычно имеет дополнительные асинхронные инверсные входы R и S, по которым он независимо от сигнала на синхронизирующем входе С переключается в состояние 0 или 1.

Условное обозначение рассмотренного триггера имеет вид (рис.64).

|

|

Рис.64.УГО двухтактного синхронного RS-триггера.

Таким образом разница между однотактным и двухтактным синхронными RS- триггерами со статическим управлением состоит в следующем: однотактный синхронный RS-триггер можно переключить, если С=1 и при этом изменить комбинацию на установочных входах с прежней (например R=0, S=1) на новую (R=1, S=0) или наоборот; в двухтактном синхронном RS-триггере при С=1 вторая ступень отключена от первой, а при С=0 первая ступень не принимает информацию с входов R и S.

Лишь при изменении сигнала на синхронизирующем входе С с 1 на 0 информация из первой ступени передаётся во вторую ступень и состояние выходов Q и Q-инверсное изменяется.

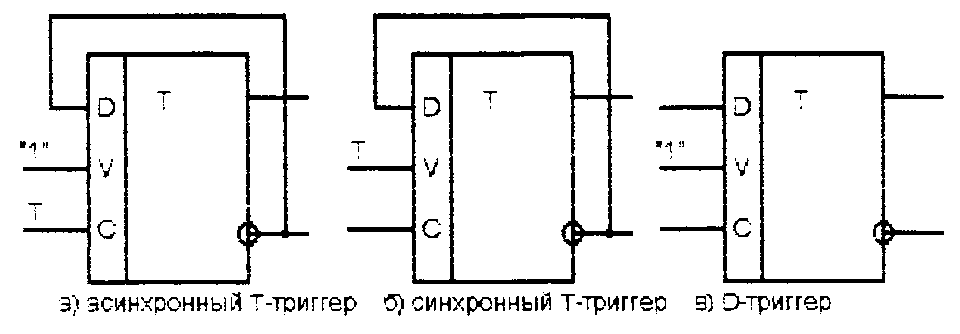

Т-триггеры.

Триггер этого типа имеет только один информационный вход Т, называемый счётным входом, и изменяет своё состояние после прихода на счётный вход Т каждого управляющего (счётного) сигнала.

Т-триггер реализует операцию сложения по mod 2, что и обусловило название триггера счётным триггером.

Сигнал на его выходе Q появляется в два раза реже, чем на входе Т, т е. Т-триггер может использоваться как делитель частоты.

1. Асинхронный Т-триггер - может быть построен на базе двухтактного синхронного RS-триггера; выход Q соединяется с информационным входом R, инверсный выход - с информационным входом S.

Информационным входом Т является синхронизирующий вход С.

|

|

Рис.65.Схема (а),таблица значений (б) и временные диаграммы (в) двухтактного асинхронного Т-триггера

В этой схеме поступление сигнала Т=1 по входу С приводит к записи в двухтактный RS- триггер состояния, противоположного предыдущему.

Сигнал на выходе триггера изменится только после завершения действия сигнала Т=1.

В данной схеме единичный входной сигнал представляется спадом сигнала Т=1.

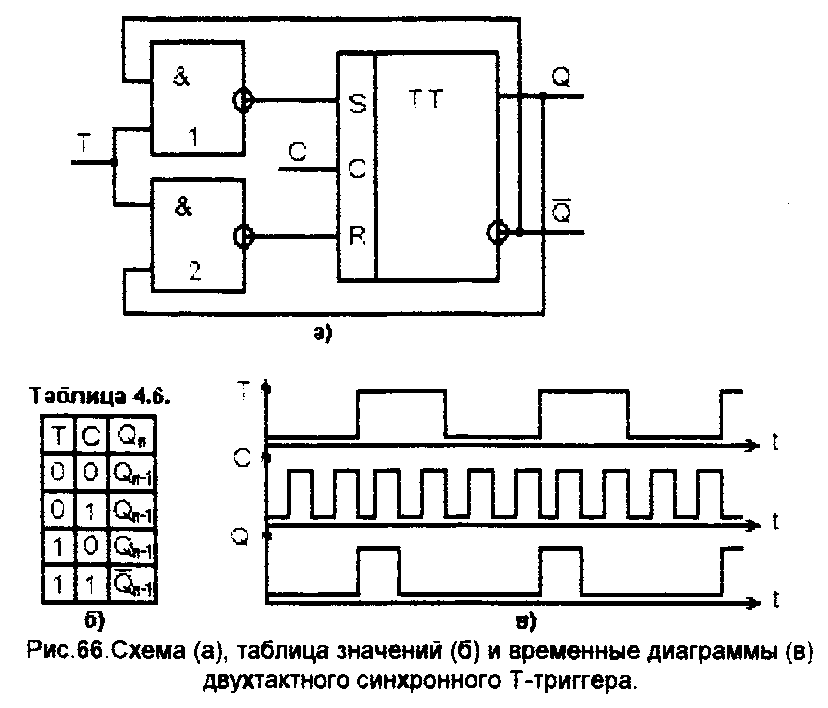

2. Синхронный Т-триггер - может быть построен на базе двухтактного RS-триггера с применением логических элементов И.

Рис.66.Схема (а),таблица значений (б) и временные диаграммы (в) двухтактного синхронного Т-триггера

При Т=0 наличие синхронизирующего сигнала С=1 не сможет вызвать переключение Т-триггера, т.к. входы R и S двухступенчатого RS-триггера заблокированы уровнем логического 0 с выходов элементов 1 и 2.

При наличии высокого уровня Т=1 каждый синхронизирующий сигнал на входе С=1 будет переключать триггер из одного состояния в другое, причём смена состояния происходит после окончания действия синхронизирующего сигнала на входе С (С=0). а электрических схемах Т-триггеры обозначается следующим образом (рис. 67).

|

|

Рис.67.УГО асинхронного(а) и синхронного(б) двухтактных Т-триггеров

D -триггеры

Состояние в синхронных триггерах может изменится только во время действия синхроимпульса. В промежутке между синхроимпульсами выходные напряжения постоянны. Это позволяет создать на основе синхронизируемых RS-триггеров триггеры задержки - D-триггеры. D-триггер может быть одноступенчатым или двухступенчатым.

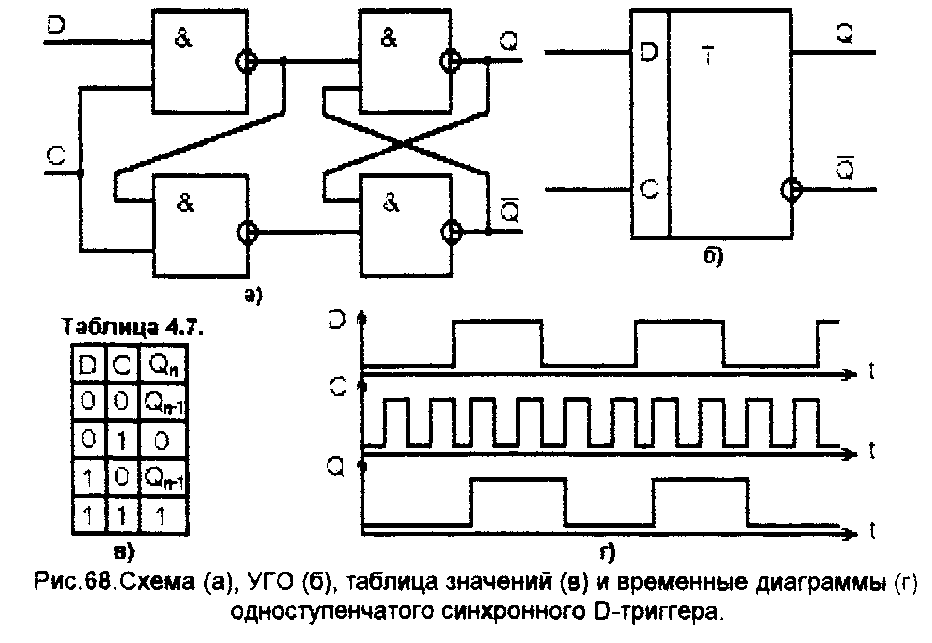

Рис.68.Схема(а),УГО(б),таблица значений(в) и временные диаграммы(г) одноступенчатого синхронного D-триггера

1. Одноступенчатый D -триггеримеет вид (рис.68).

При С=0 синхронный RS-триггер заблокирован уровнями логической 1 с выходов элементов И-НЕ. При С=1 уровень, поданный на информационный вход D, создаёт уровень логического 0 на входе S (D=1), либо на входе R (D=Q) асинхронного RS-триггера и триггер устанавливается в состояние, соответствующее логическому уровню на входе D.

Как видно из временной диаграммы одноступенчатый D-триггер задерживает распространение входного сигнала на время паузы между сигналами.

2. Двухступенчатый синхронный D-триггер обеспечивает задержку входного сигнала на период (на один такт) следования синхронизирующих сигналов.

|

|

Рис.69.Вариант построения(а),таблица значений(б) и временные диаграммы(в) двухступенчатого синхронного D-триггера.

Схема двухступенчатого синхронного D-триггера состоит из однотактного D-триггера и однотактного синхронного RS-триггера, тактируемых уровнем логической 1. и инвертора.

При С=0 информация со входа D не принимается в триггер T-j. Этот уровень через инвертор подаётся на синхронизирующий вход триггера Т2 и состояние триггера Т1 передаётся Т2.

При подаче на вход С уровня логической 1 на синхронизирующий вход триггера Т2 приходит логический 0 и связь между триггерами разрывается. Триггер Т1 при этом будет устанавливаться в состояние, соответствующее уровню на входе D. После окончания действия сигнала на входе синхронизации (С=0) производится передача состояния триггера T-j триггеру Т2.

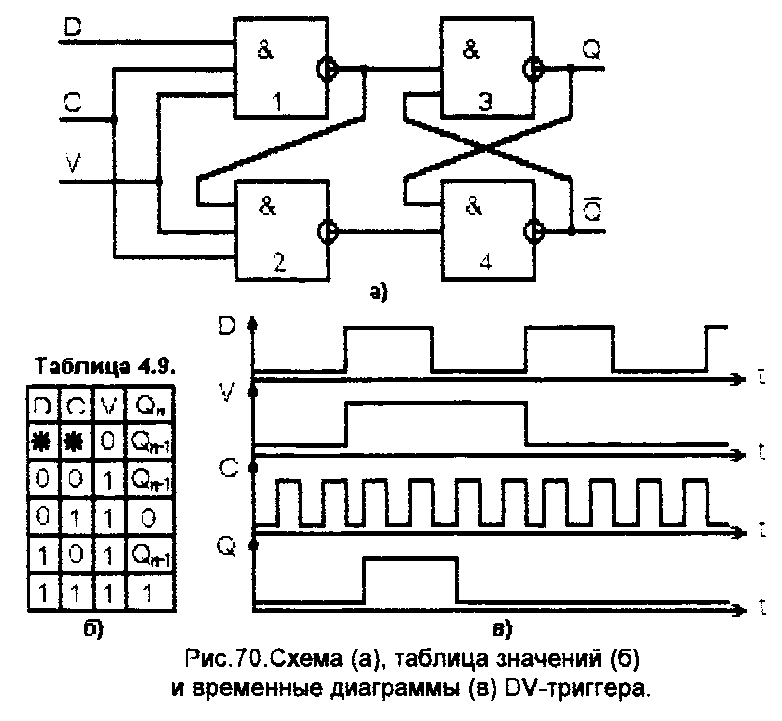

DV -триггер.

DV-триггер - тактируемый D-триггер, у которого имеется дополнительный вход управления V.

Одноступенчатый синхронный DV-триггер может быть образован из D-триггера, в который введён вход управления V параллельно синхронизирующему входу С.

|

|

Рис.70.Схема(а),таблица значений(б) и временные диаграммы(в) DV-триггера.

DV-триггер будет переключатся в состояние, соответствующее уровню на входе D, при наличии сигналов V=1 и С=1. При V=G информация со входа D не принимается в DV- триггер, т.к. уровень логической 1 с выходов элементов И-НЕ1 и И-НЕ2 блокирует состояние RS-триггера, построенного на элементах И-НЕЗ, И-НЕ4.

Наличие двух управляющих входов С и V в DV-триггере даёт возможность один вход С использовать для задания временных интервалов, в которые допускается приём информации в триггер, а другой V - для подачи сигналов, разрешающих приём в триггер сигнала со входа D. При С=1 не допускается изменение уровней на входах D и V. DV-триггер - универсальный триггер. При входном сигнале V=1 он работает в режиме D- триггера. Если выход <2п-инверсное соединить со входом D, то при подаче на вход V счётных сигналов схема будет работать в режиме синхронного Т-триггера. Если выход Qn- инверсное соединить со входом D, то при подаче уровня логической 1 на вход V и счётных сигналов на вход С схема будет работать в режиме асинхронного Т-триггера.

Схемы включения DV-триггера в режимы асинхронного и синхронного Т-триггеров и одноступенчатого D-триггера имеют вид:

|

|

JK-триггер.

Распространённым типом триггера в системах интегральных логических элементов является универсальный двухтактный JK-триггер. Триггеры этого типа отличаются от RS- триггеров тем, что при значениях входной информации, запрещённых для RS-триггеров, они инвертируют хранимую в них информацию.

JK-триггер может быть построен на основе двухтактного синхронного RS-триггера.

Рис.71.Схема(а),таблица значений(б) и временные диаграммы(в) JK-триггера.

Входы J и К триггера (рис. 71) соответствуют входам S и R в RS-триггере, т.е. сигналы J=1, К=0 устанавливают триггер в состояние 1, а сигналы J=Q, К=1 - в состояние О независимо от предыдущего состояния. Такие переключения возможны при сигнале на синхронизирующем входе С=1.

Однако в отличие от RS-триггера в JK-триггере сигналы логической 1 могут одновременно прийти на входы J и К. При J=1, К=1 и С=1 JK-триггер изменяет своё состояние на противоположное. Следовательно, при подаче на вход С серии синхронизирующих сигналов и J=K=1 JK-триггер работает в счётном режиме, т е. как Т- триггер.

|

|

У рассмотренного триггера имеются входы несинхронизируемой установки S̅ и R̅, с помощью которых при С=0 триггер может быть установлен в состояние 1 путём подами сигналов R̅=1 и S̅=0, либо в состояние 0 при подаче R̅=0 и S̅=1.

|

|

Рис.72.Условное обозначение JK-триггера

На базе синхронного JK-триггера можно реализовать синхронный и асинхронный Т- триггеры, D-триггер,

синхронный RS-триггер.

Триггеры с динамическим управлением.

При построении функциональных узлов вычислительных машин широко используются триггеры с динамическим синхронизирующим входом. Особенность таких триггеров состоит в том, что уровни с информационных входов воспринимаются триггером лишь в течение времени, когда на входе синхронизации С происходит переход с уровня логического 0 на 1, либо с логической 1 на 0.

|

|

Динамический RS-триггер

Рис.73.Схема(а) и временные диаграммы(б) динамического RS-триггера.

Пусть триггер хранит логическую 1 (Qn=1). Наличие на синхронизирующем входе триггера уровня С=0 независимо от комбинации входных сигналов на информационных входах будет блокировать состояние триггера, т.к. уровни логической 1 на выходах элементов И-НЕЗ и И-НЕ4 не смогут изменить состояние триггера Т5.

Если перед подачей уровня логической 1 на вход С на информационных входах действовали уровни сигналов, например, Я-инверсное=0 и 8-инверсное=1, то при смене уровня на входе С с 0 на 1 на выходе элемента И-НЕ4 установится уровень логического 0, устанавливающий триггер Т5 в состояние 0 (Q=0). Одновременно уровень логического 0 с выхода элемента И-НЕ4 подаётся на выход элемента И-НЕ2 и на его выходе устанавливается уровень логической 1 независимо от последующих значений уровня сигнала на инверсном входе R.

Уровень логического 0 с выхода элемента И-НЕЗ Аналогично упередаётся на вход И- НЕ1. устанавливая на его выходе уровень логической 1 независимо от последующих значений сигнала на инверсном входе S. Таким образом происходит логическое отключение триггера Т5 от входов. Изменение на входе С логического уровня с 1 на 0 заблокирует состояние триггера Т5. т.е. он будет хранить логический 0.

Если на инверсных информационных входах будут действовать уровни сигнала S=0, R=1, то при смене уровня на входе С с логического 0 на 1 произойдёт переключение триггера Т5 из состояния 0 в состояние 1 (Qn=1). После этого никакие последующие изменения уровней сигнала на входах не будут восприниматься триггером T5, пока на входе С не произойдёт перепад уровней сигнала с логического 0 на 1.

|

|

Рис.74.Условное графическое обозначение динамического RS-триггера.

Динамически D-триггер.

Рис.75.Схема динамического D-триггера.

В триггерах с динамическим управлением по входу синхронизации, или просто динамических триггерах, запись входной информации происходит в момент перепада тактового сигнала. Запись может производится в момент положительного перепада тактового импульса (по фронту синхроимпульса) или в момент отрицательного перепада (по срезу синхроимпульса), Наиболее распространённым таким динамическим триггером является D-триггер, приведённый на рис.75.

триггеров Т1 и Т2 и выходного триггера ТЗ.

Рассмотрим основные режимы и особенности работы динамического О-тригтера;

1. Режим хранения. Если С=0, то х2=S̅=1 и x3=R̅=1.

Это нейтральная комбинация входных сигналов для выходного триггера ТЗ. При такой комбинации сигналов он находится в режиме хранения и выходные сигналы О-триггера не меняются.

2. Запись информации. До тех пор, пока С=0, один из двух триггеров Т1, Т2 находится в неопределённом состоянии.

X3=1 x2=1

X4=D̅ x1=x̅4̅=D

Какой из вспомогательных триггеров находится в устойчивом состоянии, а какой в неопределённом, зависит от уровня сигнала на входе D. Когда С=1, триггер, находившийся в устойчивом состоянии, сохраняет значение сигналов на своих выходах неизменным. Неопределённое состояние другого вспомогательного триггера при этом исчезает. В какое из двух устойчивых состояний он перейдёт, определяется значениями выходных сигналов триггера, находившегося в логически допустимом состоянии; из чего следует:

При D=0 x2=S̅ - остаётся в 1

X3=R̅ - переходит в 0

При D=1 x3=R̅ - остаётся в 1

X2=S̅ - переходит в 0

Сигнал принимающий нулевое значение, определяет состояние выходного триггера ТЗ. Таким образом, выходной сигнал О-триггера Q принимает значение входных данных.

3. Блокировка. Когда оба вспомогательных триггера Т1 и Т2 находятся в логически допустимых состояниях, они блокируют друг друга. При х3=0 заблокирован элемент 4. а при х2 =0 заблокированы элементы 1 и 3.

4. Подготовка к записи. Когда С=0 при установятся единичные уровни на выходах х2 и хЗ. и взаимная блокировка вспомогательных триггеров Т1 и Т2 снимается. Один из них перейдёт в неопределённое состояние, другой останется в устойчивом. Когда закончатся переходные процессы во вспомогательных триггерах Т1 и Т2, схема будет готова к записи информации в выходной триггер ТЗ.

Условное обозначение О-триггеров с динамическим управлением имеет вид (рис.76).

|

|

Рис.76.УГО динамических D-триггеров.

Регистры.

При выполнении различных арифметических и логических операций возникает необходимость хранения кода числа в течение некоторого времени, а так же сдвинуть этот код вправо или влево. Такие операции выполняют специальные устройства, называемые регистрами.

Регистр - функциональное устройство, предназначенное для приёма и хранения информации в виде машинных слов или его частей, а также для выполнения над словами некоторых логических преобразований. Регистр представляет собой совокупность триггеров и схемы управления входными и выходными сигналами. Разрядность регистра соответствует количеству используемых в них триггеров.

Регистры классифицируются:

1. По виду выполняемых операций над словами различают регистры для приёма, передачи и сдвига информации.

2. По способу приёма и передачи информации различают параллельные, последовательные и параллельно-последовательные регистры.

3. По количеству каналов, по которым поступает информация на входы регистра, регистры бывают одно и парафазными.

4. По количеству тактов управления, необходимых для записи кода слова, различают одно, двух, и многотактные регистры.

Параллельные регистры.

Регистры приёма и передачи информации применяются для ввода, хранения и вывода двоичной информации в параллельном коде. Они могут быть построены из асинхронных и синхронных одноступенчатых и двухступенчатых триггеров.

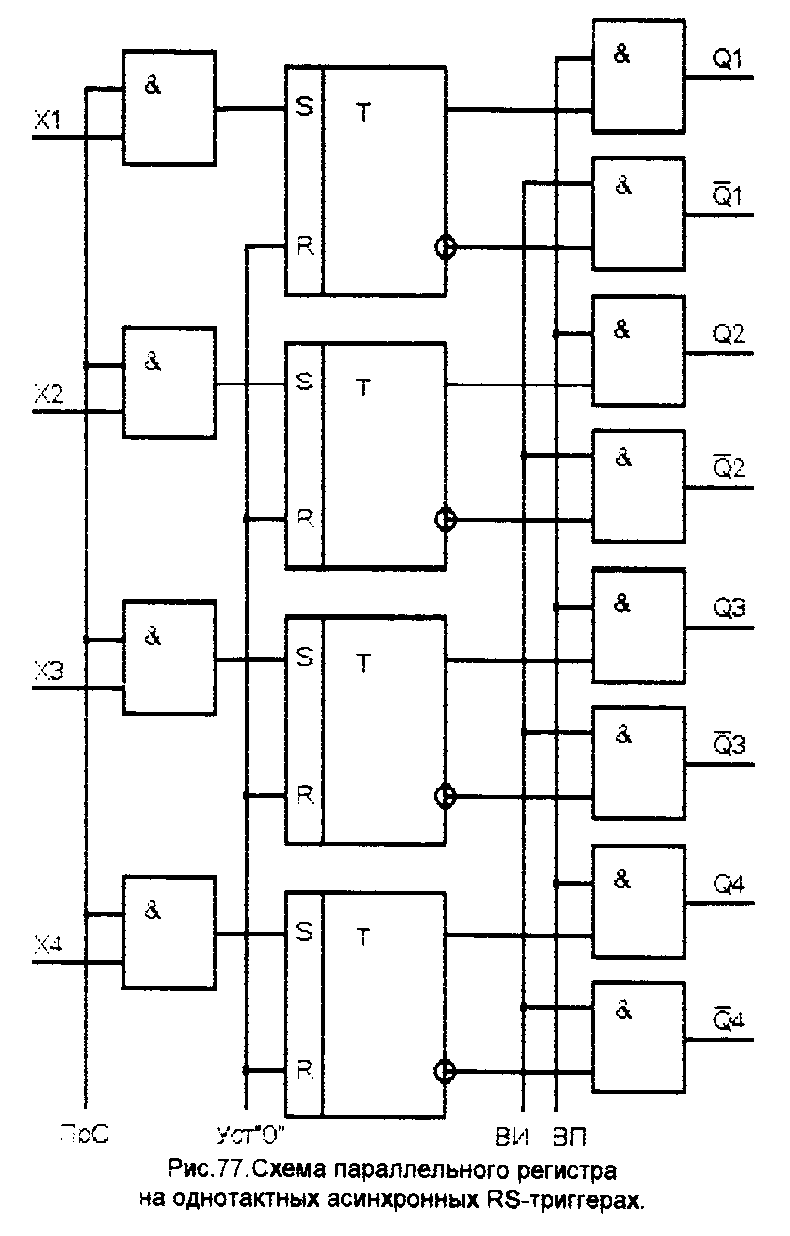

В схеме на рис.77 используются RS-триггеры, группа входных элементов И и группа выходных элементов И. Информация в регистр заносится по кодовой шине слова в прямом коде. Кодовые шины слова (КШС) с помощью элементов И подключены к входам S триггеров регистра. Приём двоичного слова Х1Х2ХЗХ4 с КШС в регистр осуществляется а два такта. По первому такту сигналом Уст"0" регистр устанавливается в нулевое состояние. Под установкой триггеров в нулевое состояние может приниматься термин ’’очищение регистра". После "очищения регистра" в него может быть занесено любое число, согласно числу разрядов регистра. По второму такту сигналом приём слова (ПрС) в регистр записывается параллельный код двоичного слова Х1Х2ХЗХ4. При этом в соответствии с кодом двоичного слова каждый из триггеров ТГТ4 регистра будет либо переключатся в состояние 1 либо оставаться в состоянии 0.

Записанный в регистр код двоичного слова будет хранится в нём до тех пор, пока не будет подан сигнал установки регистра в состояние 0.

Для выдачи прямого кода двоичного слова необходимо подать управляющий сигнал "выдача прямого кода" на шину ВП. При этом код слова с прямых выходов триггеров регистра пройдёт через группу схем И,и в каждом разряде на выходе будет выработан сигнал Qj=Xj.

Для выдачи обратного кода двоичного слова необходимо подать управляющий сигнал ’выдача обратного кода” на шину ВИ. При этом код слова с инверсных выходов триггеров пройдёт через группу схем И, и в каждом разряде на выходе будет выработан сигнал Q1=X1.

Установка триггеров параллельного регистра в состояние 0, прежде чем записать в них новую информацию, ведёт к затратам времени, т.е. снижается быстродействие. Для увеличения быстродействия параллельного регистра используются парафазные схемы.

Рис.77.Схема параллельного регистра на однотактных асинхронных RS-триггерах

При наличии на входах регистра парафазного кода на одном из входов триггера обязательно будет присутствовать сигнал логической 1. который по сигналу ПрС установит триггер в требуемое состояние, независимо от той информации, которая хранилась в нём до этого.

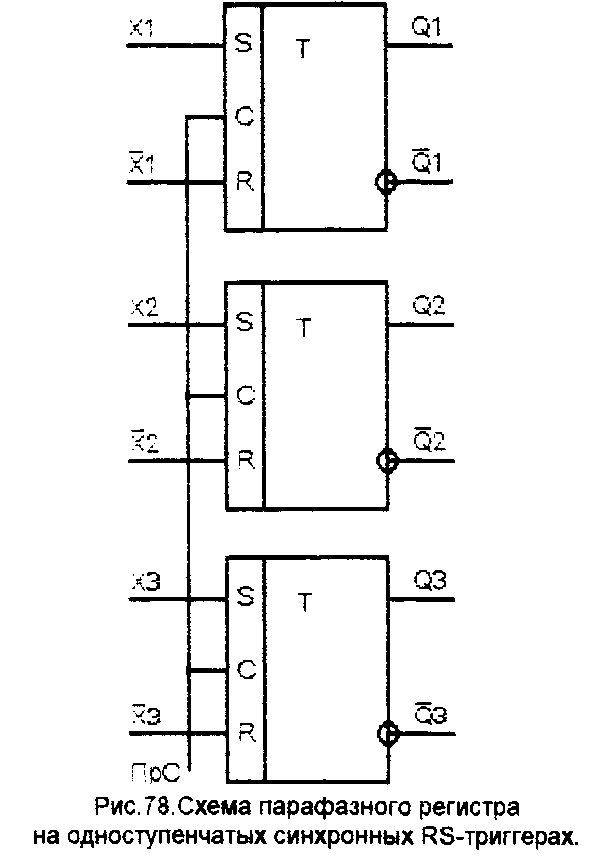

Рис.78.Схема парафазного регистра на одноступенчатых синхронных RS-триггерах.

Рис.79.Условное графическое обозначение параллельных регистров.

Сдвигающие регистры.

Сдвигающие регистры - регистры, выполняющие сдвиг двоичной информации вправо или влево по регистру. Необходимость в выполнении операций сдвига возникает при умножении, делении и преобразовании параллельного двоичного кода в последовательное сочетание двоичных знаков.

Сдвигающие регистры, в которые ввод и вывод двоичного слова производится в последовательном коде, называют последовательными регистрами.

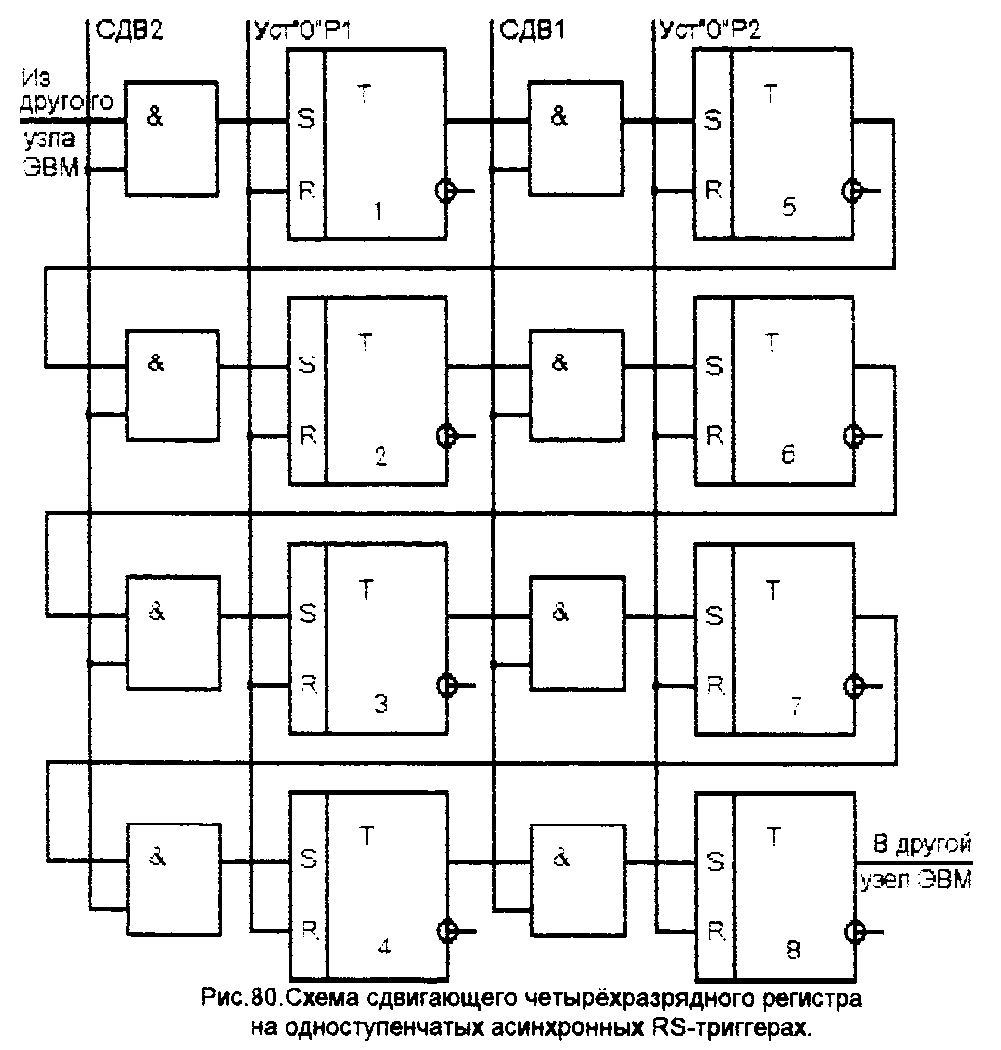

Рис.80.Схема сдвигающего четырехразрядного регистра на одноступенчатых асинхронных RS-триггерах.

Он состоит из двух частей: рабочего регистра Р1 на триггерах Т1-Т4 и вспомогательного регистра Р2 на триггерах

Т5-Т8, а также схем совпадения.

Рассмотрим работу сдвигающего регистра для сдвига прямого числа, находящегося в регистре Р1 на один разряд вправо. Эта операция может быть проведена путём выдачи двоичного числа в регистр Р2 и затем выдачи этого же числа из регистра Р2 в регистр Р1.

Операция сдвига двоичного числа производится в следующей последовательности:

1. Производится установка регистра Р2 в нулевое состояние.

2. Подаётся сигнал на шину СДВ1, т.е. на один из входов схем совпадения. При этом на другие входы схем совпадения сигнал подаётся с триггеров Т1-Т4, т.е. с регистра Р1, Таким образом двоичное число переписывается из регистра Р1 в регистр Р2.

3. Производится установка регистра Р1 в нулевое состояние.

4.

Подаётся серия импульсов на шину СДВ2, т.е. на вторые входы схем совпадения. На первые входы схем совпадения сигнал будет поступать с регистра Р2, т.е. с триггеров Т5- Т8. В результате чего, находившееся ранее в регистре Р1 двоичное число, будет сдвинуто на один разряд вправо, т.е. в регистре Р1 будет уже хранится новое число.

Сдвигающий регистр можно построить и на D-триггерах. В этом случае отпадает необходимость в дополнительном регистре.

Соединение D-триггеров (рис.81а) обеспечивает сдвиг в регистре информации вправо, если управление сдвигом осуществляется синхронизирующими сигналами. Установка регистра в состояние "0000" производится управляющим сигналом Уст"0". Информационный вход D используется для подачи двоичного слова последовательно разряд за разрядом.

Запись в регистр последовательного двоичного кода, например ХзХ2Х1Х0=1101. производится через информационный вход D-следующим образом.

1. Установка регистра в состояние "0000" управляющим сигналом Уст"0".

2.

При D=X3=1 первый сигнал сдвига СдвПр установит триггер ТО в состояние 1. остальные триггеры Т1, Т2 и ТЗ не изменят своего состояния, т.е. в регистре установится двоичные код 0001.

3. При D=X2=1 второй сигнал сдвига СдвПр установит ТО в состояние 1. его информационное состояние Х3=1 будет передано в Т1. а Т2 и ТЗ не изменят своего состояния, т.е. в регистре установится двоичный код 0011.

4. При D=Xi=Q третий сигнал сдвига СдвПр установит триггер ТО в состояние 0. его информационное состояние Х2=1 будет передано триггеру Т1, а с триггера Т1 информационное состояние Х3=1 перейдёт в Т2; ТЗ не изменит своего состояния, т.е. в регистре установится двоичный код 0110.

5. При D=Xq=1 четвёртый сигнал сдвига СдвПр изменит состояние триггера ТО, информационное состояние ТО передаётся Т1 и т.д., т.е. в регистре установится код двоичного числа 1101.

Последовательный двоичный код из регистра будет выдаваться сигналами СдвПр в виде высокого и низкого уровней на выходе регистра.

Как видно из работы регистра, при считывании информация в регистре теряется. Если замкнуть выход триггера ТЗ с входом D триггера ТО, то при считывании организуется цепь связи младшего разряда регистра со старшим и тогда одновременно будет происходить его перезапись. Такие регистры принято называть кольцевыми регистрами.

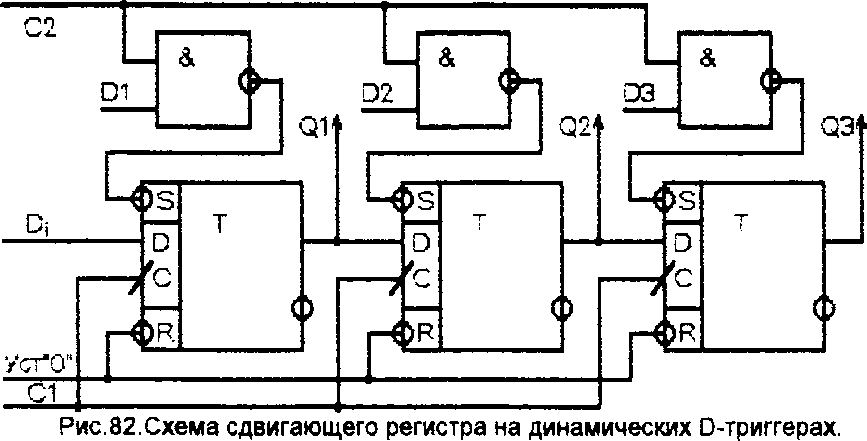

Сдвигающий регистр можно использовать не только для сдвига кода, но и для преобразования параллельного кода, принятого в регистр, в последовательный. Для этого достаточно принятый код сдвигать до тех пор, пока он весь не будет выдвинут из регистра. Выход из крайнего разряда используется в качестве выходной шины последовательного кода. Сдвигающий регистр может выполнять функцию также преобразования последовательного кода в параллельный. Такие регистры целесообразно строить на D-триггерах (рис.82).

Рис.82.Схема сдвигающего регистра на динамических D-триггерах.

Установка регистра в состояние 0 выполняется по инверсному входу R (Уст"0"). Параллельный код поступает на входы D1-D3. Запись параллельного кода в регистр осуществляется положительным импульсом, подаваемым на вход С2. Сдвиг информации по регистру осуществляется подачей сигнала С1. Запись последовательного кода осуществляется по входу Di.

|

|

Рис.83.УГО сдвигающих регистров

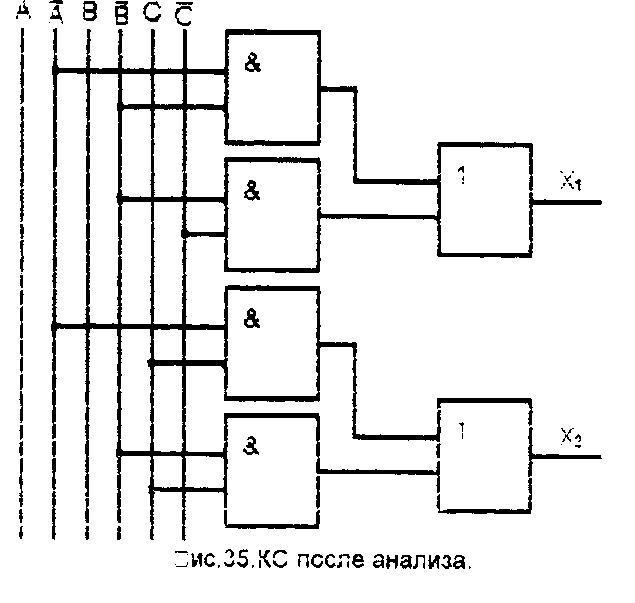

Реверсивные регистры.

В вычислительной технике при построении сложных электронных схем используют реверсивные регистры. Такой тип регистров позволяет сдвигать информацию как вправо, так и влево по регистру (см.рис.84).

|

|

Рис.84.Схема реверсивного сдвигающего регистра на D-триггерах

Сдвиг двоичного кода в регистре вправо или влево задаётся разрешающим уровнем логической 1 или на входе Е2 (сдвиг вправо), или на входе Е1 (сдвиг влево) и производится под воздействием сигнала сдвига (СДВ), подаваемого на вход синхронизации всех D-триггеров регистра. Под воздействием каждого сдвигающего импульса происходит сдвиг на один разряд вправо или влево.

|

|

Рис.85.УГО реверсивных сдвигающих регистров.

Пояснения к УГО реверсивного регистра (см.рис.85):

4.3. Счётчики.

Счётчик представляет собой устройство, предназначенное для подсчёта числа сигналов, поступающих на его вход, и фиксации этого числа в виде кода, хранящегося в триггерах. Количество разрядов счётчика определяется наибольшим числом, которое должно быть получено в каждом конкретном случае. Максимальное число N, которое может быть записано в счётчике, равно:

N=2n-1,

где n - число разрядов счётчика.

Счётчики широко применяются в вычислительной технике и различных устройствах автоматики для формирования адресов, команд, счёта количества циклов выполнения операций, формирования кода в преобразователях и т.д.

По целевому назначению счётчики подразделяют на простые и реверсивные. Простые счётчики могут быть суммирующие и вычитающие. Суммирующий счётчик предназначен для выполнения счёта в прямом направлении, т.е. для сложения. С подачей на вход очередного единичного сигнала показания счётчика увеличиваются на единицу. Вычитающий счётчик предназначен для выполнения счёта единичных сигналов в режиме вычитания. Каждый сигнал, поступающий на вход такого счётчика, уменьшает его показания на единицу. Реверсивные счётчики предназначены для работы в режиме сложения и в режиме вычитания.

По способу организации счёта счётчики подразделяют на асинхронные и синхронные. В асинхронных счётчиках сигнал от разряда к разряду передаётся естественным путём в различные интервалы времени в зависимости от сочетания входных сигналов. В синхронных счётчиках сигналы от разряда к разряду передаются принудительным путём с помощью тактовых сигналов.

По способу организации цепей переноса между разрядами различают счётчики с последовательным, параллельным и частично-параллельным переносом.

Основными характеристиками счётчика являются коэффициент пересчёта (модуль счёта), разрешающая способность, время регистрации и ёмкость. Коэффициент пересчёта характеризует число устойчивых состояний счётчика, т.е. предельное число входных сигналов, которое может сосчитать счётчик. Разрешающая способность - минимально допустимый период следования входных сигналов, при котором обеспечивается надёжная работа счётчика. Время регистрации - интервал времени между моментами поступления счётного сигнала и окончания самого длинного переходного процесса в счётчике. Ёмкость счётчика - максимальное число единичных сигналов, которое может быть зафиксировано на счётчике.

Двоичный счётчик с последовательным переносом.

В этих счётчиках каждый последующий триггер запускается от информационных выходов предыдущего триггера. Наиболее простой схемой двоичного счётчика с последовательным переносом является схема счётчика на Т-триггерах. На рис.86 приведён суммирующий счётчик с последовательным переносом.

|

| ||

|

|

|

|

|

Дата добавления: 2018-10-18; Мы поможем в написании ваших работ!; просмотров: 2436 | Нарушение авторских прав

Лучшие изречения: