данных

АЛУ данных (рис. 6.4) разработано для улучшения возможности обработки сигналов широкого динамического диапазона. Специальные схемы обеспечивают простой контроль ошибок округления и переполнения обрабатываемых данных. АЛУ содержит четыре 24-битных входных регистра, два 48-битных аккумулятора, два 8-битных регистра расширения аккумулятора, аккумулятор сдвига, две шины данных и параллельное неконвейеризованное устройство умножения с аккумулированием (MAC). Операции АЛУ используют арифметику дополнения до двух. В регистры АЛУ могут быть записаны 24- или 48-разрядные операнды. АЛУ позволяет выполнять в одном командном цикле инструкции умножения, сложения, вычитания, итерационного деления, нормализации, сдвигов, логических операций. Регистры АЛУ данных могут бы прочитаны или записаны 24-битными или 48-битными операндами по шинам XDB, YD Операнды источника могут иметь длину 24,48 и 56 бит и всегда находятся в регистрах AJ данных. Результат любой операции в АЛУ данных сохраняется в аккумуляторе.

24-битные данные обеспечивают динамический диапазон в 144 дБ. Такого диапазона достаточно для большинства приложений, в которых используются параметры разрядностью не больше 24 бит. 56-битный аккумулятор АЛУ данных обеспечивает 336 дБ внутреннего динамического диапазона.

За один цикл в АЛУ выполняются следующие операции: умножение, округление, сложение, вычитание, деление, нормализация, сдвиги и логические операции.

АЛУ данных имеет следующие компоненты:

• четыре 24-битных входных регистра;

• параллельный умножитель - аккумулятор (MAC);

• два 48-битных регистра аккумулятора;

• два 8-битных регистра расширения аккумулятора;

• аккумулятор сдвига;

• два устройства сдвига/ограничения по шине данных.

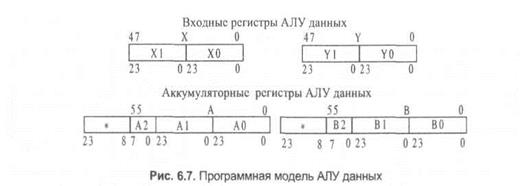

Входные регистры АЛУ данных (Х1, ХО, Y1, Y0). Это 24-битные регистры данных общего назначения. Они могут использоваться как независимые 24-битные регистры м как два 48-битных регистра X и Y, образованные объединением Х1:Х0 и Y1:Y0 соответственно. Х1 - старшее слово X, Y1 - старшее слово Y. Регистры служат входными буферами между XDB или YDB и устройством MAC. Они используются как операнды источника АЛУ данных. Содержимое регистров может быть выдано на соответствующую шину данных для процедур обработки прерываний.

Аккумуляторы АЛУ данных. Шесть регистров АЛУ данных (А2, А1, А0, В2, В1 и В формируют два 56-битных аккумулятора общего назначения. Каждый из аккумулятор! содержит по три объединенных регистра (А2:А1:А0 и В2:В1:В0). 24-битная MSP хранит! в А1 или В1, 24-битная LSP - в А0 или В0. 8-битное расширение - в А2 или В2.

8-битные регистры расширения предназначены для защиты от переполнения.

В DSP56000/DSP56001 диапазон значений операндов составляет от -1 до +0,9999998. Если сумма двух чисел меньше -1 или больше +0,9999998, то возникает потеря значимости или переполнение. 8-битный регистр расширения формирует результат в случае 255 переполнений или 255 потерь значимости.

При использовании регистра расширения аккумулятора бит переполнения в peгистре кодов условий всегда установлен в единицу.

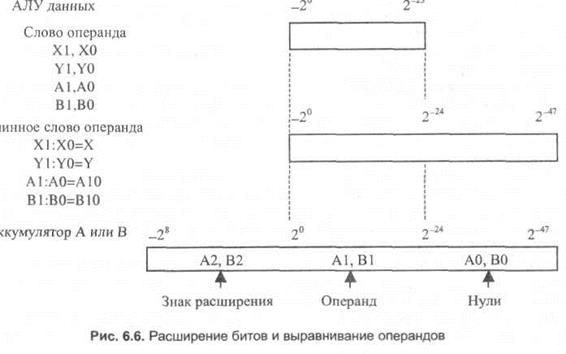

Расширение знака обеспечивается автоматически при записи в 56-битный аккумулятор А или В 48-битного или 24-битного операнда. Если записывается 24-битный операнд, LSP автоматически заполняется нулями для представления операнда в 56-битной форме.

Если аккумуляторы А и В прочитаны, можно с помощью опций масштабировать их содержимое на один бит влево или вправо для блока арифметики с плавающей точкой.

MAC и логическое устройство. MAC и логическое устройство входят в главное арифметическое устройство DSP и выполняют все вычисления с операндами данных. В случае арифметической инструкции устройство обрабатывает до трех операндов и выдает 56-битный результат в следующем формате: расширение: старшая значащая часть: младшая значащая часть (EXT: MSP:LSP).

Операция MAC выполняется независимо и параллельно с операциями на шинах данных, что облегчает буферизацию входных и выходных данных АЛУ.

Арифметическое устройство содержит умножитель и два аккумулятора. На вход умножителя могут поступать данные только из регистров X и Y. Умножитель выполняет умножение 24 х 24 с дополнением до двух. 48-битный результат выравнивается и суммируется с 56-битным содержимым аккумулятора А или В. 56-битная сумма сохраняется в аккумуляторе (рис. 6.5). 8-битное расширение аккумулятора фиксирует переполнение до 256 и позволяет складывать или вычитать содержимое 56-битных аккумуляторов. Операция MAC (умножение/ сложение) - неконвейеризованная одноцикловая операция. Если инструкция предусматривает умножение без сложения, то устройство MAC очищает аккуму-

|

лятор и складывает его содержимое с произведением. Таким образом, результат всех арифметических инструкций представляется в формате EXT:MSP:LSP (А2:А1:А0 или В2:В1:В0). Если результат сохраняется в 24-битном операнде, LSP просто отсекается или округляется до MSP.

Округление до ближайшего целого применяется при сложении произведения с содержимым аккумулятора в специальной команде DSP - MACR. Бит, до которого идет округление в аккумуляторе, определяется битом режима масштабирования в регистре статуса.

Логическое устройство выполняет логические операции AND, OR, EOR, NOT над регистрами АЛУ. Это устройство имеет разрядность 24 бита и оперирует старшей значащей частью операнда в аккумуляторе.

Устройство сдвига аккумулятора. Асинхронное параллельное устройство сдвига с 56-битным входом и 56-битным выходом подключено непосредственно к выходам MAC. Выполняет операции: нет сдвига; сдвиг на один бит влево: ASL, LSL, ROL; сдвиг на один бит вправо: ASR, ASL, ROR; обнуление.

Устройство сдвига/ограничения. Обеспечивает специальную обработку данных при выдаче из регистров аккумулятора на шины данных. Для каждой шины данных имеется отдельное устройство сдвига/ограничения.

Ограничение (насыщенная арифметика). Аккумулятор АЛУ данных в DSP56000/ DSP56001 имеет 8 бит расширения. При выдаче данных из регистров аккумулятора А или В на шины данных необходимо производить ограничение битов расширения.

Устройство ограничения нормализует результат вычислений без изменения содержимого регистров аккумулятора А и В.

Если содержимое аккумулятора источника может быть представлено без переполнения, то устройство ограничения отключено, и операнд не модифицируется.

В противном случае устройство ограничения заменяет данные максимальной величиной и устанавливает знак данных соответственно операнду источника: $7FFFFF - для 24-битного или $7FFFFF FFFFFF - для 48-битного положительного числа, $800000 - для 24-битного, $800000 000000 -для 48-битного отрицательного числа. Этот процесс называется насыщенной арифметикой (табл. 6.1).

Представление данных и округление. DSP56000/DSP56001 используют дробное представление данных для всех операций АЛУ. На рис. 6.6 показан механизм этого предтавления. Десятичная точка всегда расположена слева.

MAC использует округление содержимого аккумулятора с одинарной точностью. Данный метод округления называется округлением до ближайшего целого или конвергентным округлением.

Ограничения данных Таблица 6.1.

| Приемник | Операнд источника | Знак аккумулятора | Ограничивающее значение | Тип доступа | |

| XDB | YDB | ||||

| X | Х:А Х:В | + - | 7FFFFF 800000 | - - | Один 24-битный |

| Y | Y:A Y:B | + - | - - | 7FFFFF 800000 | Один 24-битный |

| Х и Y | Х:А Y:A X:AY:B Х:В Y:A Х:В Y:B L:AB L:BA | + - + - + - | 7FFFFF 800000 7FFFFF 800000 7FFFFF 800000 | 7FFFFF 800000 7FFFFF 800000 7FFFFF 800000 | Два 24-битных |

| L(X:Y) | L:A L:B | + - | 7FFFFF 800000 | 7FFFFF 800000 | Один 48-битный |

Программная модель АЛУ данных. Программная модель АЛУ данных приведена на рис. 6.7 («*» - читаются как нули и не записываются).

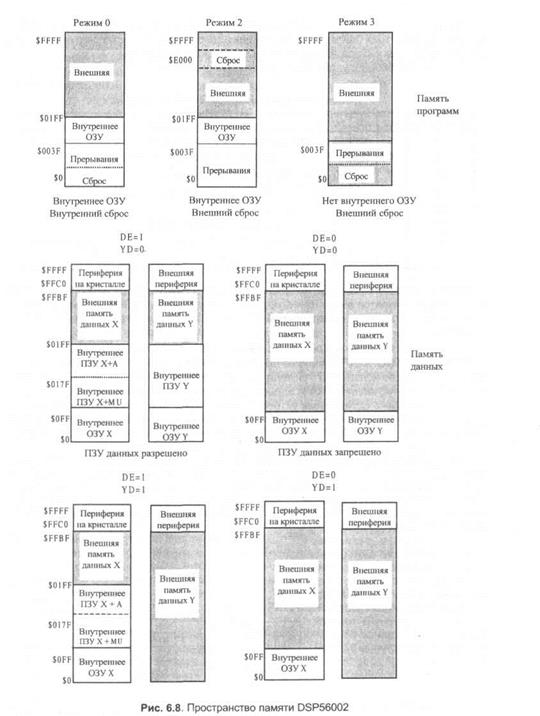

Пространство памяти DSP56002. Пространство памяти DSP56002 представлено на рис. 6.8.

Регистр OMR расширен битами YD (3 бит), МС (4 бит) SD (6 бит). Биты DE и YD задают режимы памяти (табл. 6.2).

|

Однокристальный режим. В однокристальном режиме разрешены все внутренние памяти данных и программ. Программный сброс вызывает переход по адресу $0000 и выполнение соответствующей процедуры.

Карты памяти для режима 0 и режима 2 идентичны, но в режиме 2 вектор сброса находится по адресу $Е000.

Режим загрузки из EEPROM. Загрузочные режимы предназначены для загрузки программ из байтового ПЗУ во внутреннюю память программ в течение сброса по питанию. После включения питания генератор состояний ожидания добавляет 15 состояний ожидания ко всем обращениям к внешней памяти, что позволяет использовать медленную память.

Программа загрузки использует байты в трех последовательно расположенных ячейках внешнего ПЗУ для образования слова внутренней памяти программ. В загрузочном режиме разрешены загрузочное ПЗУ на кристалле и выполнение программы загрузки.

Нормальный расширенный режим. В этом режиме разрешено внутреннее ОЗУ программ и вектор аппаратного сброса по адресу $Е000.

Режим разработки. В этом режиме внутреннее ОЗУ программ запрещено, а вектор аппаратного сброса находится по адресу $0000. Все ссылки на пространство памяти программ переадресуются прямо во внешнюю память.

Режим загрузки по Host. В этом режиме разрешены загрузочное ПЗУ и выполнение программы загрузки. Режим аналогичен режиму 1, за исключением того, что программа загружается из внешней памяти программ по host-интерфейсу.

Режим загрузки по SCI. В этом режиме разрешены загрузочное ПЗУ и выполнение программы загрузки. Внутреннее и/или внешнее ОЗУ программ загружается по интерфейсу SCI. Количество слов программы и стартовый адрес должны быть определены.

Программа загрузки по SCI ожидает приема трех байтов, определяющих количество слов программы, трех байтов, определяющих адрес, с которого будут загружаться слова программы, и трех байтов для загрузки каждого слова программы.

Режимы DSP56002 и управляющие сигналы приведены в табл. 6.3.

Данные принимаются в SCI, начиная с младших битов. После окончания приема слов программы начинается выполнение загруженной программы. SCI запрограммирован на работу в асинхронном режиме с длиной данных - 8 бит, 1 стоп-бит, проверка на четность отсутствует.

|

Устройство генерации адресов (AGU) и режимы адресации

Структура AGU. AGU выполняет вычисление эффективных адресов данных в памяти. Это устройство использует три типа адресной арифметики: линейную модификацию адреса, модульную модификацию адреса, адресацию с реверсивным переносом и работает параллельно с остальными устройствами на кристалле, что сокращает время на генерацию адресов. Структура AGU показана на рис. 6.9. Все регистры AGU являются 24-разрядными, в которых 16 младших разрядов являются значащими. Старшие 8 разрядов недоступны для записи и при чтении заполняются нулями.

|

Блок регистров адреса (R0-R3 И R4-R7). Каждый из двух подблоков регистров адреса содержит четыре 16-битных регистра, которые содержат адреса для обращения к памяти. Каждый регистр может быть прочитан или записан с использованием глобальной шины данных. При выдаче содержимого регистров на шину данных 16-битные регистры записываются в два младших значащих байта шины данных, а старший значащий байт заполняется нулями.

При записи в регистры старший значащий байт шины данных отсекается. Каждый адресный регистр может использоваться как вход АЛУ адресов для модификации регистров. Регистр из АЛУ нижних адресов и регистр из АЛУ верхних адресов доступны в одной инструкции.

Рис. 6.9. Структура AGU

Если параллельно осуществляется пересылка данных из памяти X и из памяти Y, адресные регистры разделяются на два блока: R0 - R3, R4 - R7. Содержимое регистров адреса может модифицироваться соответственно режиму адресации. Тип модификации определяется содержимым регистров модификации (Мn). Регистры смещения (Nn) используются для режима адресации «модификация со смещением».

Большинство режимов адресации модифицируют регистры адреса в цикле «чтение -модификация - запись».

Блок регистров смещения (N0-N3 И N4-N7). Каждый из двух подблоков регистров смещения содержит четыре 16-битных регистра, которые содержат величину смещения, используемую для модификации адресных указателей или данных. Каждый регистр может быть прочитан или записан с использованием глобальной шины данных. При выдаче содержимого регистров на шину данных 16-битные регистры записываются в два младших значащих байта шины данных, а старший значащий байт заполняется нулями. При записи в регистры старший значащий байт шины данных отсекается.

Блок регистров модификации (МО-МЗ И М4-М7). Каждый из двух подблоков регистров модификации содержит четыре 16-битных регистра, которые определяют тип адресной арифметики для вычисления модификаций регистров адреса или данных. Каждый регистр может быть прочитан или записан с использованием глобальной шины данных. При выдаче содержимого регистров на шину данных 16-битные регистры записываются в два младших значащих байта шины данных, а старший значащий байт заполняется нулями. При записи в регистры старший значащий байт шины данных отсекается. Каждый регистр модификации устанавливается в $FFFF после сброса, что определяет линейную арифметику при вычислении модификаций адреса.

АЛУ адресов. Два идентичных АЛУ адресов содержат 16-битный полный адрес, который может быть инкрементирован, декрементирован или к которому может быть добавлено содержимое регистра смещения. Второе полное слагаемое (называемое модулем) определяется результатом суммирования первого полного слагаемого с величиной модуля, хранящейся в регистре модификации. Третье полное слагаемое определяется инкрементированием, декрементированием содержимого адресного регистра или его суммированием с величиной смещения и переносом. Смещение и реверсивный перенос подаются параллельно на разные входы. Тестовая логика определяет, какой из трех результатов подается на выход в качестве полного адреса.

Каждое АЛУ адресов может модифицировать один регистр адреса в течение одного командного цикла. Содержимое регистра модификации определяет тип арифметики для модификации адреса. Величина модификатора декодируется в АЛУ адресов.

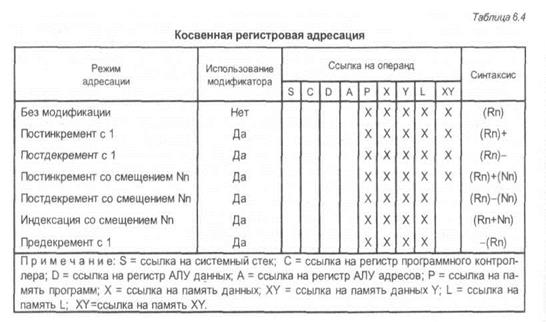

Адресация. DSP56000/DSP56001 обеспечивают три различных типа адресации: прямая регистровая, косвенная регистровая и специальная (табл. 6.4). При прямой регистровой адресации и специальных режимах использование AGU не является обязательным (эти режимы описаны в Приложении).

Косвенная регистровая адресация. Если регистр адреса используется для указания ячейки памяти, адресация называется косвенной регистровой, т.е. содержимое регистра указывает не на сам операнд, а на адрес операнда.

Поле «перемещение по шине данных» в инструкции указывает пространство памяти, на которое идет ссылка. Содержимое регистров AGU определяет эффективный адрес и его модификацию.

Без модификации. Адрес операнда содержится в регистре адреса Rn. Содержимое регистра не изменяется при выполнении инструкции.

Постинкремент. Адрес операнда содержится в регистре адреса Rn. После использования содержимое регистра инкрементируется. Этот режим адресации используется для работы с памятью X, Y и для модификации содержимого регистра адреса без пересылки соответствующих данных.

Постдекремент. Адрес операнда содержится в регистре адреса Rn. После использования содержимое регистра декрементируется. Этот режим адресации используется для работы с памятью X, Y и для модификации содержимого регистра адреса без пересылки соответствующих данных.

Постинкремент со смещением Nn. Адрес операнда содержится в регистре адреса Rn. После использования содержимое регистра суммируется с содержимым регистра смещения Nn и сохраняется в регистре адреса. Содержимое регистра смещения не изменяется. Этот режим адресации используется для работы с памятью X, Y и для модификации содержимого регистра адреса без пересылки соответствующих данных.

Постдекремент со смещением Nn. Адрес операнда содержится в регистре адреса Rn. После использования из содержимого регистра адреса вычитается содержимое регистра смещения Nn и результат сохраняется в регистре адреса. Содержимое регистра смещения не изменяется. Этот режим адресации используется для работы с памятью X, Y и для модификации содержимого регистра адреса без пересылки соответствующих данных.

Индексный со смещением Nn. Адрес операнда - сумма содержимого регистра адреса Rn и содержимого регистра смещения Nn. Содержимое регистра адреса и регистра смещения не изменяется. Этот режим адресации не может использоваться для работы с памятью X, Y.

Предекремент. Адрес операнда - содержимое регистра адреса Rn, декрементированное на единицу перед выборкой операнда. Содержимое регистра адреса декрементируется и сохраняется. Этот режим адресации используется для работы с памятью X, Y, но не может использоваться для модификации содержимого регистра адреса без пересылки соответствующих данных.

|

Типы модификации адреса. АЛУ адресов поддерживает линейную, модульную арифметику и арифметику с реверсивным переносом для всех режимов косвенной адресно-регистровой адресации. Эти типы арифметики упрощают создание структур данных в памяти для очередей, линии задержки, циклических буферов, стеков. Содержимое регистров модификации определяет тип арифметики для вычисления адреса; для модульной арифметики содержимое регистра модификации также определяет модуль. Каждому регистру адреса соответствует свой регистр модификации.

Линейный модификатор (Мп = $FFFF). Используется нормальная 16-битная линейная арифметика (табл. 6.5). При вычислении адреса используется 16-битное смещение Nп, инкремент и декремент. Диапазон величин Nn для чисел со знаком - от -32,768 до +32,767, для беззнаковых чисел - от 0 до +65,535.

Модульный модификатор (Мп = Модуль - 1). Модификация адреса использует модуль М значением от +2 до +32,767 (см. табл. 6.5).

Содержимое регистра адреса ограничивается адресным интервалом размера М, определяющего верхнюю и нижнюю границы адресов. Величина m = М - 1 сохраняется в регистре модификации (рис. 6.10). Нижняя граница (базовый адрес) должна содержать нули в К младших значащих битах, где 2К > М и, следовательно, должна быть умножена на 2К. Верхняя граница = нижняя граница плюс модуль минус 1.

Начиная с М < 2к при однажды выбранном М создается последовательная серия блоков памяти (каждый длиной 2К), в которой размещается циклический буфер. Если М < 2К, то расстояние между двумя последовательными циклическими буферами должно быть

(2к) - М. Например, для создания циклического буфера с 21 уровнями (М - 21) нижняя адресная граница должна иметь пять младших битов, равных 0 (2К > 21, поэтому К > 5).

В регистр Мп загружается значение 20. Нижняя граница может выбираться из величин 0, 1 64, 96,128,160 и т. д. Верхняя граница буфера равна нижней границе плюс 21. Таким образом, остается 11 неиспользованных ячеек памяти между верхним адресом и следуем нижним адресом.

|

Для указателя адреса не требуется установка на начало нижней границы или на конец верхней границы адреса - он может быть инициализирован по любому адресу, входящему в диапазон, определяемый модулем. Также не нужно запоминать верхнюю или нижнюю границу адресов - сохраняется только область модуля в Мп (границы определяются

содержимым Rn). Использование косвенного режима адресации (Rn)+ при инкременте адресного регистpa после верхней границы буфера вызывает возврат обратно через базовый адрес (нижняя граница). Аналогично, использование косвенного режима адресации (Rn)- при декременте адресного регистра после нижней границы буфера вызывает возврат через базовый адрес + М - 1.

|

|

В случае использования смещения Nn при вычислении адреса 16-битное абсолютное значение |Nn| должно быть равно или меньше М. Если Nn > М, результат зависим отданных и непредсказуем, за исключением специального случая: Nn = Р х 2К, где Р - положительное целое число. Для этого случая, когда используется режим адресации (Rn) + Nn, указатель Rn будет перемещаться линейно, к тому же самому относительному адресу в новом буфере, который находится на Р блоков памяти впереди (рис. 6.11). Аналогично для (Rn) - Nn указатель будет перемещаться на Р блоков памяти назад. Эта техника используется при последовательной обработке нескольких таблиц или N-размерных массивов. Диапазон значений Nn: от -32768 до +32767. Устройство модульной арифметики автоматически перемещает указатель адреса на требуемую позицию. Этот тип модификации адреса используется для создания циклических буферов FIFO, линий задержки и простых буферов длиной до 32786 слов. Специальный случай (Rn) ± Nn по модулю

М с Nn = Р х 2К используется для обработки одинаковых алгоритмов в памяти, т. е. для параллельных вычислений КИХ-фильтров. Пример модульной адресации показан на рис. 6.12. Начиная с позиции 64, создается циклический буфер с 21 уровнями. Нижняя граница = L х (2К), где 2К> 21, таким образом, К = 5 и нижняя граница адресов должна быть умножена на 32. Нижняя граница выбирается из значений 0, 32, 64,96,128, 160 и т. д. В данном примере L = 2 и нижняя граница адресов равна 64.

|

Верхняя граница буфера равна 84 (нижняя граница + 20 (М - 1)). Регистр смещения выбирается равным 15 (Nn < М). Указатель адреса не нужно устанавливать на начало нижней границы адресов. В данном примере указатель устанавливается на позицию 75. Если R2 постинкрементируется со смещением при выполнении инструкции MOVE, указатель, который установился бы на позицию 90 для линейной адресации, вернется на позицию 69. Если указатель инкрементируется после верхней границы буфера [базовый адрес плюс (М - 1)], он возвращается на базовый адрес. Если указатель адреса декрементируется после нижней границы буфера, он возвращается на базовый адрес плюс (М - 1). Если Rn находится вне корректного диапазона буфера и выполняется операция, требующая модификации Rn, содержимое Rn модифицируется в соответствии с правилами модульной арифметики. Например, инструкция MOVE B0,

X:(R0) + N0 (где R0 = 6, МО = 5, N0 = 0) не требует явной модификации регистра. Однако, если R0 выше верхней границы, вычисляется новое содержимое

R0 = R0 + N0 - МО -1 и R0 устанавливается в «0».

Модификатор реверсивного переноса. Реверсивный перенос выбирается, если регистр модификации установлен в «0». Модификация адреса осуществляется аппаратно -переносом в обратном направлении: из старших битов в младшие биты. Реверсивный перенос эквивалентен реверсии битов содержимого Rn и величины смещения Nn, сложению и реверсии битов результата. Если используется режим адресации +Nn и содержимое Nn равно 2(К-1), этот адресный модификатор эквивалентен реверсии К младших битов Rn (LSB), инкременту Rn и еще одной реверсии К младших битов Rn. Диапазон возможных значений Nn составляет от 0 до +32, что позволяет адресовать 65536 точек для ДПФ. Для корректного применения бит-реверсивной адресации для 2К точек ДПФ, необходимо использовать приведенную ниже процедуру:

1) установить Мп в 0;

2) установить Nn равным 2(к-1);

3) установить Rn между нижней и верхней границами буфера памяти. Нижняя граница равна L х 2К, где L - целое число; эта граница дает 16-битный двоичный номер

«хх...хх00...00», где хх...хх = L и 00...00 - эквивалент К нулей; верхняя граница равна L x 2к+

+(2К- 1); эта граница дает 16-битный двоичный номер «хх...хх11...11», где хх...хх = L и

11...11 - эквивалент К единиц;

4) использовать режим адресации (Rn) + Nn.

В качестве примера рассмотрим 1024-точечный ДПФ с вещественными данными, хранящимися в X памяти и мнимыми данными, хранящимися в Y памяти (1024 = 210; К = 10). Регистр модификации Мп установлен в «0». Регистр смещения Nn содержит величину 512 (2К 1). Регистр Rn содержит 3072 (L х 2К = 3 х 210). Верхняя граница равна 4095 (нижняя граница + (2К - 1) = 3072 + 1023).

Постинкремент со смещением N генерирует последовательность адресов (0,512,256, 768,128,640,...), которая добавляется к нижней границе. Эта последовательность представляет собой порядок поступления точек частоты в интервале от 0 до 2л (входных отсчетов для БПФ с прореживанием по времени). В табл. 6.6 приведено содержимое Rn при использовании модификации (Rn) + Nn.

|

Модификатор реверсивного переноса работает только в том случае, если базовый адрес буфера данных умножается на 2К, т. е. принимает такие значения, как 1024, 2048, 3072 и т. д. Можно использовать другие режимы адресации, но они могут привести к неудовлетворительному результату.

В данном примере L = 3, К = 10. Первый используемый адрес - нижняя граница (3072), вычисление следующего показано на рис. 6.13.

Заключение. Бит-реверсивная адресация используется для 2к-точечного ДПФ. Модульная адресация используется для создания циклических буферов очередей, линий задержки и простых буферов до 32768 слов длиной. Линейная адресация используется для общих случаев.

Рис. 6.13. Вычисления при бит-реверсивной адресации

На рис. 6.14 приведены примеры использования трех модификаторов адреса, использующих для упрощения анализа 8-битные регистры. В примере используется режим адресации «постинкремент со смещением». Линейный модификатор адреса адресует каждую пятую позицию, поскольку регистр смещения содержит $5.

Использование бит-реверсивной адресации в режиме «постинкремент со смещением» Nn вызывает реверсию четырех младших битов, инкремент и еще одну реверсию четырех битов. Модульный модификатор адреса имеет заданную нижнюю границу, верхняя граница определяется суммой модуля и нижней границы. Эти границы создают циклический буфер таким образом, что если содержимое адресного регистра выходит за границы буфера, происходит циклический возврат в пределы буфера.

Программный контроллер

|

Программный контроллер обеспечивает предварительную выборку инструкций, декодирование инструкций, управление аппаратными циклами и обработку исключений. Контроллер содержит 15-уровневый 32-разрядный системный стек и шесть непосредственно адресуемых регистров (рис. 6.15): программный счетчик PC (Program Counter), регистр адреса цикла LA (Loop Address), счетчик петли LC(Loop Counter), регистр статуса SR (Status Registr), регистр режима операций OMR (Operating Mode Register) и указатель стека SP (Stack Pointer). Регистры контроллера приведены на рис. 6.15. Системный стек представляет собой отдельный блок внутренней памяти, используемый для хранения регистра статуса и программного счетчика при вызовах подпрограмм и длительных прерываниях. В стеке также хранятся LA и LC для организации программных циклов. Каждая ячейка стека включает два 16-разрядных регистра: старшую часть (SSH) и младшую часть (SSL) стека.

Все эти регистры могут быть прочитаны или записаны для упрощения отладки системы. Хотя ни один из регистров программного контроллера не является 24-битным, все они читаются и записываются через 24-битную шину PDB. При чтении регистров младшая часть битов (LSB) является значащей, а старшая значащая часть битов (MSB) заполняется нулями. При записи регистров младшая часть битов (LSB) является значащей, а старшая значащая часть битов просто отбрасывается, поскольку имеет смысл только младшая значащая часть битов (биты 15-0). Программный контроллер содержит конвейер с тремя ступенями и управляется пятью состояниями процессора: нормальным, обработкой исключений, сбросом, ожиданием и остановом.

Структура программного контроллера. Программный контроллер состоит из трех аппаратных блоков: контроллера декодирования программ (PDC), генератора адресов программ (PAG) и контроллера прерываний (PIC).

Контроллер декодирования программ. PDC включает в себя программную логику для декодирования, генератор адреса регистра, механизм выполнения циклов, механизм выполнения повторений, генератор кодов условий, механизм выполнения прерываний, регистр-защелку инструкций и его копию. PDC декодирует 24-битную инструкцию, загруженную в регистр-защелку, и вырабатывает все сигналы, необходимые для управления конвейером. Копия регистра-защелки инструкций оптимизирует выполнение инструкций повторения и перехода.

Генератор адресов программ. PAG содержит: PC, SP, SS (системный стек), OMR (регистр операционного режима), SR, LC и LA. Циклы, являющиеся основной конструкцией алгоритмов цифровой обработки сигналов, поддерживаются аппаратно.

При выполнении инструкции DO в регистр счетчика цикла загружается количество повторений цикла, а в регистр адреса цикла - адрес последней инструкции цикла, и устанавливается флаг цикла в регистре статуса. Перед выполнением инструкции DO содержимое регистров LA, LC и SR сохраняется в стеке. Под управлением механизма выполнения циклов адрес первой инструкции цикла помещается в стек. Пока флаг цикла в регистре статуса не сброшен, механизм выполнения циклов сравнивает содержимое PC с содержимым LA для определения последней инструкции цикла. Когда последняя инструкция выбрана, содержимое LC сравнивается с единицей. Если равенство не выполняется, содержимое LC декрементируется и из SS читается адрес первой инструкции цикла. Если равенство выполняется, то значения LA, LC и флага цикла в SR восстанавливаются из стека, а выборка инструкций продолжается с адреса LA + 1.

Пересылка массива данных может быть выполнена с использованием механизма повторений. Инструкция REP загружает в LC количество повторений следующей за ней инструкции. Так как команда, которая будет повторяться, выбрана только один раз, это увеличивает производительность за счет уменьшения обращений к внешней шине. Однако инструкция REP не может быть прервана, поскольку выбирается только один раз.

Контроллер прерываний. PIC принимает все запросы прерываний, осуществляет арбитраж в каждом цикле и генерирует адрес вектора прерывания. Прерывания могут вызывать четыре внешних и 16 внутренних источников прерываний.

Используется структура гибкого приоритета прерываний. Каждое прерывание получает свой уровень приоритета (IPL) - от 0 до 3. Уровень 0 - самый низкий, а уровни 1 и 2 маскируются. Уровень 3 является высшим и не маскируется. Биты маски прерываний в регистре статуса (SR) показывают текущий уровень приоритета прерываний в процессоре. Прерывания, имеющие уровень приоритета меньше текущего, не учитываются при арбитраже. Уровень приоритета 3 всегда вызывает прерывание процессора. Уровни приоритета прерываний для каждого периферийного устройства на кристалле (HI, SSI, SCI) и для каждого внешнего источника прерываний (ΙRQA,ΙRQB) могут задаваться программным путем от 0 до 2. Уровни приоритета устанавливаются при записи в регистр уровней приоритета, представленный на рис. 6.16.

В DSP56002 регистр уровней приоритета прерываний расширен: добавлены биты 16-TIL1 и 17 -TIL0, которые задают уровень приоритета прерываний от таймера. Источники прерываний и их уровни приоритета указаны в табл. 6.7. Каждый источник прерываний имеет свой вектор для вызова процедуры обработки прерывания, расположенной в младших 64 словах памяти программ. При переходе к обработке исключений текущая инструкция выполняется, если только выбранное слово не является первым словом двухсловной инструкции, иначе выполнение инструкции прерывается.

Далее выполняется две выборки адреса, во время которых PC не изменяется. PIC генерирует выборку адреса инструкции прерывания, указывающего на первое слово двухсловной инструкции подпрограммы быстрой обработки прерывания. Затем производится выборка двух слов инструкции по вектору прерывания.

Если одно из этих слов - переход к подпрограмме, то быстрая обработка прерывания переводится в длительную. Процедура длительной обработки прерывания помещает текущий контекст процессора в стек. Подпрограммы и прерывания могут быть вложенными. Стек может быть расширен в память за счет использования программного доступа к регистрам SSH и SSL. Контакты внешних прерываний lRQA и lRQB могут быть настроены на прерывания по переднему или заднему фронту. Немаскируемое прерывание NMI осуществляется по уровню и выполняется по первому появлению на контакте -.IRQB 10В после последнего обслуживания NMI или сброса. NMI имеет уровень приоритета 3 и не маскируется. NMI не используется как вход прерывания общего назначения, поскольку зарезервировано для аппаратных разработок.

Вектор аппаратного сброса может указывать на внутреннюю или внешнюю (Р:$Е000) память программ. Немаскируемое прерывание, трассировка и программное прерывание используются при отладке.

Программное прерывание используется для организации точек останова. При трассировке инструкции выполняются в пошаговом режиме.

Все периферийные устройства на кристалле используют одинаковый механизм запроса прерываний. Каждое устройство имеет одну линию запроса прерывания в PIC и две входные линии: линию чтения вектора и линию ответа.

Устройство, имеющее более одного источника прерывания, проводит собственный арбитраж прерывания в соответствии с его внутренним уровнем приоритета. PIC выбирает одно из периферийных устройств и посылает ему адрес вектора прерывания.

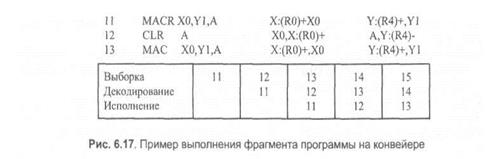

Конвейер инструкций. Программный контроллер содержит трехуровневый конвейн ер, выполняющий выборку, декодирование и исполнение инструкций. Устройства выборки, декодирования и исполнения расположены последовательно. Пример работы конвейера приведен на рис. 6.17.

Синхронизация. DSP56000/DSP56001 использует четырехфазную синхронизацию вьг полнения инструкций. Синхронизация обеспечивается внутренним генератором, соед»»-ненным с внешним кристаллом контактами XTAL и EXTAL, или внешним генератором по линии EXTAL

Программная модель. Программная модель контроллера представлена на рис. 6.18. Она содержит наряду с программным счетчиком, регистром статуса и системным стеком дополнительные регистры счетчика цикла и адреса цикла, предназначенные для аппаратной поддержки инструкции DO.

|

Программный счетчик (PC). 16-битный регистр, содержащий адрес следующей ячейки в памяти программ. PC может указывать на инструкции, операнды данных или адреса операндов. Ссылки на этот регистр подразумеваются в большинстве инструкций. PC запоминается в стеке при выполнении программного цикла, подпрограммы или прерывания.

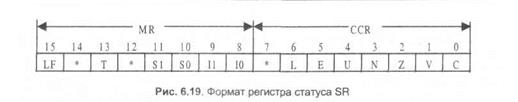

Регистр статуса (SR). 16-битный регистр статуса SR состоит из регистра режима MR, занимающего 8 старших битов и регистра кодов условий CCR, занимающего 8 младших битов. Регистр статуса сохраняется в стеке при выполнении программного цикла, подпрограммы или прерывания. Формат регистра показан на рис. 6.19.

Регистр управления (MR). MR - специальный управляющий регистр, определяющий текущее состояние процессора для супервизора. На биты регистра режима MR воздействуют сброс процессора, выполнение цикла, возврат из прерывания, программное прерывание и инструкции, оперирующие непосредственно с содержимым регистра. После аппаратного сброса в регистре устанавливается маска прерывания, биты масштабирования, флаг цикла, бит трассировки сбрасываются в «О».

Регистр кодов условий (CCR). Регистр кодов условий определяет текущее состояние процессора для пользователя. На регистр кодов условий воздействуют арифметические и логические операции, операции пересылки и инструкции, оперирующие непосредственно с содержимым регистра. После сброса все биты CCR устанавливаются в «О».

Перенос (С- бит 0).

Флаг переноса устанавливается в «1» при наличии переноса из старшей значащей части числа в результате сложения. Перенос или заем генерируется из бита 55 результата. Перенос также возникает при манипуляциях с битами, сдвигах и циклических сдвигах.

Переполнение (V- бит 1).

Флаг переполнения устанавливается при арифметическом переполнении 56-битного результата. Это означает, что результат не может быть представлен в аккумуляторе.

Нуль (Z- бит 2).

Бит устанавливается в «1», если результат равен нулю.

Минус (N - бит 3).

Бит устанавливается в «1», если результат имеет отрицательный знак.

Денормализация (U — бит 4).

Бит устанавливается, если два старших бита идентичны. Механизм вычисления денормализации представлен в табл. 6.8.

Расширение (Е - бит 5).

Бит расширения сброшен в «О», если все биты целой части 56-битного результата -нули или единицы, иначе бит установлен. Целая часть определяется режимом масштабирования и битом Е (табл. 6.9). Если бит расширения равен нулю, то младшая часть числа содержит все значащие биты, а старшая часть числа является расширением знака. В этом случае регистр расширения аккумулятора игнорируется. Если бит расширения равен единице, то регистр расширения аккумулятора используется.

Ограничение (L — бит 6).

Бит установлен, если установлен бит переполнения. Также устанавливается при выполнении операций ограничения устройством сдвига/ограничения данных. Бит сбрасывается только при сбросе процессора или специальной командой.

Маска прерывания (11,10 - биты 8 и 9).

Показывает текущий уровень приоритета прерываний в процессоре. Уровень приоритета изменяется программным путем. Биты маски прерываний устанавливаются в «1» при аппаратном сбросе процессора и не изменяются при программном сбросе.

Режим масштабирования (S1.S0 - биты 10 и 11).

Биты определяют режим масштабирования для устройства сдвига/ограничения данных АЛУ и позиции округления для MAC (табл. 6.10). Действие режима масштабирования проявляется при чтении данных из аккумуляторных регистров А и В на шины данных и при округлении в MAC. При сбросе процессора и начале длительной обработки прерывания эти биты равны нулю.

Режим трассировки (Т— бит 13).

Бит устанавливается в начале выполнения каждой инструкции в пошаговом режиме. Если бит равен нулю, трассировка запрещена и выполнение инструкций идет нормальным образом. При сбросе процессора бит равен нулю.

Флаг цикла (LF- бит 15).

Бит устанавливается при выполнении программного цикла и разрешает определение окончания цикла. По завершении цикла бит устанавливается в «0».

Регистр операционного режима (OMR). OMR -24-битный регистр (рис. 6.20), в котором определены 5 битов для DSP56000/DSP56001 и 7 битов для DSP56002. Устанавливает текущий операционный режим процессора (табл. 6.11, 6.12, 6.13).

На биты регистра воздействует только сброс процессора и непосредственные операции с содержимым регистра. После сброса биты МА и MB могут быть загружены извне через контакты А и В.

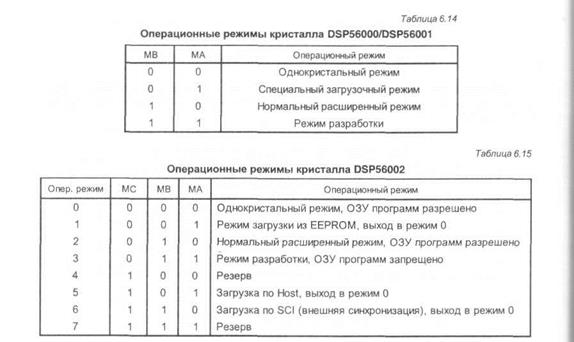

Операционный режим кристалла (МА,МВ - биты 0 и 1). Показывают режим расширения шин в процессоре (табл. 6.14). После сброса эти значения загружаются извне через внешние контакты выбора операционного режима MODA и MODB, либо могут быть изменены программным путем. Операционные режимы кристалла DSP56002 представлены в табл. 6.15.

Разрешение ПЗУ данных (DE- бит 2).

Установка бита разрешает использование двух ПЗУ данных размером 256 х 24, находящихся по адресам $0100 -$01FF в пространствах памяти X и Y.

Запрещение внутренней памяти Y (YD - бит 3).

Установка бита запрещает доступ к внутренней памяти данных Y. Если бит равен нулю, внутренняя память данных Y доступна в соответствии с состоянием управляющего бита DE. Аппаратный сброс очищает бит YD.

Операционный режим кристалла (МС - бит 4).

Бит МС наряду с битами МА и MB определяет карту памяти и операционный режим кристалла. После сброса процессор загружает этот бит через внешний контакт MODC. После выхода процессора из состояния сброса бит МС может быть изменен программным путем.

Задержка останова (SD — бит 6).

При выходе из состояния останова (по инструкции STOP) если этот бит равен нулю, генерируется задержка в 64К циклов синхронизации (131072 Т состояний). Если бит установлен в «1», задержка составляет 16 Т состояний. Длительная задержка используется для стабилизации синхронизации.

Доступ к внешней памяти (ЕА - бит 7).

Бит определяет функции двух линий порта А, указанные в табл. 6.16.

|