Опыт построения МП-систем позволяет выделить типовые задачи, которые должен уметь решать МК для эффективного управления в реальном времени:

• отсчет равных интервалов времени заданной длительности, повтор алгоритма управления по истечении каждого такого временного интервала; обычно эту функцию называют формированием меток реального времени.

• контроль за изменением состояния линии ввода МК;

• измерение длительности сигнала заданного логического уровня на линии ввода МК;

• подсчет числа импульсов внешнего сигнала на заданном временном интервале;

• формирование на линии вывода МК сигнала заданного логического уровня с программируемой задержкой по отношению к изменению сигнала на линии ввода;

• формирование на линии вывода МК импульсного сигнала с программируемой часто

той и программируемым коэффициентом заполнения.

Каждая из перечисленных задач в отдельности может быть выполнена только программными средствами, без использования специальных аппаратных решений. Так, для формирования интервала времени следует загрузить в регистр центрального процессора число, а затем выполнять команду декрементирования этого регистра до тех пор, пока содержимое регистра не станет равным нулю. Похожие решения можно предложить и для остальных перечисленных задач. Однако все эти решения будут обладать общим недостатком: невозможностью выполнения вычислений одновременно с отсчетом временного интервала. Поэтому для выполнения функций, связанных с управлением в реальном времени, в состав МК включают специальные аппаратные средства, которые называют таймером.

В процессе развития модули таймеров в составе 8-разрядных МК непрерывно совершенствовались. Рассмотрим принцип действия одного из первых модулей, который входит в состав МК 8051 АН фирмы «Intel».

Таймер представляет собой 16-разрядный счетчик со схемой управления (рис. 4.7).

8 карте памяти МК счетчик отображается двумя регистрами: ТН — старший байт счетчика, TL - младший байт. Регистры доступны для чтения и для записи. Направление счета счетчика - только прямое, т. е. при поступлении тактовых импульсов десятичный эквивалент двоичного кода счетчика изменяется в сторону увеличения. В зависимости от программных настроек счетчик может использовать один из двух источников тактирования:

1) импульсную последовательность с выхода управляемого делителя частоты fBIJS;

2) внешнюю импульсную последовательность, поступающую на один из входов МК.

В первом случае говорят, что счетчик работает в режиме таймера, во втором — в режиме счетчика событий. При переполнении счетчика устанавливается триггер переполнения TF, который генерирует запрос на прерывание, если прерывания от таймера разрешены. После переполнения работа счетчика продолжается. Последовательность изменения кодов следующая: $FF, $00, $01 и т. д. Пуск и останов счетчика могут выполняться только под управлением программы посредством установки/сброса соответствующего бита. Программа также может установить старший ТН и младший TL байты счетчика в произвольное состояние или прочитать текущий код счетчика. Однако эти операции не следует выполнять в процессе счета, так как длительность операции чтения или записи может превысить длительность периода частоты тактирования счетчика. Тогда за время чтения одного из байтов второй успеет измениться. В результате будет прочитана недостоверная информация. По этой же причине может оказаться ошибочной операция записи. Например, пользователь записывает в регистры счетчика код $0005: сначала старший байт $00, а затем младший - $05. Если текущее состояние счетчика пользо-

вателю неизвестно, то может оказаться, что на момент завершения операции записи старшего байта младший равен $FF.

Тогда в процессе записи младшего байта старший, ранее записанный, успеет измениться, и конечный код счетчика будет равен $0105.

Если рассмотренный таймер используется для измерения временного интервала 1ИЗМ (рис. 4.8), то необходимо выполнить следующую последовательность действий:

1)прервать выполнение текущей программы при изменении сигнала на линии РТх1

с «О» на «1»; в подпрограмме прерывания установить регистры счетчика таймера в $0000

и разрешить счет;

2)при изменении сигнала на линии РТх1 с «1» на «О» еще раз прервать выполнение

программы МК; в подпрограмме прерывания остановить счет; код в регистрах ТН и TL будет равен длительности интервала tw3M, выраженной числом периодов частоты тактирования счетчика таймера.

Однако такой способ измерения годится для сигналов, длительность которых составляет единицы мс и более. Моменты разрешения счета таймера t1 и его остановки 12 не совпадают с моментами изменения сигнала на входе РТх1, так как пуск и останов выполняются в подпрограмме прерывания. Ошибка счета равна t1 -t2. Каждое из значений t1 и t2 определяется временем перехода МК к выполнению подпрограммы прерывания и временем выполнения некоторого количества инструкций, предшествующих команде разрешения или останова счета таймера. Вторая величина является систематической ошибкой и может быть учтена при выполнении дальнейших расчетов, в то время как первая - время перехода на подпрограмму прерывания - величина случайная, которая зависит от особенностей выполнения программного обеспечения МП системы. Так, если рассматриваемых каналов измерения несколько, и изменение сигналов на входах PTxi произошло одновременно, то в первом из обслуженных по прерыванию каналов ошибка будет минимальной, а в последнем - максимальной. Эта максимальная ошибка может составить несколько десятков микросекунд, поэтому рассмотренный метод не может быть использован для изменения временных интервалов микросекундного диапазона. В противном случае точность измерения будет недостаточной. Наряду с задачей измерения временного интервала может возникнуть необходимость одновременного формирования времяимпульсных сигналов по нескольким каналам. Тогда желательно, чтобы МК имел в своем составе несколько таймеров. Увеличение числа модулей таймеров, интегрированных на кристалл МК, является объективной тенденцией совершенствования структуры современных МК.

Рассмотренный «классический» модуль таймера наиболее часто используется в МК с архитектурой MSC-51. Однако даже в составе основателя семейства МК 8051 АН он претерпел некоторые усовершенствования:

• дополнительная логика счетного входа позволяет тактовым импульсам поступать на

вход счетчика, если уровень сигнала на одной из линий ввода равен 1; это повышает

точность измерения временного интервала, так как интервалы t, и 12 теперь не являются составляющими погрешности измерения;

• реализован режим перезагрузки счетчика произвольным кодом в момент переполнения; это позволяет формировать метки реального времени с периодом, отличным от

периода полного коэффициента счета, равного 216.

Более подробно режимы работы таймера МК 8051 АН рассмотрены в п. 4.2.6.

Главный недостаток модуля «классического» таймера — невозможность одновременного обслуживания (измерения или формирования импульсного сигнала) сразу в нескольких каналах. Совершенствование структуры подсистемы реального времени 8-разрядных МК ведется по двум направлениям:

1)простое увеличение числа модулей таймеров; этот путь характерен для части МК

компаний «Pfilips» и «Atmel» со структурой MSC-51, для МК компаний «Mitsubishi» и

«Hitachi».

2)модификация структуры модуля таймера, при которой увеличение числа каналов

достигается не увеличением числа счетчиков, а введением дополнительных аппаратных

средств входного захвата и выходного сравнения; Такой путь характерен для 8-разряд

ных МК «Motorola», «Microchip», «Pfilips», «Infineon», более поздних моделей семейства MCS-51 Intel.

Типовая структура усовершенствованного модуля таймера представлена на рис. 4.9 и 4.11. Счетчик таймера дополнен аппаратными средствами входного захвата и выходного сравнения. Эти средства принято называть каналом входного захвата 1C (Input Capture) и выходного сравнения ОС (Output Compare).

Принцип действия канала входного захвата поясняет рис. 4.9. Схема детектора события «наблюдает» за уровнем напряжения на одном их входов МК. Обычно это одна из линий порта ввода/вывода. При изменении уровня логического сигнала на входе детектора с «О» на «1» или наоборот вырабатывается строб записи, и текущее состояние счетчика таймера записывается в 16-разрядный регистр данных TIC канала захвата. Описанное действие в микропроцессорной технике называют событием захвата. Предусмотрены три типа изменения сигнала на входе детектора, которые воспринимаются как событие захвата:

1)изменение логического уровня с 0 на 1 (нарастающий фронт сигнала);

2)изменение логического уровня с 1 на 0 (падающий фронт сигнала);

3)любое изменение логического уровня сигнала.

Выбор типа события захвата устанавливается в процессе инициализации модуля таймера и может многократно изменяться по ходу выполнения программы. Каждое событие захвата отмечается установкой в «1» триггера TFIC. Состояние триггера может быть считано программно, а если прерывания по событию захвата разрешены, то генерируется запрос на прерывание.

Временные диаграммы рис. 4.10 поясняют процесс изменения временного интервала с использованием режима входного захвата. Первоначально детектор события инициализируется на контроль за нарастающим фронтом сигнала на линии РТх1. При изменении уровня сигнала с «О» на «1» код счетчика К, копируется в регистр канала захвата TIC. Триггер TFIC устанавливается в «1», одновременно формируется запрос на прерывание: таймер «сообщает» МК о том, что измеряемый интервал начался. С задержкой времени t по отношению к моменту появления запроса на прерывание МК считывает код К, из регистра TIC, сбрасывает триггер TFIC и инициализирует детектор события на контроль за падающим фронтом сигнала РТх1. При изменении уровня сигнала с «1» на «О» детектор снова фиксирует событие захвата, и код счетчика К2 копируется в регистр TIC. Снова выставляется запрос на прерывание, с задержкой t2 этот код считывается в память МК. Разность кодов К2 - К, и есть длительность измеряемого временного интервала, выраженная в числе периодов частоты тактирования счетчика таймера. Максимальная ошибка измерения равна двум периодам частоты тактирования, так как погрешность детектора событий не может превышать единицы квантования таймера. Время перехода к подпрограммам прерывания t, или 12 не оказывает влияния на точность измерения, так как копирование текущего состояния счетчика осуществляется аппаратными, а не программными cредс-

твами.

Однако время перехода на подпрограмму прерывания (t,) накладывает ограничение на длительность измеряемого интервала тизм, так как обсуждаемый метод реализуем при условии, что второе событие захвата произойдет позже, чем код К, будет считан в память МК.

Структура аппаратных средств канала выходного сравнения представлена на рис. 4.11. Многоразрядный цифровой компаратор непрерывно сравнивает изменяющийся во времени код счетчика таймера с кодом, который записан в 16-разрядном регистре ТОС канала сравнения. В момент равенства кодов на одном из выводов МК (РТх2 на рис. 4.11) устанавливается заданный уровень логического сигнала. Рассмотренное действие называют событием выходного сравнения. Предусмотрены три типа изменения сигнала на выходе РТх2 в момент события выходного сравнения:

1)инвертирование сигнала на выходе;

2)установка низкого логического уровня;

3)установка высокого уровня.

При наступлении события захвата устанавливается в «1» триггер ТРОС. Аналогично предыдущему случаю состояние триггера может быть считано программно, а если прерывания по событию выходного сравнения разрешены, то генерируется запрос на прерывание.

Временные диаграммы рис. 4.12 иллюстрируют способ формирования временного интервала предварительно рассчитанной длительности tx с использованием аппаратных средств канала выходного захвата. Первое событие сравнения в момент t, формирует нарастающий фронт сигнала РТх2. Одновременно генерируется запрос на прерывание МК, и в подпрограмме прерывания происходит загрузка нового кода сравнения К2. Время, необходимое для записи нового значения в регистр канала сравнения ТОС, ограничивает минимальную длительность формируемого временного интервала. В момент t, наступает второе событие сравнения, и выход РТх2 устанавливается в «0». Таким образом, длительность сформированного временного интервала tx определяется только разностью кодов и не зависит от особенностей программного обеспечения МК.

|

В рассмотренных примерах каждому событию модуля таймера (изменению уровня логического сигнала на входе или выходе МК) ставится в соответствие код счетчика, т. е. счетчик используется для создания непрерывно изменяющихся меток текущего времени. В отличие от «классического» таймера, где счетчик используется непосредственно для формирования кода измеряемого временного интервала, в усовершенствованном таймере счетчик лишь создает образ времени, подобно часам. А все действия по формированию или измерению временных интервалов производят аппаратные средства сравнения/захвата. Поэтому счетчик в составе модуля усовершенствованного таймера называют счетчиком временной базы, или просто «временной базой». Эта же терминология сохранится и далее в модулях процессоров событий.

Если говорить о модификациях модуля усовершенствованного таймера в 8-разрядных МК различных фирм, то необходимо отметить следующие особенности.

• Число каналов входного сравнения и выходного захвата (1C и ОС), которые реализованы в модуле усовершенствованного таймера МК, может быть различно. Так, в МК семейства НС05 Motorola типовыми решениями являются модули 2IC+2OC или 11C+1OC, и модуль таймера в составе МК всегда только один. МК семейства НС11 Motorola имеют в своем составе модуль таймера с конфигурацией 4IC+5OC. МК PIC16 Microchip содержат до трех модулей таймеров, но обязательно со структурой 1IC или ЮС (обозначается IC/OC).

• В ряде модулей каналы могут быть произвольно настроены на функцию входного захвата (1C) или выходного сравнения (ОС) посредством инициализации.

• Счетчик модуля усовершенствованного таймера может не иметь функции программного

останова, т. е. он будет считать всегда. Поскольку в этом случае состояние счетчика

нельзя синхронизировать с каким-либо моментом работы МП системы, то такой счетчик

характеризуют как свободно считающий (free counter).

• Часто счетчик таймера не имеет опции тактирования внешним сигналом, т. е. не может

работать в режиме счетчика событий.

.

Аппаратные средства усовершенствованного таймера позволяют решить многие задачи управления в реальном времени. Однако процесс совершенствования алгоритмов управления предъявляет все новые требования к структуре МК. И, как следствие, все более отчетливо проявляются ограничения модулей усовершенствованного таймера:

• недостаточное число каналов сравнения и захвата, принадлежащих одному счетчику временной базы; в результате невозможно сформировать синхронизированные между собой многоканальные импульсные последовательности;

• однозначно определенная конфигурация каналов (или захват или сравнение) часто не удовлетворяет пользователя;

• с использованием средств выходного сравнения возможно формирование сигнала по способу широтно-импульсной модуляции (ШИМ), однако несущая частота ШИМ сигнала тем меньше, чем больше вычислений требуется выполнять при реализации алгоритма управления и чем больше число ШИМ каналов требуется реализовать.

|

|

|

Следующий этап в развитии модулей подсистемы реального времени - модули процессоров событий. Впервые модули процессоров событий были предложены фирмой «Intel» в составе МК 8xC51FA/FB/FC/GB, позже аналогичный модуль появился в МК с ядром MSC-51 фирмы «Pfilips». Модуль, который входит в состав перечисленных МК, носит название программируемого счетного массива РСА (Programmable Counter Array). В МК других фирм аналогичные по функциональному назначению модули обозначают САРСОМ («Infineon»), TIM08 (семейство НС08 Motorola).

Структурная схема процессора событий приведена на рис. 4.13. Модуль процессора событий содержит в себе 16-разрядный счетчик временной базы и некоторое количество универсальных каналов захвата/сравнения. Счетчик может тактироваться импульсной последовательностью с выхода программируемого делителя частоты стробирования межмодульных магистралей feus или внешним генератором. Счетчик имеет опции пуска/ останова и сброса в «О». В некоторых моделях процессора событий счетчик временной базы доступен для чтения «на лету». Режим чтения «на лету» предусматривает автоматическое копирование содержимого старшего и младшего байтов счетчика в специальные буферные регистры в момент выполнения операции чтения указанного в спецификации байта счетчика (старшего или младшего). Тогда при чтении второго байта счетчика возвращается код из соответствующего буферного регистра. Тем самым исключается ошибка считывания по причине изменения состояния счетчика временной базы за время чтения. Наиболее совершенные модели процессора событий 8-разрядных МК допускают изменение коэффициента счета счетчика временной базы или, что то же самое, изменение периода его работы. Для этого в составе модуля имеется двухбайтовый программно доступный регистр периода и многоразрядный цифровой компаратор (не путать с каналом захвата). При совпадении текущего кода счетчика временной базы с кодом периода триггеры счетчика временной базы автоматически сбрасываются в «0».

Универсальные каналы захвата/сравнения в процессоре событий полностью идентичны друг другу и в зависимости от программных настроек могут работать в одном из трех режимов:

1)режим входного захвата;

2)режим выходного сравнения;

3)режим широтно-импульсной модуляции (ШИМ).

Первые два режима по принципу действия ничем не отличаются от аналогичных режимов модуля усовершенствованного таймера. Программно-логическая модель каждого канала включает двухбайтовый регистр данных канала и триггер события. В зависимости от выбранного режима регистр данных канала используется аппаратными средствами для записи кода временной базы в момент наступления входного захвата или для хранения кода выходного сравнения. Триггер устанавливается при наступлении любого из этих событий. При работе канала в режиме выходного сравнения могут возникать нарушения алгоритма работы, приводящие к неправильному формированию сигнала на выходе PTxi модуля. Причиной таких сбоев является изменение под управлением программы величины кода сравнения в процессе работы канала. Наиболее совершенные модели процессора событий предусматривают для таких случаев специальный режим буферированного сравнения, при котором: 16-разрядный регистр кода сравнения дублируется; в каждый момент времени ко входу компаратора оказывается подключенным один из регистров данных, а для записи оказывается доступным другой; в момент наступлении события выходного сравнения регистры автоматически меняются местами. Более подробно режим буферированного выходного сравнения, а также режим буферированной ШИМ рассмотрен в п. 4.3.7.

В режиме широтно-импульсной модуляции (рис. 4.14) на выводе PTxi MK формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса (в некоторых моделях длительность паузы) прямо пропорциональна коду в регистре данных канала. Режим ШИМ чрезвычайно удобен с точки зрения программного обслуживания. Если изменение коэффициента заполнения у не требуется, то достаточно один раз занести код у в регистр данных и проинициализировать режим ШИМ, и импульсная последовательность будет воспроизводиться с требуемыми параметрами без дальнейшего вмешательства со стороны программы.

Режим ШИМ в различных моделях процессоров событий имеет существенные отличия. В модулях программируемого счетного массива РСА код коэффициента заполнения имеет однобайтовый формат, следовательно, дискретность регулирования коэффициента заполнения составляет 1/256 периода ШИМ-сигнала. Причем, 16-разрядный регистр данных универсального канала РСА в режиме ШИМ «распадается» на два однобайтовых регистра. Доступным для записи является только один из регистров. В начале каждого периода ШИМ-сигнала содержимое этого регистра копируется во второй регистр, который используется аппаратными средствами для формирования длительности импульса в текущем периоде. Такое буферирование позволяет избежать нарушений при формировании импульсной последовательности в случаях, когда до наступления момента равенства кодов регистра и счетчика происходит изменение кода коэффициента у, и новое значение у меньше текущего кода счетчика. Тогда сравнение кодов в текущем периоде ШИМ сигнала не наступит, и импульс будет пропущен. Кроме недостатка по низкой дискретности регулирования коэффициента заполнения модуль РСА имеет ограниченный набор несущих частот сигнала ШИМ. Это происходит потому, что коэффициент счетчика временной базы не может быть изменен, а регулирование частоты достигается только изменением коэффициента деления предварительного делителя частоты. Параметры модулей процессоров событий некоторых 8-разрядных МК приведены в табл. 4.2.

В модулях TIM08 МК семейства НС08 фирмы «Motorola» рассмотренные недостатки устранены. Код коэффициента заполнения имеет двухбайтовый формат и, следовательно, дискретность регулирования составляет 1/216 периода ШИМ-сигнала. Одновременно период широтно-модулированной импульсной последовательности может регулироваться в широких пределах, поскольку счетчик временной базы допускает изменение коэффициента счета. Подробно модуль процессора событий TIM08 рассмотрен в п. 4.3.7.

Модули «классических» таймеров и таймеров со схемами захвата/сравнения - достаточно сложные устройства. Их функциональная гибкость в простейших системах управления часто оказывается избыточной. Поэтому в некоторых маловыводных МК, выполненных в корпусах с 16 и 20 выводами, с целью снижения стоимости ИС реализуются упрощенные таймеры. Таймеры содержат постоянно считающий 8-разрядный счетчик с триггером переполнения и программируемый делитель частоты. Такие таймеры могут формировать лишь метки реального времени с периодом следования, который определяется набором коэффициентов деления программируемого делителя частоты. Упрощенные модули таймера имеются в составе МК MC68HC705KJ1 фирмы «Motorola» и Р1С16С5хх фирмы «Microchip». Однако среди последних разработок наблюдается тенденция к функциональному усложнению модуля таймера даже в очень простых МК. Так, модуль процессора событий с небольшим числом каналов имеется в составе всех маловыводных МК семейства НС08 фирмы «Motorola» (серии JUJK, КХ/КТ).

Тенденция увеличения числа таймеров-счетчиков, интегрированных на кристалл МК, нашла свое продолжение и для модулей процессоров событий. Так, во многих современных 8-разрядных МК совершенствование подсистемы реального времени идет не просто по пути увеличения числа каналов процессора событий. Растет число модулей процессоров событий, предоставляя разработчику возможность использования нескольких «временных баз», что позволяет обрабатывать и формировать сигналы разного временного масштаба. Кроме того, в состав МК вводятся упрощенные модули таймеров, способные «разгрузить» процессор событий от выполнения простейших функций.000000

4.1.7. АНАЛОГО-ЦИФРОВЫЕ И ЦИФРОАНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ

Отличительная особенность многих современных 8-разрядных МК— интегрированный на кристалл МК модуль многоканального аналого-цифрового преобразователя (АЦП). Модуль АЦП предназначен для ввода в МК аналоговых сигналов с датчиков физических величин и преобразования этих сигналов в двоичный код с целью последующей программной обработки. Структурная схема типового модуля АЦП представлена на рис. 4.15.

Многоканальный аналоговый коммутатор служит для подключения одного из источников аналоговых сигналов (РТхО - РТх7) ко входу АЦП. Выбор источника сигнала для измерения осуществляется посредством записи номера канала коммутатора в соответствующие разряды регистра управления АЦП. Заметим, что в модулях АЦП 8-разрядных МК предусмотрена только программная установка номера канала, режим автоматического последовательного сканирования каналов с записью результата измерения каждого канала в индивидуальную ячейку памяти не реализуется.

Диапазон измеряемых значений напряжения аналоговых входов определяется напряжением опоры Uоп,. Разрешающая способность АЦП составляет Uоп /2n, где п— число двоичных разрядов в слове результата. Максимальное значение опорного напряжения, как правило, равно напряжению питания МК. Два вывода модуля АЦП используются для задания опорного напряжения: UREFH - верхний предел, Uоп, UREFL - нижний предел. Разность потенциалов на входах U RЕРН и U/REFL и составляет U опЕсли измеряемое напряжение U изм ≥ U RЕРН, то результат преобразования будет равен $FF, код $00 соответствует напряжениям Uизм ≤ UREFL. Для достижения максимальной точности измерения следует выбрать максимально относительно малые погрешности.

Собственно аналого-цифровой преобразователь выполнен по способу последовательного приближения. Принцип действия АЦП иллюстрируют функциональная схема и временные диаграммы (рис. 4.16 и 4.17).

Вставить рис 4.16

АЦП включает регистр последовательного приближения, цифроаналоговый преобразователь, компаратор, генератор импульсов синхронизации, схему управления, регистр результата ADCDATA и триггер готовности данных. Начало преобразования задает сигнал «Пуск», который устанавливает регистр последовательного приближения в состояние 10000000. При этом на выходе ЦАП формируется напряжение, равное половине опорного. Компаратор сравнивает измеряемое напряжение с напряжением ЦАП. Если Ц,зм > t/цдр, то в регистре последовательного приближения формируется следующий код сравнения, равный 11000000. Если U/изм < U/цап, то старший разряд регистра последовательного приближения устанавливается в «0», следующий код сравнения равен 01000000. Таким образом, на первом такте измеряемое напряжение сравнивается с эталонным значением U оп/2. Аналогичные действия выполняются в каждом из тактов преобразования, однако значение напряжения сравнения зависит от результатов сравнения в предыдущих тактах. В примере рис. 4.2 на втором такте напряжение сравнения равно U оп/2 + Uon/4, на третьем такте U оп/2 + Uon/8 - поскольку на втором такте было установлено, что Uизм < U оп/2 + Uon/4. Интервал преобразования состоит из n тактов: один такт для получения каждого двоичного разряда слова результата. Точность аналого-цифрового преобразования определяется разрешающей способностью блока ЦАП. В разных моделях МК он может быть выполнен на основе матрицы из 256 резисторов равных номиналов, матрицы весовых резисторов R/2R, достаточно часто встречается решение на основе емкостного делителя. Однако во всех моделях МК разрешающая способность ЦАП составляет 8 двоичных разрядов. Соответственно формат представления результата измерения АЦП-однобайтовый. Исключение составляют лишь модули АЦП микроконтроллеров для управления преобразователями частоты электропривода, разрешающая способность которых равна 10 двоичным разрядам. Два младших разряда результата получают с помощью дополнительного емкостного делителя, не связанного с регистром последовательного приближения. Длительность такта преобразования задает генератор синхронизации: один цикл равен двум периодам частоты генератора fADC.

Время преобразования можно рассчитать по формуле t изм = = (2n+1)tАDС, последний цикл необходим для переноса результата в регистр данных АЦП. Частота генератора синхронизации, как правило, не может быть выбрана произвольно. Ее ограничение определяется двумя обстоятельствами:

1)конденсаторы емкостного делителя неидеальны и имеют определенное сопротивление утечки; поэтому длительность такта измерения должна быть, с одной стороны,

достаточна для заряда конденсаторов до уровня напряжения, определяемого разряда

ми регистра последовательного приближения, а с другой стороны, не слишком большой,

чтобы погрешность утечки не была значительной;

2)в некоторых моделях источник питания аналоговой части модуля АЦП выполнен на основе импульсного преобразователя; для его работы требуется тактирование,

частота тактирования определена с достаточно узким допуском ±10 %.

Источником синхронизации модуля АЦП может служить встроенный RC-генератор или импульсная последовательность тактирования межмодульных магистралей МК. В первом случае частота синхронизации АЦП обязательно окажется оптимальной, той, которая рекомендуется в техническом описании. Во втором случае выбранная в результате других соображений fBUS может оказаться неподходящей для модуля АЦП. На этот случай в составе некоторых модулей предусмотрен программируемый делитель частоты feus.

Большинство моделей АЦП имеет только режим программного запуска: установка одного из битов регистра режима запускает очередное измерение. Наиболее универсальные модули АЦП имеют также режим автоматического запуска, при котором после завершения одного цикла преобразования немедленно начинается следующий. Однако данные измерения каждого цикла должны быть считаны программным способом (см. модуль ADC08 НС08 фирмы «Motorola»).

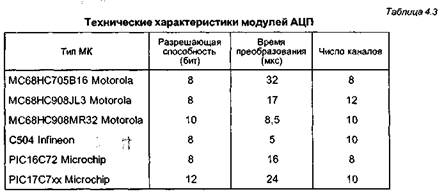

В заключение приведем технические характеристики модулей АЦП некоторых популярных 8-разрядных МК (табл. 4.3).

Цифроаналоговые преобразователи в составе МК являются большой редкостью. Модули параллельных ЦАП можно встретить лишь в МК «Mitsubishi» и «Hitachi».

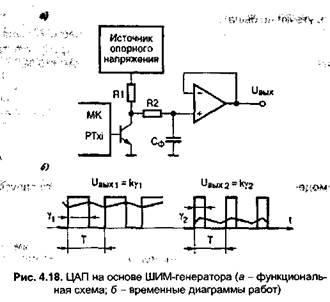

Функция цифроаналогового преобразователя реализуется средствами модуля программируемого таймера. На одном из выводов МК формируется высокочастотная импульсная последовательность с регулируемой длительностью импульса.

Полученный сигнал сглаживается фильтром нижних частот на операционном усилителе (рис. 4.18). Разрешающая способность такого ЦАП определяется дискретностью регулирования коэффициента заполнения у в режиме ШИМ. Как было отмечено в п. 4.1.6, немногие модели 8-разрядных МК способны реализовать с дискретностью более 8 разрядов (табл. 4.3). Этим вызвана необходимость применения внешних ИС ЦАП. Кроме того, частота ШИМ сигнала определяет время преобразования ЦАП, этим объясняется особая привлекательность МК с частотой ШИМ в десятки килогерц.