Основою побудови будь-якого пристрою, що використовує цифрову інформацію, є елементи двох типів: логічні і запам'ятовуючі. Логічні елементи виконують найпростіші логічні операції над цифровими сигналами. Запам'ятовуючі елементи служать для зберігання цифрової інформації.

Логічна операція полягає в перетворенні за певними правилами вхідних цифрових сигналів у вихідні. Математично цифрові сигнали позначають порозрядно символами, наприклад x1, x2, x3, x4. Їх називають змінними. Кожна змінна може приймати значення "0" або "1". Результат логічної операції часто позначають F або Q. Він також може мати значення "0" або "1". Математичним апаратом логіки є алгебра Буля. У булевой алгебрі над змінними "0" або "1" можуть виконуватися три основні дії: логічне додавання, логічне множення і логічне заперечення.

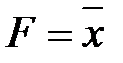

Логічне заперечення (інверсія або операція НЕ) записується у вигляді

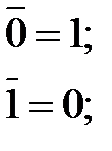

і читається: F рівне не x. Правила виконання операції НЕ полягають в наступному:

Логічні схеми, що реалізують операцію НІ називаються елементами НІ. Їх графічне позначення наведено на рис. 1. Операція НЕ може бути реалізована схемою транзисторного ключа.

Рис. 1. Умовне графічне зображення (закордонне зліва, вітчизняне справа) та

приклад реалізації логічного елементу НІ.

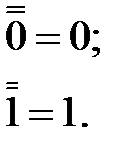

В одному корпусі мікросхеми зазвичай буває шість інверторів. Вітчизняне позначення мікросхем інверторів - "ЛН".

| Таблиця істинності інвертора | |

| Вхід | Вихід |

Дві основні сфери застосування інверторів - це зміна полярності сигналу і зміна полярності фронту сигналу. Тобто з позитивного вхідного сигналу інвертор робить негативний вихідний сигнал і навпаки, а з позитивного фронту вхідного сигналу - негативний фронт вихідного сигналу і навпаки. Ще одне важливе застосування інвертора - збільшення навантажувальної здатності вихідного сигналу. Це буває потрібно в тому випадку, коли якийсь сигнал треба подати на багато входів, а вихідний струм джерела сигналу недостатній, або до виходу логічного елементу необхідно підєднати потужне навантаження.

Логічне додавання (диз'юнкція або операція АБО) записується у вигляді

Правила виконання операції АБО полягають в наступному:

0 + 0 = 0; 1 + 0 = 1;

0 + 1 = 1; 1 + 1 = 1.

Логічні схеми, що реалізують операцію АБО називаються елементами АБО. Їх схемне позначення і найпростіша реалізація на діодах приведені на рис. 2. Напруга на виході схеми дорівнюватиме лог. одиниці, якщо хоча б на один з входів буде поданий одиничний сигнал.

Рис. 2. Умовне графічне зображення (закордонне зліва, вітчизняне справа) та

реалізація логічного елементу АБО.

Логічне множення (кон'юнкція або операція І) записується у вигляді

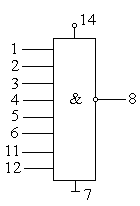

Правила виконання операції І полягають в наступному

Логічні схеми, що реалізують операцію І називаються елементами І. Їх схемне позначення і найпростіша реалізація на діодах наведено на рис. 3. Напруга на виході  тільки в тому випадку, якщо всі діоди будуть закриті, тобто на всіх входах буде потенціал Е (логічна 1). В іншому випадку відкритий діод шунтує навантаження і

тільки в тому випадку, якщо всі діоди будуть закриті, тобто на всіх входах буде потенціал Е (логічна 1). В іншому випадку відкритий діод шунтує навантаження і  .

.

Рис. 3. Умовне графічне зображення (закордонне зліва, вітчизняне справа) та

реалізація логічного елементу І.

Набір логічних елементів, який дозволяє реалізувати логічну функцію будь-якої складності називається БАЗИСОМ. За допомогою елементів І, АБО, НІ можна синтезувати будь – яку функцію тому ці елементи є базисом.

Поряд з елементами І та АБО широко застосовуються елементи І-НІ та АБО-НІ. Це звичайні елементи І та АБО на вихід яких ввімкнутий інвертор. Використовуючи лише елементи І-НІ (АБО-НІ) можна також реалізувати логічну функцію будь-якої складності тому елементи І-НІ (АБО-НІ) також є базисом.

| Таблиця істинності двоходових елементів І, І-НІ, АБО, АБО-НІ | |||||

| Вхід 1 | Вхід 2 | Вихід І | Вихід І-НІ | Вихід АБО | Вихід ИЛИ-НІ |

Серії цифрових мікросхем

В даний час випускається величезна кількість різноманітних цифрових мікросхем: від найпростіших логічних елементів до найскладніших процесорів, мікроконтролерів і спеціалізованих ВІС (великих інтегральних мікросхем). Виробництвом цифрових мікросхем займається безліч фірм - як у нас в країні, так і за кордоном. Тому навіть класифікація цих мікросхем являє собою досить важке завдання.

Однак як базису в цифровій схемотехніці прийнято розглядати класичний набір мікросхем малої і середньої ступені інтеграції, в основі якого лежать ТТЛ серії сімейства 74, що випускаються вже кілька десятиліть рядом фірм, наприклад, американською фірмою Texas Instruments.

Кожна мікросхема серій сімейства 74 має своє позначення, і система позначень яка складається з шести елементів:

1. Ідентифікатор фірми SN (для серій AC і ACT відсутня).

2. Температурний діапазон (тип сімейства):

74 - комерційні схеми (температура навколишнього середовища для біполярних мікросхем - 0... 70 ° С, для КМОП мікросхем - 40... +85 ° С),

54 - мікросхеми військового призначення (температура - 55... +125 ° С).

3. Код серії (до трьох символів):

Відсутня - стандартна ТТЛ-серія.

LS (Low Power Schottky) - малопотужна серія ТТЛШ.

S (Schottky) - серія ТТЛШ.

ALS (Advanced Schottky) - поліпшена серія ТТЛШ.

F (FAST) - швидка серія.

HC (High Speed CMOS) - високошвидкісна КМОП-серія.

HCT (High Speed CMOS with TTL inputs) - серія HC, сумісна по входу з ТТЛ.

AC (Advanced CMOS) - поліпшена серія КМОП.

ACT (Advanced CMOS with TTL inputs) - серія AC, сумісна по входу з ТТЛ.

BCT (BiCMOS Technology) - серія з БіКМОП-технологією.

ABT (Advanced BiCMOS Technology) - поліпшена серія з БіКМОП-технологією.

LVT (Low Voltage Technology) - серія з низькою напругою живлення.

4. Ідентифікатор спеціального типу (2 символи) - може бути відсутнім.

5. Тип мікросхеми (від двох до шести цифр). Перелік деяких типів мікросхем наведено в додатку.

6. Код типу корпусу (від одного до двох символів) - може бути відсутнім. Наприклад, N - пластмасовий корпус DIL (DIP), J - керамічний DIL (DIC), T - плоский металевий.

Приклади позначень: SN74ALS373, SN74ACT7801, SN7400.

Вітчизняна система позначень мікросхем відрізняється від розглянутої досить істотно:

1. Область застосування: Буква К позначає мікросхеми широкого застосування, для мікросхем військового призначення буква відсутня.

2. Тип корпусу мікросхеми (один символ) - може бути відсутнім. Наприклад, Р - пластмасовий корпус, М - керамічний, Б - безкорпусна мікросхема.

3. Номер серії мікросхем (від трьох до чотирьох цифр).

4. Функція мікросхеми (дві літери).

5. Номер мікросхеми (від однієї до трьох цифр).

Наприклад, КР1533ЛА3, КР531ІЕ17, КР1554ІР47.

Головна перевага вітчизняної системи позначень полягає в тому, що з позначення мікросхеми можна легко зрозуміти її функцію. Зате в системі позначень Texas Instruments видно тип серії з його особливостями.

Широке розповсюдження знайшли елементи ТТЛ серій. Схема двоходового ТТЛ елемента 2І-НІ наведена на рис. 4.

Рис. 4. ТТЛ елемент 2І-НІ.

Відмінною його рисою є наявність на вході багатоемітерного транзистора VТІ, що є набутком інтегральної технології і замінює вхідний діодний вузол елементів РДТЛ.

Елемент ТТЛ має складний двотактний вихідний каскад, що дозволяє збільшити навантажувальну здатність елемента - знижує вплив опору колекторного резистора на величину вихідного сигналу логічної 1.

Діод VD (як пороговий елемент із напругою відкривання близько 0,6 В) надійно забезпечує вимкнений стан транзистора VT3 при відкритому VT2 (падіння на якому складає 0,2-0,4 В).

На рис. 5. наведена схема двовходового елемента І-НІ, виконаного на комплементарних КМДН транзисторах. Як видно з рисунку, він складається тільки з чотирьох МДН-транзисторів, які одночасно виконують і роль резисторів, бо опір їх каналу становить від десятків до сотень ом.

Рис. 5. Елемент КМДН логіки 2І-НІ.

Вихід елемента транзисторними ключами VT1 або VT2 підмикається до шини живлення, а VT3 і VT4 - до нульової шини.

Елементи КМДН прості у виготовленні (а значить дешеві), мають більшу завадостійкість, ніж елементи ТТЛ, а за частотними властивостями в останній час наближаються до них.

Перевагою КМДН логіки є ще й те, що вона працездатна у широкому діапазоні змін напруги живлення. Так, якщо для ІМС ТТЛ типове значення напруги живлення становить 5 В ± 5 %, то для ІМС КМДН вона може становити від 3 до 15 В.

В додатку наведені параметри цифрових ІМС, ТТЛ та КМДН типів

ХІД РОБОТИ

1.1. Зберіть схему вимірювання передавальної характеристики U ВИХ(UВХ ) ЛЕ ТТЛ логіки.

1.2. Виміряйте та занесіть до таблиці 1 значення U ВИХ, UВХ змінюючи вхідну напругу логічного елементу за допомогою резистора R4.

Таблиця 1

| UВХ | ||||||||||

| UВИХ |

1.3. Зберіть схему вимірювання вхідної характеристики І ВХ(UВХ ) ЛЕ ТТЛ логіки.

1.4. Виміряйте та занесіть до таблиці 2 значення U 1, UВХ змінюючи вхідну напругу логічного елементу за допомогою резистора R4. За формулою ІВХ = (U1– UВХ)/ R2 розрахуйте та внесіть до таблиці 2 значення вхідного струму ЛЕ.

Таблиця 2

| UВХ | ||||||||||

| U1 | ||||||||||

| ІВХ |

1.5. Зберіть схему вимірювання вихідної характеристики І ВИХ(UВИХ ) ЛЕ ТТЛ логіки.

1.6. Виміряйте та занесіть до таблиці 3 значення U 2, UВИХ змінюючи вихідний струм логічного елементу за допомогою резистора R5. За формулою ІВИХ = (UВИХ – U2)/ R4 розрахуйте та внесіть до таблиці 3 значення вихідного струму одиниці (S1 в положенні «0») та нуля (S1 в положенні «1»)

Таблиця 3

| UВИХ | ||||||||||

| U2 | ||||||||||

| ІВИХ 0 | ||||||||||

| ІВИХ 1 |

2.1. Зберіть схему вимірювання передавальної характеристики U ВИХ(UВХ ) ЛЕ КМДМ логіки.

2.2. Виміряйте та занесіть до таблиці 4 значення U ВИХ, UВХ змінюючи вхідну напругу логічного елементу за допомогою резистора R6.

Таблиця 4

| UВХ | ||||||||||

| UВИХ |

2.3. Зберіть схему вимірювання вихідної характеристики І ВИХ(UВИХ ) ЛЕ КМДН логіки.

2.4. Виміряйте та занесіть до таблиці 5 значення U 3, UВИХ змінюючи вихідний струм логічного елементу за допомогою резистора R10. За формулою ІВИХ = (UВИХ – U3)/ R9 розрахуйте та внесіть до таблиці 5 значення вихідного струму одиниці (S6 в положенні «0») та нуля (S6 в положенні «1»)

Таблиця 5

| UВИХ | ||||||||||

| U3 | ||||||||||

| ІВИХ 0 | ||||||||||

| ІВИХ 1 |

3.1. Користуючись даними таблиці 1 та 4 побудуйте в одних координатах передавальні характеристики U ВИХ=f(UВХ ) ЛЕ ТТЛ та КМДН логікивикористовуючи Майстер діаграм MS EXCEL.

3.2. Користуючись даними таблиці 2 побудуйте вхідну характеристику І ВХ=f(UВХ ) ЛЕ ТТЛ логіки використовуючи Майстер діаграм MS EXCEL.

3.3. Користуючись даними таблиці 3 побудуйте вихідну характеристику І ВИХ=f(UВИХ ) ЛЕ ТТЛ логіки використовуючи Майстер діаграм MS EXCEL.

3.4. Користуючись даними таблиці 5 побудуйте вихідну характеристику І ВИХ=f(UВИХ ) ЛЕ КМДН логіки використовуючи Майстер діаграм MS EXCEL.

4. Користуючись експериментальними ВАХ ПТ виконайте дії, згідно із завданням до лабораторної роботи.

ЗАВДАННЯ

4.1.Які найпростіші логічні функції Ви знаєте?

4.2.Наведіть можливі способи реалізації простих логічних функцій за допомогою електронних пристроїв.

4.3.Що таке багатоемітерний транзистор?

4.4.Поясніть, чому елементи КМДН-логіки дешеві у виготовленні.

4.5.Вкажіть, чим визначається кількість можливих комбінацій на вході логічного елемента.

4.6.Дайте визначення поняття базису

4.7.Назвіть основні параметри логічного елемента.

4.8.Використовуючи передавальну характеристику визначте порогову напругу для ТТЛ елементів.

4.9. Використовуючи вхідну характеристику ТТЛ елементу визначте  ,

,  .

.

4.10. Використовуючи вихідну характеристику ТТЛ елементу визначте  ,

,  .

.

4.11. Розрахуйте коефіцієнт розгалуження елементів ТТЛ, використовуючи дані п.10 та п.11.

4.12. Використовуючи передавальну характеристику визначте порогову напругу для КМДН елементів.

4.13. Оцініть точність відтворення логічних рівнів логічними елементами ТТЛ та КМДН логіки.

5. Вимоги до оформлення звіту.

Звіт необхідно оформити в текстовому редакторі MS WORD.

Звіт повинен містити:

- титульну сторінку;

- мету роботи;

- схеми дослідів;

- таблиці з даними;

- графіки ВАХ;

- розрахунки параметрів згідно із індивідуальним завданням.

ДОДАТКИ

Схема електрична принципова лабораторного макету.

Приклади реалізації цифрових ІМС ТТЛ та КМДН типів

Параметри цифрових ІМС, ТТЛ та КМДН типів.

Додаток 1

Додаток 2

Приклади реалізації цифрових ІМС ТТЛ та КМДН типів

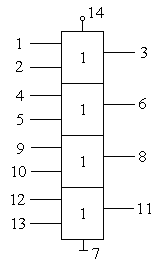

| Шесть элементов НЕ | Шесть буферных формирователей с открытым коллекторным выходом | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛН1, К155ЛН2, К155ЛН3, К155ЛН5, КP1533ЛН1, КP1533ЛН2

К155ЛН1, К155ЛН2, К155ЛН3, К155ЛН5, КP1533ЛН1, КP1533ЛН2

|  К155ЛН4

К155ЛН4

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

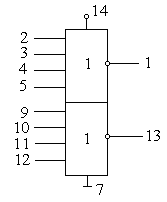

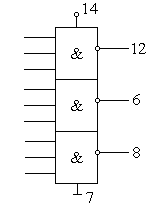

| Шесть логических элементов с буферным выходом | Два логических элемента 4И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К564ЛН2

К564ЛН2

|  К555ЛИ, КР1533ЛИ6

К555ЛИ, КР1533ЛИ6

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

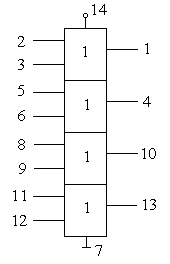

| Четыре логических элемента 2И | Три логических элемента 3И | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛИ5

К155ЛИ5

|  К555ЛИ1, КР1533ЛИ6

К555ЛИ1, КР1533ЛИ6

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

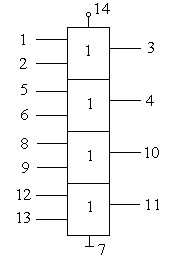

| Четыре логических элемента 2ИЛИ | Два логических элемента 4ИЛИ-НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЛ1, К555ЛЛ1, КР1533ЛЛ1

К155ЛЛ1, К555ЛЛ1, КР1533ЛЛ1

|  К564ЛЕ6, К561ЛЕ6

К564ЛЕ6, К561ЛЕ6

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Четыре логических элемента 2ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЕ1, К555ЛЕ1, К155ЛЕ5, К155ЛЕ6

К155ЛЕ1, К555ЛЕ1, К155ЛЕ5, К155ЛЕ6

|  К561ЛЕ5, К564ЛЕ5

К561ЛЕ5, К564ЛЕ5

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Три логических элемента 3ИЛИ-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛЕ4, К555ЛЕ4

К155ЛЕ4, К555ЛЕ4

|  К561ЛЕ10, К564ЛЕ10

К561ЛЕ10, К564ЛЕ10

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Три логических элемента 3И-НЕ | Четыре логических элемента 2И-НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К564ЛА9

К564ЛА9

|  К155ЛА8, К555ЛА8

К155ЛА8, К555ЛА8

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Логический элемент 8И-НЕ | Два логических элемента 4И-НЕ | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛА2, К55ЛА2, КР1533ЛА2

К155ЛА2, К55ЛА2, КР1533ЛА2

|  К155ЛА1, К155ЛА6, К155ЛА7, К555ЛА1, К555ЛА7, КР1533ЛА1, КР1533ЛА7

К155ЛА1, К155ЛА6, К155ЛА7, К555ЛА1, К555ЛА7, КР1533ЛА1, КР1533ЛА7

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Три логических элемента 3И-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛА4, К155ЛА10, К555ЛА10

К155ЛА4, К155ЛА10, К555ЛА10

|  К555ЛА4, КР1533ЛА4

К555ЛА4, КР1533ЛА4

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Четыре элемента 2И-НЕ | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

К155ЛА3, К155ЛА9, К155ЛА12, К155ЛА13, К555ЛА3, К555ЛА9, К555ЛА12, К555ЛА13, КР1533ЛА3, КР1533ЛА9

К155ЛА3, К155ЛА9, К155ЛА12, К155ЛА13, К555ЛА3, К555ЛА9, К555ЛА12, К555ЛА13, КР1533ЛА3, КР1533ЛА9

|  К561ЛА7, К564ЛА7, К176ЛА7

К561ЛА7, К564ЛА7, К176ЛА7

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Додаток 3

Основні параметри та характеристики мікросхем КР155

| Входной ток, мА, не более Низкого уровня ……………………………………………… Высокого уровня …………………………………………… | -1,6 0,04 |

| Выходное напряжение, В Низкого уровня, не более …………………………………. Высокого уровня, не менее | 0,4 2,4 |

| Выходной ток, мА, не более Низкого уровня ……………………………………………. Высокого уровня …………………………………………… | -0,4 |

| Нагрузочная способность…………………………………………… | |

| Время задержки распространения сигнала, нс, при Включении (С н=50 пФ) ……………………………………. Выключении (С н=50 пФ) …………………………………… | 18,5* 18,5* |

| Средний ток потребления, мА, не более …………………………. | 15* |

| Помехоустойчивость, В, не более ………………………………… | 0,4 |

| Максимальное напряжение питания, В …………………………… | |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В 155 …………………………………………………………… КР155 ………………………………………………………. | 4,5 – 5,5 4,75–5,25 |

| Максимальная емкость нагрузки, пФ ……………………………. | |

| Диапазон рабочих температур, С 155 …………………………………………………………… КР155 ………………………………………………………. | -60+125 -10..+70 |

Основні параметри та характеристики мікросхем

| Входной ток, мА, не более Низкого уровня ……………………………………………… Высокого уровня …………………………………………… | -0,4 0,04 |

| Выходное напряжение, В Низкого уровня, не более …………………………………. Высокого уровня, не менее | 0,4 2,5 |

| Выходной ток, мА, не более Низкого уровня ……………………………………………. Высокого уровня …………………………………………… | -0,4 |

| Нагрузочная способность…………………………………………… | |

| Время задержки распространения сигнала, нс, при Включении (С н=50 пФ) ……………………………………. Выключении (С н=50 пФ) …………………………………… | 20* 20* |

| Средний ток потребления, мА, не более …………………………. | 3* |

| Помехоустойчивость, В, не более ………………………………… | 0,3 |

| Максимальное напряжение питания, В …………………………… | 5,5 |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В 555 …………………………………………………………… КР555 ………………………………………………………. | 45, – 5,5 4,75–5,25 |

| Максимальная емкость нагрузки, пФ ……………………………. | |

| Диапазон рабочих температур, С 555 …………………………………………………………… КР555 ………………………………………………………. | -60+125 -10..+70 |

*Для микросхем типа ЛА3

Основні параметри та характеристики мікросхем КР1533

| Входной ток, мА, не более Низкого уровня ……………………………………………… Высокого уровня …………………………………………… | -0,2 0,02 |

| Выходное напряжение, В Низкого уровня, не более …………………………………. Высокого уровня, не менее | 0,4 2,5 |

| Выходной ток, мА, не более Низкого уровня ……………………………………………. Высокого уровня …………………………………………… | -0,2 |

| Нагрузочная способность…………………………………………… | |

| Время задержки распространения сигнала, нс, при Включении (С н=50 пФ) ……………………………………. Выключении (С н=50 пФ) …………………………………… | |

| Средний ток потребления, мА, не более …………………………. | |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Максимальное напряжение питания, В …………………………… | |

| Максимальное напряжение на входе, В …………………………. | 5,5 |

| Минимальное напряжение на входе, В …………………………… | -0,4 |

| Напряжение питания, В……………………………………………. | 45, – 5,5 |

| Максимальная емкость нагрузки, пФ ……………………………. | |

| Диапазон рабочих температур, С……………………………… | -10..+70 |

Основні параметри та характеристики мікросхем КР176

| Входной ток, мкА, не более Низкого уровня ……………………………………………… Высокого уровня …………………………………………… | 1,0 1,0 |

| Выходное напряжение, В Низкого уровня, не более …………………………………. Высокого уровня, не менее | 0,3 8,2 |

| Выходной ток, мкА, не более Низкого уровня ……………………………………………. Высокого уровня …………………………………………… | -0,2 |

| Нагрузочная способность…………………………………………… | |

| Время задержки распространения сигнала, нс, при Включении (С н=50 пФ) ……………………………………. Выключении (С н=50 пФ) …………………………………… | |

| Средний ток потребления, мА, не более …………………………. | |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Максимальное напряжение питания, В …………………………… | |

| Максимальное напряжение на входе, В …………………………. | 8,5 |

| Напряжение питания, В……………………………………………. | 9±5% |

| Максимальная емкость нагрузки, пФ ……………………………. | |

| Диапазон рабочих температур, С……………………………… | 40..+70 |

Основні параметри та характеристики мікросхем КР654

| Входной ток, мкА, не более Низкого уровня ……………………………………………… Высокого уровня …………………………………………… | -0,05 1,0 |

| Выходное напряжение, В Низкого уровня, не более …………………………………. Высокого уровня, не менее | 2,9 7,2 |

| Выходной ток, мкА, не более Низкого уровня ……………………………………………. Высокого уровня …………………………………………… | 0,5 -10 |

| Нагрузочная способность…………………………………………… | |

| Время задержки распространения сигнала, нс, при Включении (С н=50 пФ) ……………………………………. Выключении (С н=50 пФ) …………………………………… | |

| Средний ток потребления, мА, не более …………………………. | |

| Помехоустойчивость, В, не более ………………………………… | 0,8 |

| Максимальное напряжение питания, В …………………………… | |

| Максимальное напряжение на входе, В …………………………. | 9,5 |

| Напряжение питания, В……………………………………………. | 10±10% |

| Максимальная емкость нагрузки, пФ ……………………………. | |

| Диапазон рабочих температур, С……………………………… | -60..+125 |

ЛАБОРАТОРНА РОБОТА № 10

ТЕМА: Дослідження роботи тригерів в інтегральному виконанні.

МЕТА: Дослідити особливості роботи універсальних тригерів в інтегральному виконанні.

ОБЛАДНАННЯ:

- лабораторний макет.

КОРОТКІ ТЕОРЕТИЧНІ ВІДОМОСТІ

В даний час відомо велика кількість різних типів трігерів, що виготовляються у вигляді інтегральних мікросхем. Як правило, це універсальні тригери, тобто тригери, що поєднують в собі функціональні можливості кількох більш простих видів тригерів (наприклад: RS- і D-тригерів, RS-і JK-тригерів і т.д.). Так, наприклад, тригер, зображений на рис.1, поєднує в себе можливості RS- і D-тригерів.

Рис.1

|

Запис інформації в тригер даного типу проводиться по входу D. На вхід С подаються імпульси синхронізації. Крім того, тригер має вхід установки "0" (R - вхід) і вхід установки "1" (S - вхід).

Для керування роботою тригера можуть використовуватися керуючі сигнали різних рівнів. Так, вищевказаний тригер (рис.1) встановлюється в "0" та "1" при подачі на входи S і R сигналів логічної "1" (прямі входи). При управлінні сигналом логічного нуля "0" вводиться спеціальне позначення входів мікросхем (рис.2).

Рис.2

|

Вхід синхронізації може бути як потенційним (рис.1), так і динамічним (рис.2). Приклад роботи синхронного тригера із синхронізацією рівнем по входу С наведений на часових діаграмах рис.3, а із синхронізацією по перепаду на рис. 4.

Як випливає з рис.3, запис інформації в тригер з потенційним входом відбувається при наявності на вході С синхрорівня - логічної "1" (для інших тригерів "0"). При цьому, стан тригера протягом дії синхрорівня змінюється відповідно із надходженням сигналів на вхід D. У динамічному тригері (рис.4) запис інформації в тригер відбувається по позитивному (передньому) фронту синхросигналу при перепад із стану "0" в стан "1" на вході С (для інших тригерів - по негативному (задньому) фронту синхросигналу при перепаді зі стану "1" в стан "0").

Роботу синхронного тригера з керуванням по рівню, можна описати таблицею перемикання (табл.1).

Таблиця 1

| S | R | D | C |

|

| Режим роботи |

| х |

|

| Збереження попередньо записаної інформації | |||

| х х х | х х х | Запис “1” Запис “0” Встановлення “1” Встановлення “0” Заборонена комбінація |

Режим "Зберігання попередньо записаної інформації" означає, що тригер знаходиться у стані, в який він переключився у попередньому такті роботи.

У режимі "Установка "1" і "Установка "0" універсальний тригер функціонує як стандартний RS-тригер. Комбінація вхідних сигналів R = S = 1 є забороненою, тому що при цьому обидва виходи тригера встановлюються в одинаковий стан, що суперечить нормальній роботі тригера.

В режимі "Запис" 0 "і" Запис "1" універсальний тригер функціонує як стандартний D-тригер.

Таблиця перемикання синхронного тригера з керуванням по перепаду з «0» в «1» (табл.2).

Таблиця 2

| S | R | D | C |

|

| Режим роботи |

| х х | ↓ |

|

| Збереження попередньо Записаної інформації | ||

| х х х | ↑ ↑ х х х | Запис “0” Запис “1” Встановлення “1” Встановлення “0” Заборонена комбінація |

Якщо тригер має динамічний вхід синхронізації С (як це показано на рис.2), то в таблиці перемикання для позитивного і негативного фронту вводяться спеціальні позначення "↑" і "↓" відповідно.

Універсальні тригери можуть бути переведені в рахунковий режим роботи, тобто такий режим, при якому стан тригера змінюється на протилежний з приходом кожного наступного імпульсу синхронізації на його С-вхід. У разі використання D-тригера для реалізації рахункового режиму інверсний вихід  з’єднують з входом D, для JK-тригера встановлюють вхідні керюючі сигнали J = K = 1.

з’єднують з входом D, для JK-тригера встановлюють вхідні керюючі сигнали J = K = 1.

ХІД РОБОТИ

1.8. Зберіть схему дослідження універсального D-тригера (тумблер T/D встановіть в положення D).

1.2. Встановлюючи за допомогою тумблерів S, R, D рівні логічних сигналів «1», «0» і імітуючи позитивний імпульс на вході С тригера, переберіть всі можливі комбінації вхідних сигналів D-тригера. За допомогою світлодіодів «Стан Q», «Стан не Q» визначте стан прямого і інверсного виходів тригера, які відповідають вхідним комбінаціям. Результати занесіть до до таблиці 1.

Таблиця 1

| S | R | D | C |

|

| Примітки |

1.3. Проведіть аналіз таблиці та встановіть тип входу С тригера (синхронізація відбувається по рівню чи по перепаду).

1.9. Зберіть схему дослідження універсального D-тригера в рахунковому режимі (тумблер T/D встановіть в положення Т).

2.2. Встановлюючи за допомогою тумблерів S, R рівні логічних сигналів «1», «0» і імітуючи перепад логічного рівня на вході С тригера, переберіть всі можливі комбінації вхідних сигналів D-тригера в рахунковому режимі. За допомогою світлодіодів «Стан Q», «Стан не Q» визначте стан прямого і інверсного виходів тригера, які відповідають вхідним комбінаціям. Результати занесіть до до таблиці 2.

Таблиця 2

| S | R | C |

| D =

| Примітки |

2.3. Проведіть аналіз таблиці 2 та зробіть висновок про можливість роботи D-тригера в якості Т-тригера.

3.1. Користуючись даними таблиці 1 побудуйте часові діаграми роботи D-тригера.

3.2. Користуючись даними таблиці 2 побудуйте часові діаграми роботи D-тригера в лічильному режимі.

4. Користуючись експериментальними даними та теоретичними відомостями виконайте дії, згідно із завданням до лабораторної роботи.

ЗАВДАННЯ

4.1. Наведіть визначення тригера.

4.2. Наведіть класифікацію тригерів.

4.3. Вкажіть, у чому полягає відмінність тригера із синхронізацією по рівню від тригера із синхронізацією по перепаду.

4.4. Визначте, яким перепадом синхронізується D-тригер зібраний з ЛЕ І-НІ.

4.5. Наведіть приклад реалізації D-тригера на ЛЕ І-НІ.

4.6. Визначте, яким перепадом синхронізується D-тригер зібраний з ЛЕ АБО-НІ.

4.7. Наведіть приклад реалізації D-тригера на ЛЕ АБО-НІ.

4.8. Наведіть приклад реалізації JK-тригера на ЛЕ І-НІ.

4.9. Визначте, яким перепадом синхронізується JK-тригер зібраний з ЛЕ І-НІ.

4.10. Визначте, яким перепадом синхронізується JK-тригер зібраний з ЛЕ АБО-НІ.

4.11. Наведіть приклад реалізації JK-тригера на ЛЕ АБО-НІ.

4.12. Поясніть, що таке заборонена комбінація на входах тригера.

4.13. Вкажіть, для яких тригерів існує заборонена комбінація.

4.14. Поясніть, що таке лічильний режим роботи тригера, як реалізується цей ре жим у D та JK-тригерах.

5. Вимоги до оформлення звіту.

· Звіт необхідно оформити в текстовому редакторі MS WORD.

· Звіт повинен містити:

- титульну сторінку;

- мету роботи;

- схеми дослідів;

- таблиці з даними;

- діаграми.

Додаток 1

| Схема електричнА принципова лабораторного макету |

ЛАБОРАТОРНА РОБОТА № 11

ТЕМА: Дослідження мультивібратора.

МЕТА: Дослідити роботу та визначити основні параметри імпульсів мультивібратора на ІМС із роздільним регулюванням тривалості імпульсу та паузи.

ОБЛАДНАННЯ:

- лабораторний макет;

- осцилограф.

КОРОТКІ ТЕОРЕТИЧНІ ВІДОМОСТІ

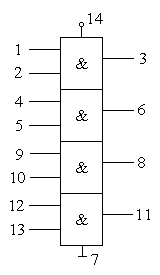

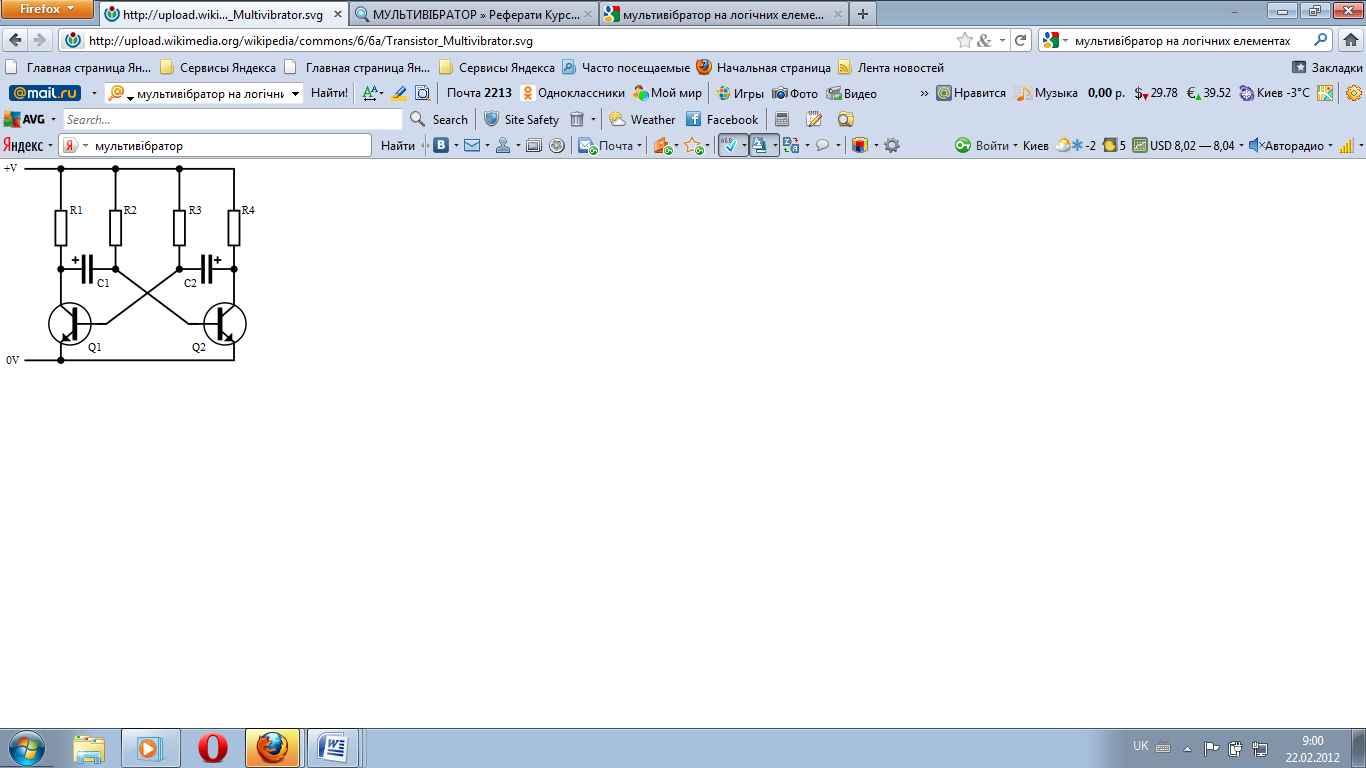

Мультивібра́тор — релаксаційний генератор електричних коливань прямокутного типу. Мультивібратор є одним з найпоширеніших генераторів імпульсів прямокутної форми, що представляє собою двохкаскадний резистивний підсилювач з додатнім зворотним зв'язком.(Рис.1) В електронній техніці використовуються самі різні варіанти схем мультивібратора, які різняться між собою за типом використовуваних елементів (лампові, транзисторні, тиристорні, мікроелектронні і так далі), режиму роботи (автоколивальних, режиму очікування, синхронізації), видами зв'язку між підсилювальними елементами, способах регулювання тривалості і частоти генерованих імпульсів і так далі.

Віднесення мультивібратора до класу автогенератори виправдане лише при автоколивальному режимі його роботи. У режимі очікування мультивібратор виробляє імпульси тільки тоді, коли на його вхід надходять спеціальні сигнали, які його запускають. Режим синхронізації відрізняється від автоколивальних лише тим, що в цьому режимі за допомогою зовнішнього керуючої (синхронізуючої) напруги можна змінювати частоту генерованих коливань.

Віднесення мультивібратора до класу автогенератори виправдане лише при автоколивальному режимі його роботи. У режимі очікування мультивібратор виробляє імпульси тільки тоді, коли на його вхід надходять спеціальні сигнали, які його запускають. Режим синхронізації відрізняється від автоколивальних лише тим, що в цьому режимі за допомогою зовнішнього керуючої (синхронізуючої) напруги можна змінювати частоту генерованих коливань.

Рис.1. Схема мультивібратора на біполярних транзисторах