Для статичних ОЗП та пам’яті типу ROM характерні структури 2D, 3D, 2DM та блочні структури на їх основі, рис.2.

Структуру пам’яті визначає спосіб розподілу КП між адресними та розрядними лініями. За цією ознакою виділяють такі структури пам’яті: 2D, 3D, 2,5D і модифіковану 2DМ (D від Dimention - розмірність).

Структуру пам’яті визначає спосіб розподілу КП між адресними та розрядними лініями. За цією ознакою виділяють такі структури пам’яті: 2D, 3D, 2,5D і модифіковану 2DМ (D від Dimention - розмірність).

а б в г

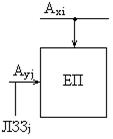

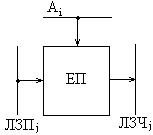

Рис. 2 Узагальнене поняття структури пам’яті: а - 2D; б - 3D; в – 2,5D; г - 2DM.

Кожна матриця (М) в пристрої пам’яті має систему адресних і розрядних ліній (провідників). Адресні (словникові) лінії служать для виділення за адресою будь-якої комірки пам’яті (КП). Сукупність різних адресних кодів утворює адресний простір пам’яті. Розрядні лінії записування (ЛЗП) служать для введення в кожний розряд вибраної КП цифри 0 або 1 відповідно до вхідної інформації. Розрядні лінії зчитування (ЛЗЧ) служать для знімання інформації, яка зберігається, з розряду вибраної КП. Часто використовують спільну лінію записування-зчитування (ЛЗЗ). Адресні та розрядні лінії разом називаються лініями вибірки. Якщо довжина адресного коду дорівнює k, то кількість слів N, які зберігаються в пам’яті як окремі одиниці даних, визначаються із співвідношення N = 2k.

Структура типа 2D використовується лише в ПЗ малої інформаційної ємності, так як при рості ємності проявляється декілька її недоліків, найбільш явним із котрих являється надмірне ускладнення дешифратора адреси (кількість виходів дешифратора рівно числу зберігаючих слів). У системі 2D кожний ЕП має одну адресну лінію Аj (одне D), лінії записування ЛЗПj і зчитування ЛЗЧj, які спільно утворюють друге D (рис. 2, а).

Структура 3D дозволяє різко спростити дешифрування адреси за допомогою двухкоординатної вибірки запам’ятовуючих елементів.

У структурі 3D адресу розподіляють на дві частини: старша Ах визначає адреси рядків, а молодша Ау – адреси стовпців; разом вони утворюють 2D. Лінії записування і зчитування утворюють третє D (рис. 2, б). Структури типу 3D мають також досить обмежене застосування, оскільки в структурах типу 2DМ поєднуються переваги обох розглянутих структур - спрощується дешифрація адреси і не потрібні запам'ятовуючі елементи з двокоординатною вибіркою. У структурі 2,5D одна з ЛЗП або ЛЗЧ суміщена з напівадресою Ахі або Ауj (рис. 2, в). В структурах типа 2DМ поєднуються переваги структур 2D, 3D – спрощується дешифрація адреси і не потребується ЕП з двухкоординатною вибіркою. У модифікованій системі 2DM використовується спільна лінія ЛЗЗJ, яка поєднується з адресною лінією Ауі. Структури динамічних ОЗП мають свою специфіку.

Мікросхеми пам’яті

Основні типи ЗП та їх умовне позначення наведені в таб.1.

Таблиця1.

| Назва ЗП | Позначення ЗП | |

| За ЕСКД | Види ІС | |

| Оперативні ЗП (ОЗП) | RAM – Random Access Memory | РУ |

| Постійні ЗП (ПЗП) · масочні · програмовані ПЗП | ROM –Read Only Memory PROM - Programmable ROM | РЕ РТ |

| Репрограмовані ПЗП (РПЗП) · з ультрафіолетом стиранням і електрозаписом інформації · з елктроперезаписом інформації | EPROM – Erasable Programmable ROM EEPROM – Electrically Erasable Programmable ROM | РФ РР |

| Асоціативні ЗП (АЗП) | CAM | РА |

| Інші ЗП | РП |

Приклад. Мікросхеми оперативних запам’ятовуючих пристроїв

КР541РУ2А Статичний оперативний ЗП на основі інжекційних структур

Інформаційна ємність 4096 біт

Організація 1024 слів х 4 розряда

Напруга живлення 5В ± 5%

Сумісність по входу й виходу із ТТЛ-схемами

Таблиця істинності мікросхеми К541РУ2А К541РУ2,

Таблиця 2 К541РУ2, К541РУ2А

| CS |

| A0…A9 | DIO0…DIO3 | Режим роботи |

| Х | Х А А А | Roff Вихідні дані в прямому коді | Зберігання Запис 0 Запис 1 Зчитування |

Рис. 3

Призначення виводів мікросхем КР 541РУ2А

Таблиця 3

| Виводи | Призначення | Позначення |

| 1…7, 15 16, 17 11…14 | Адресні входи Вхід-вихід даних Вибір мікросхеми Сигнал запис – зчитування Напруга живлення Загальний | А6…А3, А0…A2,

А9…А7

DIO3…DIO0

UCC

0B

UCC

0B

|

КР565РУ2А Статичний оперативний ЗП на основі n-МОП-структур

Інформаційна ємність 1024 біт

Організація 1024 х Х1 розряд

Напруга живлення 5 В ± 10%

Сумісність по входу й виходу із ТТЛ-схемами

Призначення виводів мікросхем КР565РУ2А

Таблиця 4

| Виходи | Призначення | Позначення |

| 1, 2, 4…8, 14…16 | Адресні входи Вхід даних Вихід даних Вибір мікросхеми Сигнал - запис | А6, А5, А1… А4, А0, А9… А7

DI

D0

|

КР565РУ2А

Таблиця істинності мікросхем КР565РУ2А

Таблиця 5

| CS |

| DI | D0 | Режим роботи | |

| Х | Х А А А | Х Х | Roff Дані в прямому коді | Зберігання Запис 0 Запис 1 Зчитування |

Рис.4