Состояние триггера определяется выходным (прямым Q или инверсным  ) сигналом. Триггер является элементарным автоматом Мура. Поэтому принципы его функционирования можно описывать всеми способами, применяемыми для описания таких автоматов. Чаще всего функциональную зависимость между входными и выходными сигналами в двух соседних тактах t и t+ 1 работы триггера представляют таблицами переходов. В этих таблицах используют следующие обозначения:

) сигналом. Триггер является элементарным автоматом Мура. Поэтому принципы его функционирования можно описывать всеми способами, применяемыми для описания таких автоматов. Чаще всего функциональную зависимость между входными и выходными сигналами в двух соседних тактах t и t+ 1 работы триггера представляют таблицами переходов. В этих таблицах используют следующие обозначения:

Qt – предшествующее состояние выхода;

Qt +1 – новое состояние, устанавливающееся после

перехода (возможно Qt +1 = Qt);

´ - безразличное состояние сигнала (0 или 1);

- (дефис) – неопределенное состояние.

Аналитическое описание (характеристическое уравнение)

Qt +1= f (Qt, At +1, Tt +1)

функционирования триггера и его минимальную форму можно получить по правилам, описанным при рассмотрении минимизации полных и частичных автоматов. В характеристическом уравнении через At +1 обозначены информационные входные сигналы, а через Tt +1 - тактовые сигналы, действующие на t +1 такте. Поскольку выходной сигнал триггера отождествляется с его состоянием, то таблица переходов триггера одновременно является и его таблицей выходов.

В качестве примера проведем анализ функционирования RS -триггеров и синтез соответствующих схем, построенных на элементах И-НЕ и ИЛИ-НЕ. Схемы RS -триггеров составляют основу для построения других типов триггеров и являются основными узлами для построения последовательных схем.

Пример 1. RS -триггер имеет два установочных входа: вход установки S и вход сброса R, на которые подаются входные сигналы от внешних источников питания. При подаче на вход установки активного логического уровня триггер устанавливается в состояние 1 (Q = 1,  = 0), а при подаче активного уровня на вход сброса триггер устанавливается в состояние 0 (Q = 0,

= 0), а при подаче активного уровня на вход сброса триггер устанавливается в состояние 0 (Q = 0,  = 1). Если подать на оба входа установки (возбуждения) пассивный уровень, то триггер будет сохранять предыдущее состояние выходов: Q = 0 (

= 1). Если подать на оба входа установки (возбуждения) пассивный уровень, то триггер будет сохранять предыдущее состояние выходов: Q = 0 ( = 1), либо Q = 1 (

= 1), либо Q = 1 ( = 0). Каждое состояние является устойчивым и поддерживается за счет действия обратных связей.

= 0). Каждое состояние является устойчивым и поддерживается за счет действия обратных связей.

Для триггеров этого типа является недопустимой одновременная подача активного уровня на оба входа установки, так как триггер по определению 1 не может одновременно быть установлен в логический нуль или логическую единицу.

На практике подача активного уровня на установочные входы приводит к тому, что это состояние не может быть сохранено, и невозможно определить, в каком состоянии будет находиться триггер при последующей подаче на установочные входы сигналов пассивного уровня.

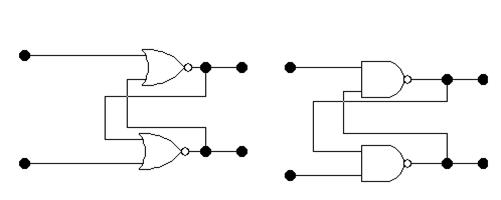

RS -триггеры бывают двух видов: асинхронные и синхронные. Рассмотрим схему и функционирование асинхронного RS -триггера. На рисунках 2 а) и б) показаны схемы асинхронного RS -триггера, выполненные соответственно на элементах ИЛИ-НЕ и И-НЕ (на рисунках отрицания обозначены апострофом). На рисунках 3 а) и б) приведены условные графические изображения соответствующих триггеров. Буква T на этих рисунках означает, во-первых, что это триггер, а во-вторых, что этот триггер однотактный (на практике встречаются и двухтактные триггеры, на условном графическом изображении которых ставится две буквы T).

|

|

|

|

|

|

|

|

|

|

|

|

а) б)

Рисунок 2. Логическая структура асинхронного RS -триггера: а) на стрелках Пирса; б) на штрихах Шеффера

|

а) б)

|

Для схемы, изображенной на рис.2 а) активным уровнем является уровень логической единицы, для схемы, изображенной на рис.2 б) – уровень логического нуля. Схема, изображенная на рис.3 б) получила название асинхронного RS -триггера с инверсными входами.

Схема RS -триггера, изображенного на рис.2 а), состоит из двух логических элементов ИЛИ-НЕ, точнее 2ИЛИ-НЕ, связанных таких образом, что выход каждого элемента подключен к одному из входов другого. Такое соединение элементов в устройстве обеспечивает два устойчивых состояния, в чем легко убедиться. Действительно, пусть на входах R и S действуют постоянные для элементов ИЛИ-НЕ уровни логического нуля, которые не влияют на состояние триггера. В состоянии 0 триггера на выходе элемента АQ = 0. Этот уровень подается на вход элемента В, при этом на обоих входах элемента В действует уровень логического нуля и на выходе элемента Q =1. С выходом элемента В уровень логической единицы поступает на вход элемента А, что и обеспечивает на его выходе уровень 0. Это одно из устойчивых состояний триггера. В состоянии 1 триггера на выходе элемента АQ =1, что обуславливает на выходе элемента ВQ =0, при этом на обоих выходах элемента А действуют уровни 0, что и обеспечивает на выходе этого элемента уровень логической единицы. Анализ работы триггера показал, что в каждом из состояний триггера элементы А и В оказываются в противоположных состояниях.

Переключение триггера из одного устойчивого состояния в другое происходит при подаче активных сигналов на его входы. Под действием уровня R =1 элемент А установится в состояние, при котором на его выходе Q =0, следовательно, на инверсном выходе  = 1 и, таким образом, триггер устанавливается в состояние 0. Если триггер и прежде, до подачи сигнала R =1, находится в состоянии 0, то его состояние не изменится. Если же триггер находился в состоянии 1, то при подаче сигнала R =1 произойдет переключение элемента А, и на его выходе установится уровень Q =0. Далее этот уровень действует на вход элемента В, переключает его и на выходе элемента В установится уровень Q =1, после чего триггер оказывается установленным в состояние 0. Таким образом, при переключении триггера из одного состояния в другое его элементы последовательно переключаются и время переключения равно удвоенному среднему времени задержки распределения сигнала в логическом элементе ИЛИ-НЕ.

= 1 и, таким образом, триггер устанавливается в состояние 0. Если триггер и прежде, до подачи сигнала R =1, находится в состоянии 0, то его состояние не изменится. Если же триггер находился в состоянии 1, то при подаче сигнала R =1 произойдет переключение элемента А, и на его выходе установится уровень Q =0. Далее этот уровень действует на вход элемента В, переключает его и на выходе элемента В установится уровень Q =1, после чего триггер оказывается установленным в состояние 0. Таким образом, при переключении триггера из одного состояния в другое его элементы последовательно переключаются и время переключения равно удвоенному среднему времени задержки распределения сигнала в логическом элементе ИЛИ-НЕ.

Очевидно, чем меньше время переключения триггера, тем большее число переключений триггера можно произвести в единицу времени, то есть будет выше допустимой частота переключений или, иначе говоря, быстродействие триггера.

Процесс установки триггера в состояние 1 при подаче на вход S уровня логической единицы аналогичен описанному выше процессу.

Одновременная подача активных уровней 1 на оба входа R и S не допускается, так как при этом на обоих выходах установится уровень 0, а после снятия его с входов активных уровней состояние триггера окажется неопределенным.

Как уже отмечалось выше, условия переходов триггеров из одного состояния в другое (алгоритм работы) можно описать табличным, аналитическим или графическим способами. Табличное описание работы RS -триггера, заданного схемой на рис.2 а), представлено в таблице 1 (таблица переходов) и таблице 2 (таблица функций возбуждения).

Таблица 1.- Таблица переходов

| Qt | Qt +1 | R | S |

| ´ | |||

| ´ |

Таблица 2.- Таблица функций возбуждения

| R | S | Qt +1 |

| Qt | ||

| - |

Обозначения в таблицах 1 и 2 были введены выше. Запрещенной является комбинация входных сигналов, вызывающая неопределенной состояние триггера. Эта комбинация для асинхронного триггера может быть выражена требованием RS = 0. Для удобства нахождения аналитического описания функционирования рассматриваемого триггера объединим таблицы 1 и 2 в одну таблицу 3, на основе которой составим карту Карно с целью минимизации характеристического уравнения.

Таблица 3. – Сводная таблица переходов и функций возбуждения

| Qt | R | S | Qt +1 | Примечания |

| Хранение 0 | ||||

| Установка 1 | ||||

| Нулевое состояние | ||||

| ´ | Неопределенное состояние | |||

| Хранение 1 | ||||

| Единичное состояние | ||||

| Установка 0 | ||||

| ´ | Неопределенное состояние |

Аналитическое описание (характеристическое уравнение) асинхронного RS -триггера можно получить из таблицы 3, доопределив в ней значения состояния Qt +1, соответствующие запрещенным комбинациям R и S,сначала единицами, а затем нулями. Для минимизации полученных функций воспользуемся соответствующими картами Карно (рис.4 а) и б)).

R

|

|  1 1

|   1 1

| |||

S

Рисунок 4 а). Карта Карно: доопределение запрещенных сигналов

единицами

R

0 0

|   1 1

| ||||

S

Рисунок 4 б). Карта Карно: доопределение запрещенных сигналов нулями

Склеивая минтермы поочередно, как показано на рис.4, мы получим соответственно два характеристических уравнения (1) и (2), описывающие работу асинхронного RS -триггера. Правая часть уравнения (1) выражена через штрих Шеффера, а правая часть уравнения (2) – через стрелку Пирса.

(1)

(1)

Уравнению (2) соответствует схема RS -триггера, изображенная на рис.4 а), а уравнению (2) – схема, изображенная на рис.4 б).

Заметим, что зависимость состояния Qt +1 на t + 1 такте работы триггера от состояния Qt на такте t характеризует свойство запоминания предшествующего состояния.

Описание работы рассматриваемого RS -триггера можно дополнить графом, изображенным на рис.5.

Рисунок 5. Графический способ описания работы асинхронного RS -триггера

На рис.5 видно, что схема, которая находилась в состоянии Q =0, сохраняет это состояние как при воздействии входного набора R =1, S =0, так и при воздействии набора R =0, S =0. Если же на вход схемы, находящейся в состоянии Q =0, подействовать набором R =0, S =1, то она переходит в состояние Q =1 и сохраняет его при входных наборах R =0, S =0, либо R =0, S =1 и т.д.

Рассмотрим теперь синхронный RS -триггер (рис.6). К входам S и R подключены конъюнкторы, с помощью которых обеспечивается передача активных уровней информационных входов S и R синхронного триггера на входы S и R входящего в его состав асинхронного триггера только при наличии уровня логической единицы на синхронизирующем входе С.

Рисунок 6. Схема синхронного RS -триггера

Таким образом, при С =0 на входы асинхронного триггера не передаются активные уровни и триггер сохраняет ранее установленное в нем состояние Qt. При C =1 состояние триггера определяется действующими на входах уровнями так же, как и в рассмотренном выше асинхронном RS -триггере.

Нормальная работа синхронного RS -триггера требует, чтобы за время действия логической единицы на синхронизирующем входе С уровни на информационных входах S и R оставались неизмененными. Смена уровней на входах допускается лишь в то время, когда С =0 и триггер не реагирует на уровни, действующие на входах S и R.

Приведем характеристики некоторых других, наиболее распространенных в системах интегральных логических элементов типов триггеров.

JK-триггеры являются универсальными триггерами, у которых входы J и K в отдельности реализуют раздельное управление и совместно-счетный режим. Триггер JK- типа имеет более сложную, по сравнению с RS -триггером, структуру и более широкие функциональные возможности. Помимо информационных входов J и K и прямого и инверсного выходов Q и  , JK -триггер имеет вход управления С (синхронизирующий, тактирующий или счетный вход), а также асинхронные установочные S и R -входы. Обычно активными уровнями установочных сигналов являются нули. Установочные входы имеют приоритет над остальными. Активный уровень сигнала на входе S устанавливает триггер в состояние Q =1, а активный уровень сигнала на входе R – в состояние Q =0 независимо от сигналов на остальных входах.

, JK -триггер имеет вход управления С (синхронизирующий, тактирующий или счетный вход), а также асинхронные установочные S и R -входы. Обычно активными уровнями установочных сигналов являются нули. Установочные входы имеют приоритет над остальными. Активный уровень сигнала на входе S устанавливает триггер в состояние Q =1, а активный уровень сигнала на входе R – в состояние Q =0 независимо от сигналов на остальных входах.

Если на входы установки одновременно подать пассивный уровень сигнала, то состояние триггера будет изменяться по фронту импульса на счетном входе в зависимости от состояния входов J и K, как показано в таблицах переходов (таблица 4) и функций возбуждения (таблица 5).

Таблица 4.- Таблица переходов Таблица 5.-Функции возбуждения

| J | K | Qt +1 |

| Qt | ||

t t

|

|

.

Полную таблицу истинности, описывающую функционирование JK -триггера, можно представить в виде (таблица 6):

Таблица 6.- Сводная таблица

| Qt | J | K | Qt +1 |

Из соответствующей карты Карно можно легко получить одно из характеристических уравнений JK -триггера:

или

или

Переведя эти уравнения в логический базис элементов, на которых строится JK -триггер, мы получим структурное уравнение триггера, определяющее конфигурацию его схемы.

JK -триггеры отличаются от RS -триггеров тем, что при значениях входной информации, запрещенной для RS -триггеров, они инвертируют хранимую в них информацию.

К универсальным триггерам с управляемым приемом информации по одному входу относятся D -триггеры. D -триггер имеет один информационный вход D. Информация с входа D заносится в триггер по положительному перепаду импульса на счетном входе C и сохраняется до следующего положительного перепада на входе C. Помимо счетного C и информационного D входов D -триггер снабжен асинхронными установочными R и S -входами. Установочные входы приоритетны. Они устанавливают D -триггер независимо от сигналов на входах C и D. Характеристическое уравнение D -триггера имеет вид Qt +1 = D. Это уравнение показывает, что состояние триггера на t+ 1 такте работы равно входному сигналу в момент, предшествующий тактовому перепаду сигнала C. Функциональная схема D -триггера может быть получена из схемы JK -триггера путем подключения входа K к входу J через инвертор D = J =