Вхідний контроль:

1 Чим відрізнюються паралельний і послідовний способи обміну даними у МПС?

2 Даними якої розмірності може обмінюватися МПС через послідовний порт RS -232- C?

3 Які службові символи можуть входити до складу інформації, яка передається через послідовний порт RS -232- C?

4 В чому полягає різниця поміж синхронним і асинхронним способами обміну інформацією?

5 В який спосіб слід зорганізовувати послідовний обмін інформацією поміж МПС, якщо в кожній з них інформацію подано у паралельному коді?

6 У яких випадках застосовується паралельний обмін даними поміж МПС та периферійними пристроями й чому?

7 У яких випадках дані поміж МПС та периферійними пристроями пересилаються у послідовному коді й чому?

8 Які послідовні адаптери та приймачі-передавачі Вам є відомі?

9 З яких бітів складається формат даних у послідовному адаптері

RS -232- С?

Асинхронний послідовний інтерфейс DUART – МС68681 фірми Motorola

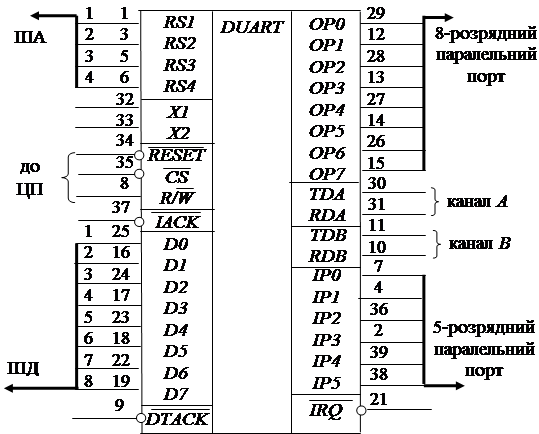

ВІС фірми Motorola МС 68681 (DUART – Dual asynchronous reseiver/transmitter) – подвійний асинхронний приймач-передавач, призначений для організації двох незалежних послідовних асинхронних дуплексних каналів обміну (А та В) із зовнішніми пристроями; також за його допомогою існує можливість організації обміну службовою інформацією через 6-розрядний паралельний порт приймання і 8-розрядний паралельний порт введення-виведення інформації.

DUART забезпечує такі можливості як:

– організація двох незалежних асинхронних дуплексних послідовних каналів введення-виведення;

– робота кожного з каналів на 18-ти фіксованих швидкостях обміну, які можуть програмуватися незалежно для кожного з каналів;

– робота з даними, довжина котрих може становити від 5 до 8 бітів даних;

– у повідомлення встановлюються стартовий і один-два стопових біти, додатково може використовуватися біт паритету;

– можуть вибиратися такі режими роботи каналів:

нормальний (повний дуплекс);

автоматичного ехо-сигналу;

місцева кільцева перевірка;

віддалена кільцева перевірка;

– робота в режимі селекторного виклику;

– багатофункціональний 16-розрядний лічильник/таймер може працювати у двох режимах:

формування часових інтервалів;

генерування імпульсів;

– 6-розрядний паралельний порт введення може слугувати за багатофункціональний пристрій введення інформації або використовувати чотири входи для вимірювання часових характеристик сигналів;

– багатофункціональний 8-розрядний паралельний порт введення-виведення дозволяє індивідуально виконувати встановлення інформації на кожному з розрядів і задавати режим роботи;

– порт забезпечує багатовекторну систему переривань (до восьми пристроїв);

– визначення помилок роботи (зупин лінії, фальшстарт, надходження переривання тощо);

– робота від внутрішнього генератора з кварцовим стабілізуванням частоти або від зовнішнього генератора імпульсів;

– ВІС є сумісна з ТТЛ-логікою;

– живлення від джерела +5 В.

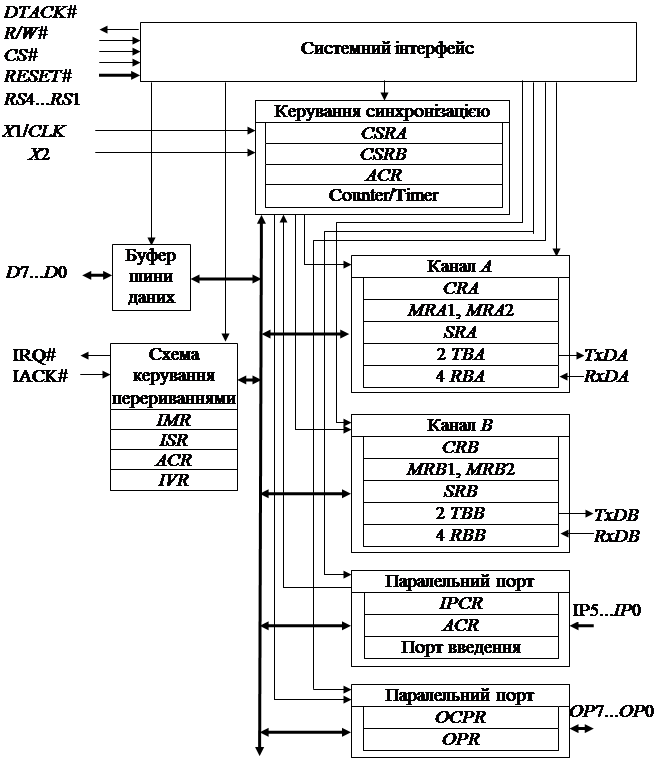

Структурну схему DUART наведено на рис. 11.13. До структурної схеми входять:

– системний інтерфейс – схема, яка забезпечує керування роботою вузлів DUART, а також керування обміном інформацією з ЦП. За допомогою цієї схеми проводиться обмін сигналами поміж ЦП і вузлами DUART. На схему надходять сигнали:

R/W# – читання /запис;

CS# – вибір мікросхеми, при надходженні цього сигналу ВІС переводиться до активного стану;

RESET# – сигнал скидання;

RS 4- RS 1 (Register Select) – відповідні розряди шини адреси, які визначають адресу внутрішнього вузла регістра DUART;

DTACK# – сигнал підтвердження готовності ВІС до обміну, підтверджує наявність інформації на шині даних;

– буфер шини даних – схема, котра забезпечує правильність обміну поміж шиною даних МПС і внутрішньою шиною DUART;

– схема керування перериваннями – забезпечує роботу за перериваннями. На її входи надходить сигнал IACK# – сигнал підтвердження переривання – і формується сигнал IRQ# – номер запиту на переривання. До схеми входять такі вузли:

IMR (Interrupt Mask Register) – регістр маски переривання;

ISR (Interrupt Status Register) – регістр стану переривання;

ACR (Auxiliary Control Register) – допоміжний регістр керування;

IVR (Interrupt Vector Register) – регістр вектора переривань;

Рисунок 11.13 – Структурна схема DUART

– схема керування синхронізацією. Схема визначає швидкість обміну інформацією у послідовних каналах. До її складу входять:

CSRA (Clock Select Register channel A) – регістр визначення швидкості обміну інформацією в каналі А;

CSRВ (Clock Select Register channel В) – регістр визначення швидкості обміну інформацією в каналі В;

ACR (Auxiliary Control Register) – допоміжний регістр контролю;

Counter/Timer – 16-розрядний лічильник/таймер, складається з двох 8-розрядних регістрів, кожен з яких програмується окремо;

– два аналогічних асинхронних послідовних канали – А і В, які побудовано з однакових вузлів:

CRA (B) (Command Register channel A (B)) – командний регістр, який керує виконанням команд;

MRA 1, MRA 2 (Mode Register 1, 2) – регістри, вміст котрих визначає режим роботи каналів введення-виведення даних;

SRA (B) (Status Register channel A (B)) – регістри стану, зберігають інформацію про результати обміну;

TBA (B) (Transmit Buffer channel A (B)) – буферні регістри передавача відповідного каналу, до їхнього складу входять два регістри: THRA (В) – регістр тимчасового зберігання передавача і TSRА (В) – регістр зсуву передавача;

RBA (B) (Receive Buffer channel A (B)) – буферні регістри приймача відповідного каналу. Кожний складається з чотирьох регістрів: трьох регістрів RHRA (В) – регістр тимчасового зберігання приймача, і RSRА (В) – регістр зсуву приймача;

– 6-розрядний паралельний порт введення. За необхідністю виводи каналу може бути запрограмовано на виконування певних допоміжних функцій обслуговування каналів зв’язку. До його складу входять:

IPCR (Input Port Change Register) – регістр стану порту введення. За відсутності сигналів перебуває у скинутому стані;

ACR (Auxiliary Control Register) – допоміжний регістр контролю;

порт (6-розрядний регістр) введення;

– 8-розрядний паралельний порт введення-виведення. Багатоцільовий універсальний порт. Усі розряди порту може бути індивідуально скинуто або встановлено. До його складу входять:

OPCR (Output Port Configuration Register) – регістр стану. Програмується задля визначення конфігурації паралельного порту (OP 7... OP 0) для поточного режиму роботи.

OPR (Output Port Register) – 8-розрядний паралельний порт.

Розподіл адресного простору DUART відбувається відповідно до табл. 11.6.

Кожен з двох каналів забезпечує роботу на 18-ти фіксованих швидкостях від внутрішнього генератора, частота котрого визначається кварцовим стабілізатором, який має частоту 3,6864 МГц, або від зовнішнього генератора, сигнал з котрого надходить на вивід Х 1/ CLK. Взаємозв’язок швидкості й частот зовнішнього генератора наведено в табл. 11.7.

Таблиця 11.6 – Розподіл адресного простору DUART

| RS 4 | RS 3 | RS 2 | RS 1 | Читання (R/W = 1) | Запис (R/W = 0) | |

| Mode Register А (MRA 1, 2) | Mode Register А (MRA 1, 2) | |||||

| Status Register A (SRA) | Clock Select Register (CSRA) | |||||

| Не використовується | Command Register А (CRA) | |||||

| Receive Buffer (RBA) | Transmit Buffer А (TBA) | |||||

| Input Port Change Register (IPCR) | Auxiliary Control Register (ACR) | |||||

| Interrupt Status Register (ISR) | Interrupt Mask Register (IMR) | |||||

| Старший байт лічильника/таймера | Старший байт лічильника/таймера | |||||

| Молодший байт лічильника/таймера | Молодший байт лічильника/таймера | |||||

| Mode Register В (MRВ 1,2) | Mode Register В (MRВ 1,2) | |||||

| Status Register В (SRВ) | Clock Select Register (CSRВ) | |||||

| Не використовується | (Command Register B (CRВ) | |||||

| Receive Buffer В (RBВ) | Transmit Buffer В (TBA) | |||||

| Interrupt Vector Register (IVR) | Interrupt Vector Register (IVR) | |||||

| Порт введення | Output Port Configuration Register (OPCR) | |||||

| Старт лічби | Output Port Register | Встановлення біта | ||||

| Стоп лічби | Скидання біта |

Таблиця 11.7 – Відповідність швидкості й частоти зовнішнього генератора

| Швидкість, Бод | Частота зовнішнього генератора, кГц | Швидкість, Бод | Частота зовнішнього генератора, кГц |

| 0,8 | 19,2 | ||

| 1,2 | 28,8 | ||

| 1,759 | 32,056 | ||

| 134,5 | 2,153 | 38,4 | |

| 2,4 | 76,8 | ||

| 3,2 | 115,2 | ||

| 4,8 | 153,6 | ||

| 9,6 | 19,2 кБод | 307,2 | |

| 16,756 | 38,4 кБод | 614,4 |

Програмування ВІС DUART здійснюється за допомогою запису сигналів керування (байтів) до відповідних регістрів.

Керування роботою каналів А і В здійснюється за допомогою вмісту регістрів MRA 1, MRA 2 (MRВ 1, MRВ 2). Призначення бітів регістра MRA 1 (MRВ 1) подано в табл. 11.8.

Програмування регістрів MRA 2 та MRВ 2 задля визначання режиму роботи каналу здійснюється відповідно до табл. 11.9.

Вибір необхідної швидкості роботи передавача та приймача здійснюється завантаженням до регістрів CSRA та CSRВ байта, вміст котрого формується відповідно до табл. 11.10. За коду 1111 для синхронізації використовуються виводи ІР 3 або ІР 4 паралельного порту введення.

Вміст регістрів команд CRA (B) керує виконуванням програми функціонування ВІС DUART. Його програмування наведено у табл. 11.11.

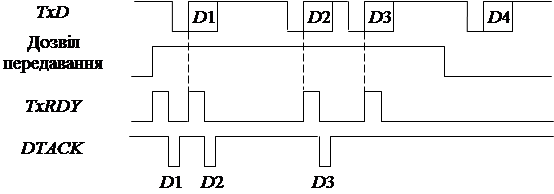

Передавачі каналів А і В програмуються відповідно до наведених таблиць перед початком передавання інформації. Про готовність до передавання повідомляється встановленням біта 2 у регістрі статусу (SRA (B)). Цей біт також може використовуватися задля генерації запиту на переривання для каналу А на виводі ОР 6 паралельного порту або ОР 7 – для каналу В. Передавання дозволяється встановленням біта 2 і скиданням біта 3 у командному регістрі CRA (B).

Передавання інформації розпочинається з її завантаження до буферного регістра передавача ТВА (В), звідки вона передається до регістра зсуву TSRA (B). В цьому регістрі здійснюється її перетворювання на послідовний код, формування стартового біта і передавання інформації до каналу. Завершується передавання формуванням необов’язкового біта парності та обов’язкових одного чи двох стопових бітів. Передавання розпочинається за зрізом сигналу у каналі TxD, що встановлює значення сигналу TxRDY у 1. Скидання цього сигналу буде відбуватися після завантаження до буфера передавання нової інформації, що призводить до формування імпульсу сигналу  , котрий дозволяє передавання інформації. Після проходження стопового біта лінія залишається у стані логічної 1, якщо немає наступного байта. Скидання бітів 2 і 3 командного регістра CRA (B) є забороною передавання; при цьому сигнали TxRDY та

, котрий дозволяє передавання інформації. Після проходження стопового біта лінія залишається у стані логічної 1, якщо немає наступного байта. Скидання бітів 2 і 3 командного регістра CRA (B) є забороною передавання; при цьому сигнали TxRDY та  не формуються і інформація D 4 не передається.

не формуються і інформація D 4 не передається.

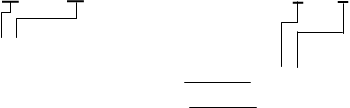

Передавання інформації подано за допомогою часових діаграм, які наведено на рис. 11.14.

Про готовність до приймання інформації повідомляється встановлЯнням біта 0 в регістрі статусу (SRA (B)). Приймачі відповідних каналів розпочинають працювати при надходженні на вхід зрізу вхідного сигналу і визначають тривалість одного біта. Тривалість біта визначається кількістю імпульсів тактової частоти від зрізу до першого фронту вхідного сигналу. Зазвичай тривалість біта становить 7,5 періодів тактової частоти; якщо таке не виконується, подальша інформація ігнорується і приймач продовжує

Таблиця 11.8 – Програмування режиму роботи каналів регістрів MRA 1 (MRВ 1)

| Контроль RxRTS | Вибір RxIRQ # | Помилка | Перевірка парності | Тип перевірки | Довжина повідомлен- ня | ||||

| біт 7 | біт 6 | біт 5 | біт 4 | біт 3 | біт 2 | біт 1 | біт 0 | ||

| 0 – не дозволено 1 – дозволено | 0 – RxRDY 1 – повний канал FIFO | 0 – обнулення 1 – блокування |

| З перевіркою 0 – дорівнює 1 – не дорівнює – Адреси/дані 0 – дані 1– адреси | |||||

| 0 0 | Перевірка парності | ||||||||

| 0 1 | – | 0 0 – 5 біт 0 1 – 6 біт 1 0 – 7 біт 1 1 – 8 біт | |||||||

| 1 0 | Немає перевірки | ||||||||

| 1 1 | Біти використо-вуються як адреси/дані | ||||||||

Таблиця 11.9 – Програмування режиму роботи каналів регістрів MRA 2 (MRВ 2)

| Режим роботи каналу | Контроль ТxRTS (вивід ОР 0) | СТS дозвіл передавання | Кількість стопових бітів | |||||

| біт 7 | біт 6 | біт 5 | біт 4 | біт 3 | біт 2 | біт 1 | біт 0 | |

| 0 – не дозволено 1 – дозволено | 0 – не дозволено 1 – дозволено | 6-8 5 бітів бітів даних даних 0000 – 0,563 1,063 0001 – 0,625 1,125 0010 – 0,688 1,188 0011 – 0,750 1,250 0100 – 0,813 1,313 0101 – 0,875 1,375 0110 – 0,938 1,438 0111 – 1,000 1,500 1000 – 1,563 1,563 1001 – 1,625 1,625 1010 – 1,688 1,688 1011 – 1,750 1,750 1100 – 1,813 1,813 1101 – 1,875 1, 875 1110 – 1,938 1,938 1111 – 2,000 2,000 | |||||

| 0 0 0 1 1 0 1 1 | Нормальний Автоматичного ехо-сигналу Місцева кільцева перевірка Віддалена кільцева перевірка | |||||||

Таблиця 11.10 – Програмування швидкості обміну DUART

| Вибір швидкості приймача | Вибір швидкості передавача | ||||||||||||||

| Біт 7 | Біт 6 | Біт 5 | Біт 4 | Біт 3 | Біт 2 | Біт 1 | Біт 0 | ||||||||

| |||||||||||||||

| Швидкість, Бод залежно від ACR | Швидкість, Бод залежно від ACR | ||||||||||||||

| Біт 7 = 0 | Біт 7 = 1 | Біт 7 = 0 | Біт 7 = 1 | ||||||||||||

| 134,5 | 134,5 | 134,5 | 134,5 | ||||||||||||

| 19,2 кБод | 19,2 кБод | ||||||||||||||

| 38,4 кБод | 19,2 кБод | 38,4 кБод | 19,2 кБод | ||||||||||||

| Таймер | Таймер | Таймер | Таймер | ||||||||||||

| Зовн. сигн. | Зовн. сигн. | Зовн. сигн. | Зовн. сигн. | ||||||||||||

| Зовн. сигн. | Зовн. сигн. | Зовн. сигн. | Зовн. сигн. | ||||||||||||

Таблиця 11.11 – Програмування командного регістра CRA(B)

| Різні команди | Команди передавача | Команди приймача | |||||

| Біт 7 | Біт 6 | Біт 5 | Біт 4 | Біт 3 | Біт 2 | Біт 1 | Біт 0 |

|

|

| |||||

| 000 – Команди немає 001 – Скидання режиму 010 – Скидання приймача 011 – Скидання передавача 100 – Скидання статусу помилок 101 – Скидання канальних переривань 110 – Зупин 111 – Скидання зупину | 00 – Не виконуються активні дії. Зберігається поточний стан режимів | 00 – Не виконуються активні дії. Зберігається поточний стан режимів | |||||

| 01 – Передавання дозволено | 01 – Приймання дозволено | ||||||

| 10 – Передавання заборонено | 10 – Приймання заборонено | ||||||

| 11 – Не використовується | 11 – Не використовується | ||||||

|

Рисунок 11.14 – Передавання інформації послідовним каналом

контролювати надходження імпульсів на його вхід. Якщо часові співвідношення виконуються, то приймач записує дані до буфера приймача RHR і скидає біт 0 у регістрі статусу (SRA (B)). Якщо віднайдено помилку кадрової синхронізації (відсутність стопового біта), то у лінії зберігається нульовий (L 0) стан упродовж половини періоду тривалості біта, після чого робота триває так само, як і після отримання стартового біта.

Поява інших помилок (парності, зміна швидкості надходження інформації тощо) змінює значення відповідних прапорців (ознак) у регістрах статусу (SRA (B)).

Після завершення приймання байта на лінії повинен встановлюватися високій рівень сигналу (L 1) тривалістю не менш за половину періоду тривалості біта, після чого порт продовжує пошук наступного стартового біта.

Функціонування DUART у режимах контролю забезпечується встановленням бітів 7, 6 у регістрі режиму роботи каналів MRA 2 (MRВ 2) відповідно до табл. 11.8.

В режимі автоматичного ехо-сигналу (код бітів 7, 6,..., 1) в каналі автоматично ретранслюються дані. Місцевий зв’язок поміж центральним процесором і приймачем продовжує нормально функціонувати, а зв’язок поміж центральним процесором і передавачем заблоковано. В такий спосіб можна контролювати стан лінії і роботу робочої станції.

В режимі місцевої кільцевої перевірки (код – 10) вихід передавача у ВІС з’єднується з входом приймача. Передавач і приймач в цьому режимі працюють відповідно до встановлених режимів у штатному розписі. Передаючи дані і контролюючи їхнє приймання, можна перевірити правильність роботи місцевого каналу приймання-передавання DUART.

В режимі віддаленої кільцевої перевірки каналом автоматично ретранслюються дані і канал передавача робочої станції сполучено з іншими станціями мережі (дозволено до 256 інших станцій). При цьому місцевий зв’язок поміж центральним процесором і приймачем заблоковано. До складу даних, що передаються, входять стартовий біт, блок даних, біт адреси/даних (A/D) і стопові біти. Цей блок призначено одній зі станцій. Станції мережі невпинно здійснюють моніторинг каналу й ідентифікують біт адреси/даних задля визначення виду інформації. Якщо біт A/D встановлено, то передається адреса, якщо скинуто – дані. Станція визначає власну адресу, сповіщає про це головну станцію, яка вмикає власний приймач, і генерує переривання, після чого отримується повідомлення, і знову заблоковує власний канал.

Багатофункціональний 16-розрядний лічильник/таймер може працювати в режимі формування часових інтервалів і в режимі генерування імпульсів. В кожному з режимів лічильник/таймер можна запрограмувати на отримання сигналу тактової частоти від кількох джерел і виведення результату через вивід ОР 3 паралельного порту. До лічильника можна завантажити число від $0002 до $ FFFF, котре можна змінити будь-якого моменту. Програмування здійснюється завантаженням до допоміжного регістра керування (ACR) байта, що відповідає потрібному режимові роботи. Формат цього регістра наведено у табл. 11.12. Біт 7 цього регістра визначає швидкість обміну інформацією відповідно до табл. 11.6. В режимі формування часових інтервалів лічильник/таймер запускається і зупиняється ЦП, тому цей режим можна використовувати як системний годинник реального часу задля генерування переривань і як вартовий пристрій. В режимі генерування імпульсів лічильник/таймер працює невпинно незалежно від ЦП, тому такий режим можна використовувати задля програмної реалізації сигналів тактової частоти для каналів А і В, періодичного звернення до певних пристроїв і в якості автогенератора періодичних імпульсних сигналів.

В режимі формування часових інтервалів лічильник/таймер працює як лічильник, який декрементує попередньо завантажений вміст лічильника. За сигнал тактової частоти може слугувати сигнал від зовнішнього генератора, який надходить на вхід X 1/ CLK, поділений на 16, або сигнал зі входу ІР 2. Після програмування і запуску лічильник/таймер розпочинає працювати від значень попереднього завантаження до досягнення значення $0000, після чого встановлює прапорець у біті 3 регістра ISR і продовжує лічбу від значення $ FFFF. Задля перевантаження лічильник/таймер потрібно заново зініціалізувати.

В режимі генерування імпульсів таймер формує періодичну послідовність прямокутних імпульсів, частота слідування котрих визначається значеннями попередніх завантажень і сигналом, який надходить від джерел: внутрішній кварцовий генератор; зовнішній сигнал на виводі Х 1/ СLK або сигнал на цьому виводі, частота котрого поділена на 16; зовнішній сигнал, що надходить на вивід ІР З2. Таймер виконує лічбу до досягнення значення $0000, після чого перевантажує значення попередніх завантажень і продовжує роботу.

Таблиця 11.12 – Програмування режиму роботи таймера

| Вибір швид-кості | Програмування режиму і джерела сигналу | Виводи запитів переривання | |||||||

| IP 3 IRQ | IP 2 IRQ | IP 1 IRQ | IP 0 IRQ | ||||||

| Біт 7 | Біт 6 | Біт 5 | Біт 4 | Біт 3 | Біт 2 | Біт 1 | Біт 0 | ||

| 0 – дозвіл, 1 – заборона | 0 – дозвіл, 1 – заборона | 0 – дозвіл, 1 – заборона | 0 – дозвіл, 1 – заборона | |||||

| 0 або1 (табл. 11.5 | |||||||||

| Режим Джерело часових сигналів | |||||||||

| 000 – лічильник | зовнішній IP2 | ||||||||

| 001 – лічильник | TxCA – 1 X визначення часових інтервалів каналу передавача А | ||||||||

| 010 – лічильник | TxCВ – 1 X визначення часових інтервалів каналу передавача В | ||||||||

| 011 – лічильник | кварцовий резонатор або зовнішній сигнал (Х 1/ СLK), поділений на 16 | ||||||||

| 100 – таймер | зовнішній IP 2 | ||||||||

| 101 – таймер | зовнішній IP 2 | ||||||||

| 110 – таймер | кварцовий резонатор або зовнішній сигнал (Х 1/ СLK) | ||||||||

| 111 – таймер | кварцовий резонатор або зовнішній сигнал (Х 1/ СLK), поділений на 16 | ||||||||

Нижче наведено фрагмент програми роботи послідовного порту DUART задля передавання байта зі швидкістю 300 Бод каналом А:

MOVEА.L #$В00000,A0; Завантаження базової адреси DUART у А0

MOVE.B #$07,(A0); Завантаження до регістра режиму порту А

; MR2A даного $07 (00000111) для

; встановляння нормального режиму

; передавання з одним стоповим бітом

MOVE.B #$44,($01,A0); Завантаження до регістра визначання

; швидкості обміну інформацією у каналі А

; даного $44 (01000100) для забезпечення

; швидкості 300 Бод

MOVE.B #$34,($02,A0); Завантаження до регістра команд каналу А

; даного $34 (01010101), яке перевантажує

; передавач

MOVE.B #$A5,($03,A0); Завантаження до буферного регістра

; передавача каналу А даного $А5 (10100101),

; яке є інформацією, котру буде передано

; каналом А

MOVE.B ($03,A0),($0Е,A0); Передавання інформації каналом А

Підмикання ВІС DUART до шин МПС здійснюється відповідно до функціонального призначення виводів мікросхеми та сигналів, що формуються іншими пристроями. Умовні графічні позначення та схему підключення асинхронного послідовного порту DUART подано на рис. 11.15. Збільшення кількості послідовних портів здійснюється при дешифруванні сигналів адреси. Кожна з ВІС DUART займає адресний простір 32 байти. Отже, для адресування наступних ВІС можна використовувати розряди А 5 і наступні.

|

Рисунок 11.15 – Схема підключення ВІС DUART

Контрольні питання:

1 Які функціональні можливості має ВІС DUART?

2 Які пристрої входять до складу ВІС DUART?

3 Який обсяг пам’яті відведено для адресування блоків ВІС DUART?

4 У яких режимах може працювати блок приймача-передавача ВІС DUART?

5 Скільки дуплексних каналів можливо зорганізувати за допомогою однієї ВІС DUART?

6 Для чого можуть використовуватися виводи порту ІР 0... ІР 5?

Контрольні питання підвищеної складності:

1 Для чого призначено режим автоматичного ехо-сигналу?

2 У яких режимах може працювати 16-розрядний лічильник/таймер?

3 У який спосіб програмується швидкість обміну інформацією ВІС DUART?

4 Чи існує можливість перевірки працездатності тракту приймача-передавача без наявності абонента?

5 Скільки окремих швидкостей обміну можна зреалізовувати за допомогою ВІС DUART?

Периферійний інтерфейс/таймер (PIT) МС68230 фірми Motorola

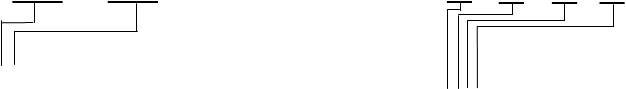

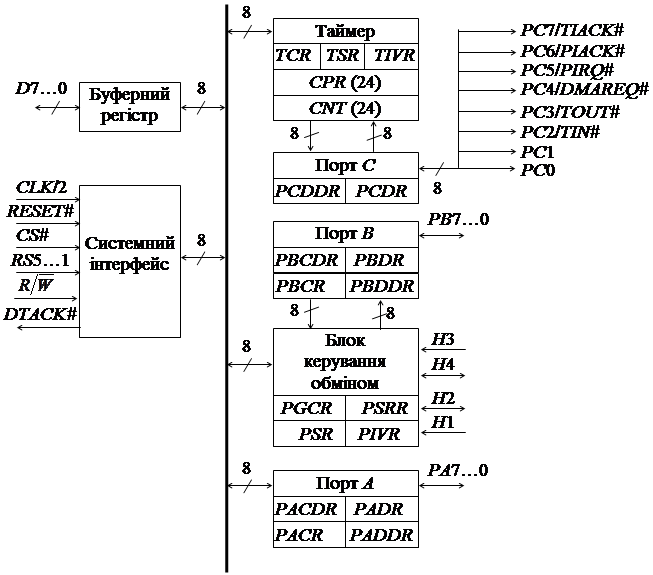

ВIC PI/T є паралельний інтерфейс/таймер, призначений для обміну 8-розрядними даними поміж мікропроцесором та зовнішніми пристроями (датчиками, пристроями керування тощо). Структурну схему PI/T наведено на рис. 11.16.

ВIC PI/T є паралельний інтерфейс/таймер, призначений для обміну 8-розрядними даними поміж мікропроцесором та зовнішніми пристроями (датчиками, пристроями керування тощо). Структурну схему PI/T наведено на рис. 11.16.

Рисунок 11.16 – Структурна схема РІ/Т

PI/T складається з блоків, які забезпечують зв’язок з мікропроцесором (буферний регістр, системний інтерфейс), і блоків, які обслуговують зовнішні пристрої (8-розрядні порти А, В, С, 24-розрядний таймер, блок керування обміном, який може використовуватись pfдля реалізації переривань, паралельного введення-виведення даних або формування сигналів квитування при пересиланні даних через порти А, В). Виводи РС 7... РС 2 можуть програмуватись для передавання сигналів таймера TIN #, TOUT #, переривання PIRQ #, PIACK #, TIACK, запиту прямого доступу DMAREQ #. Зв’язок PI/T з МП зреалізовується шляхом обміну даними по виводах D 7… D 0 у циклі читання або запису. МП видає на вхід системного інтерфейсу сигнал R/  , а PI/T видає сигнал підтвердження готовності DTACK #.

, а PI/T видає сигнал підтвердження готовності DTACK #.

Дані зчитуються або записуються до одного з регістрів таймера, порту А, В, С або блока керування обміном. Вибір регістра визначається кодом адреси, який надходить на входи адреси RS 5… RS 1. В адресному просторі PI/T займає 32-байтові комірки, з яких 23 зайнято регістрами, а решта не використовуються. Всі регістри, окрім лічильника CNT та регістра попереднього встановляння лічильника CPR, які мають 24 розряди, є 8-розрядні і адресуються як байт. CNT та CPR адресуються як три окремих 8-розрядні регістри. У табл. 11.13 показано адреси регістрів PI/T та зазначено зміщення відносно базової адреси $800001, які використовуються у команді MOVEP для формування ефективної адреси регістрів PI/T.

При зверненні до PI/T на входи RS 5... RS 1 надходить адреса регістра, що її формує МП, а на вхід вибирання CS # подається сигнал CS # від адресного дешифратора, який визначає саме цей PI/T серед усіх, які входять до МПС. На вхід CLK надходять синхросигнали CLK /2, а на вхід RESEТ # – загальний для всієї системи сигнал скидання.

PI/T є програмована ВІС, до керувальних регістрів якої задля реалізації різних режимів роботи треба записати керувальні коди, тобто зініціалізувати її.

Порти А та В забезпечують паралельний обмін даними поміж МП та зовнішніми пристроями. Задля виведення даних МП записує їх до регістра даних відповідного порту: PADR або PBDR, а введення здійснюється шляхом їхнього зчитування з регістрів даних. Кожний вивід портів А та В може програмуватись окремо на введення або виведення встановлянням у 1 (виведення) або у 0 (введення) бітів відповідного регістра – PADDR або PBDDR. Порти мають також додаткові регістри даних – PАСDR та PBСDR, які дозволяють зберігати дані, якщо необхідно ввести від зовнішнього пристрою наступний біт до того, як попередній було зчитано мікропроцесором, або вивести наступний біт з мікропроцесора до того, як попередній біт було прийнято зовнішнім пристроєм. Отже, PACDR та PBCDR слугують за буферні регістри.

Блок керування обміном здійснює загальне керування портами А та В, а також керування функціями виводів Н 3... Н 1. При ініціалізації портів А та В до регістрів PGCR, PSRR блока керування, регістрів PACR, PADDR та PBCR, PBDDR портів МП записує керувальні коди, які визначають їхнє функціонування.

Таблиця 11.13 – Адреси регістрів PI/T

| Назва регістра | Призначення регістра | Адреса | Зміщення |

| PGCR | Головний регістр керування | $800001 | $00 |

| PSRR | Регістр обслуговування переривань | $800003 | $02 |

| PADDR | Регістр напрямку обміну даними порту А | $800005 | $04 |

| PBDDR | Регістр напрямку обміну даними порту В | $800007 | $06 |

| PCDDR | Регістр напрямку обміну даними порту С | $800009 | $08 |

| PIVR | Регістр вектора переривань | $80000 В | $0 A |

| PACR | Регістр керування порту А | $80000 D | $0 C |

| PBCR | Регістр керування порту В | $80000 F | $0 E |

| PADR | Регістр даних порту А | $8000011 | $10 |

| PBDR | Регістр даних порту В | $8000013 | $12 |

| PAAR | Додатковий регістр даних порту А | $8000015 | $14 |

| PBAR | Додатковий регістр даних порту В | $8000017 | $16 |

| PCDR | Регістр даних порту С | $8000019 | $18 |

| PSR | Регістр стану PI/T | $800001 B | $1 A |

| TCR | Регістр керування таймером | $8000021 | $20 |

| TIVR | Регістр вектора переривань таймера | $8000023 | $22 |

| CPRH | Регістр попереднього встановляння старшого байта лічильника | $8000027 | $26 |

| CPRM | Регістр попереднього встановляння середнього байта лічильника | $8000029 | $28 |

| CPRL | Регістр попереднього встановляння молодшого байта лічильника | $800002 B | $2 A |

| CNTRH | Регістр старшого байта лічильника | $800002 F | $2 E |

| CNTRM | Регістр середнього байта лічильника | $8000031 | $30 |

| CNTRL | Регістр молодшого байта лічильника | $8000033 | $32 |

| TSR | Регістр стану таймера | $8000035 | $34 |

Фрагмент програми демонструє керування виведенням даних PI/T:

MOVEА.L #$800001,A0; Завантаження базової адреси PI/T до А0

MOVE.B #0,($0С,A0); Завантаження до регістра керування порту А РАCR

; 0 задля встановляння нульового режиму

MOVE.B #$FF,(4,A0); Завантаження до регістра напрямку обміну даними

; порту А даного $FF задля забезпечення виведення

; по всіх розрядах

MOVE.B #$55,($0,A0); Завантаження до регістра даних порту А даного

; $55 (01010101)

JSR.B *+12; Звернення до підпрограми затримки

BRA.B *-16; Циклування програми

MOVE.L #1000000,D0; Завантаження лічильника підпрограми затримки

SUBQ.L #1,D0; Декрементування лічильника

BNE.B *-2; Організація підпрограми затримки на 1 с

RTS; Повернення з підпрограми затримки

Наведений фрагмент програми є драйвер виведення PI/Т.

Фрагмент драйвера введення наведено нижче:

MOVE.B $800015.L,D0; Введення молодшого байта даного з додаткового

; регістра порту А PADR до регістра D0

За бажання ввести до регістра D 0 слова з портів А та В можна застосовувати команду MOVEP, яка виконується тільки з непрямою регістровою адресацією:

MOVEA.L $800001,A5

.

.

.

MOVEP ($14,A5),D0

За командою MOVEP біти D 15... D 8 з додаткового регістра порту А пересилаються до першого байта регістра D 0, а біти D 7... D 0 пересилаються з додаткового регістра порту В до нульового байта регістра D 0.

Виводи H 3... H 1 може бути запрограмовано на виконування функцій входів на запит переривання, входів-виходів даних або передавання сигналів квитування при обміні даними через порти А, В. Якщо виводи H 3 та H 1 використовуються для введення даних, то поточні сигнали на цих виводах дублюються у чотирьох розрядах регістра стану PSR. Для виведення даних використовуються виводи H 2 та H 4, значення даних на них встановлюються відповідно до вмісту певних розрядів регістра PSR. Через читання або запис вмісту PSR мікропроцесор керує введенням або виведенням даних.

Порти А, В можуть програмуватись для реалізації чотирьох різних режимів обміну.

Режим 0 – односпрямований обмін 8-розрядними даними через окремі порти А і В. Напрямок обміну для кожного виводу задається вмістом регістрів PADDR та PBDDR. Виводи H 1 і H 2 можуть використовуватись для квитування передавання через порт А, а виводи H 3 і H 4 – для квитування передавання через порт В. При введенні даних до відповідного порту сигнали H 1 і H 3 вказують на надходження даних від зовнішнього пристрою, при виведенні даних – на їхнє приймання зовнішнім пристроєм. Сигнали H 2 і H 4 при введенні підтверджують отримання даних від зовнішніх пристроїв, а при виведенні слугують за запити на приймання даних зовнішніми пристроями.

Режим 1 – односпрямований обмін 16-розрядними даними через подвійний порт А-В. Для квитування обміну використовуються сигнали на виводах H 3, H 4, функціональне призначення яких при введенні та виведенні даних є таке ж саме, як і в режимі 0. Виводи H 1 та H 2 використовуються для введення-виведення даних або для подавання запитів на переривання.

Режим 2 – двоспрямований обмін 8-розрядними даними через порт В. Виводи H 1 та H 2 слугують для квитування виведення даних до зовнішнього пристрою, виводи H 3 та H 4 – для квитування введення даних до порту В. Порт А у цьому режимі використовується для односпрямованого обміну даними без квитування.

Режим 3 – двоспрямований обмін 16-розрядними даними, які зчитуються мікропроцесором через подвійний порт А-В. Виводи H 1 та H 2 слугують для квитування виведення даних до зовнішнього пристрою, а виводи H 3 та H 4 – для квитування введення даних до порту.

Порт С може використовуватись для обміну 8-розрядними даними, які записуються або зчитуються мікропроцесором через регістр PCDR. Обмін використовується без квитування. Напрямок передавання даних для кожного виводу PCi задається відповідним розрядом вмісту регістра PCDDR, який вводиться до нього у перебігу ініціалізації порту С. Виводи РС 2, РС 3, РС 7 може бути запрограмовано для обслуговування таймера, виводи РС 5, РС 6 – для запиту на переривання та приймання підтвердження переривання від мікропроцесора. Вивід РС 4 може використовуватись для формування запиту на прямий доступ до пам’яті.

Якщо виводи H 3... H 1 або частина з них програмується для роботи на приймання запитів на переривання за ініціалізації блока керування обміном, то надходження на них запиту зумовлює формування сигналу PIRQ # = 0 на виводі РС 5 порту С. Цей сигнал подається на вхід пріоритетного шифратора PRCD, який формує відповідний код запиту на переривання IPL 2... IPL 0, який подається на мікропроцесор. Коли мікропроцесор переходить до обслуговування цього запиту, він видає сигнал підтвердження, який надходить на вхід PIACK # – вивід РС 6. Мікропроцесор формує адресу регістра векторів переривань PIVR і зчитує вектор при зверненні до таблиці переривань для адресування підпрограми обслуговування цього переривання. Кожному запитові Hi відповідає свій вектор переривань. Старші шість розрядів цього вектора записуються до регістра PIVR PI/T у перебігу ініціалізації, а два молодших розряди відповідають номерові входу Hi, на який надійшов запит. Пріоритети запитів від зовнішніх пристроїв і порядок їхнього обслуговування визначаються вмістом регістра PSSR PI/T, який завантажується у перебігу ініціалізації.

Таймер, який входить до складу PI/T, зреалізовано на базі 24-розрядного лічильника CNT, який працює на віднімання. Початковий стан лічильника встановлюється за ініціалізації через запис 3-х байтів до регістра попереднього встановляння CPR. Запуск таймера здійснюється через запис до регістра керування таймером TCR керувального коду, який визначає також режим його функціонування. Сигнали на CNT можуть надходити як від генератора синхроімпульсів CLK, так і від зовнішніх пристроїв на вхід TIN # (вивід PC 2).

У режимі лічби імпульсів CLK таймер через інтервали часу, які визначаються вмістом CPR, формують сигнали на виході TOUT # (вивід PC 3). У режимі лічби подій (лічба сигналів на вході TIN #) поточний вміст CNT вказує на кількість імпульсів, що надійшли. Також можна запрограмувати ділення частоти вхідних імпульсів на 32.

У режимі лічби синхроімпульсів сигнал на вході TIN # слугує для запуску (TIN # = 1) або зупину (TIN # = 0) лічильника. Сигнал на виході таймера ТОUT # (вивід РС 3) має початкове значення ТОUT # = 1 і змінює своє значення, коли вміст лічильника дорівнює 0. Після цього лічильник може відновити початкове значення і повторити лічбу або завантажити нове значення з регістра CPR. Коли стан лічильника стає нульовим, у регістрі TSR встановлюється значення біта ZDS = 1 (прапорець нуля). Поточний стан таймера контролюється мікропроцесором через зчитування та аналіз вмісту регістра TSR.

При роботі таймера на виході ТОUT # формуються прямокутні імпульси, які можуть використовуватись для керування зовнішніми пристроями (періодичне включення-виключення, синхронізація тощо). Сигнал ТОUT може подаватися на вхід приорітетного шифратора як сигнал запиту для переривання для мікропроцесора. Сигнал підтвердження переривання надходить на вхід TIACK (вивід РС 7). Для зчитування вектора переривання мікропроцесор звертається до регістра TIVR, до якого цей вектор записується за ініціалізації таймера.

Таймери використовуються у вартових пристроях, для затримки сигналів, для запуску підпрограм у задані моменти часу тощо.

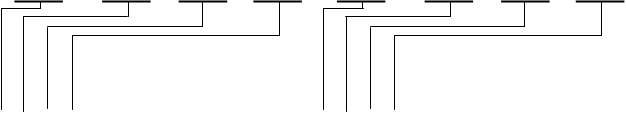

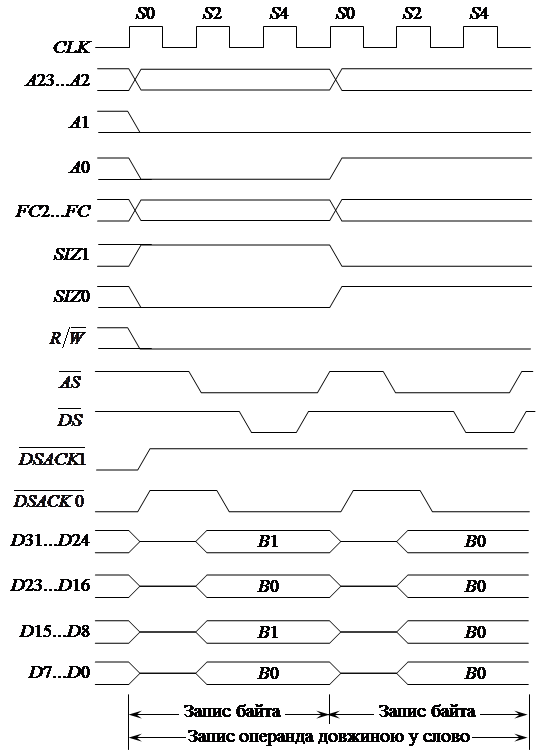

На рис. 11.17 подано часові діаграми передавання слова через 8-розрядний інтерфейс РІ/Т. Сигнали SIZ 1, SIZ 0 мають відповідно значення 10...2 байти в перебігу першого циклу і 1 байт (значення 01) – в перебігу другого циклу. Сигнали DSACK 1# та DSACK 0#, які вказують на готовність порту до роботи в кожному циклі, мають значення 11 в перебігу очікування і 10 (1 байт) – у кожному з циклів передавання даних до РІ/Т.

Контрольні питання:

1 Які функції можна зреалізовувати на ВІС PI/T?

2 Які пристрої входять до складу ВІС PI/T?

3 Скільки регістрів може бути адресовано до ВІС PI/T?

4 У скількох режимах роботи може працювати ВІС PI/T і чим вони відрізнюються один від одного?

5 Поясніть термін – обмін інформацією з квитуванням.

6 Для чого використовуються виводи Н 1... Н 4 в різних режимах роботи?

7 У яких режимах може працювати таймер ВІС PI/T?

8 Які виводи ВІС PI/T використовує таймер?

Контрольні питання підвищеної складності:

1 Чи можна використовувати ВІС PI/T для обміну словами?

2 Проілюструйте за допомогою часових діаграм процес передавання слова.

Рисунок 11.17 – Часові діаграми передавання слова через 8-розрядний інтерфейс РІ/Т

11.3 32-розрядні мікропроцесори сімейства М 680 ХХ фірми Motorola

Вхідний контроль:

1 Яку назву мають регістри загального призначення МП фірми Intel?

2 Чи закріплено згадані у п. 1 регістри за умовчанням за певними функціями?

3 Що таке сегментування пам’яті і в яких МП воно використовується?

4 З якою метою пам’ять поділяється на сегменти?

5 Чи є сумісні різні моделі універсальних МП фірми Intel і, якщо так, то як цього досягають?

6 Розпочинаючи з якої моделі МП фірми Intel використовують конвеєр команд?

7 Розпочинаючи з якої моделі МП фірми Intel використовують кеш-пам’ять?

32-розрядні універсальні мікропроцесори фірми Motorola МС 68020, МС 68030, МС 68040, МС 68060 побудовано на підставі базової моделі МС 68000. Їхньою характерною особливістю є наявність засобів, які забезпечують їхню спільну роботу з співпроцесорами задля обробки чисел з плаваючою точкою. Розпочинаючи з моделей МС 68040, 32-розрядні процесори побудовано за гарвардською архітектурою з розділенням потоків даних та команд; кеш-пам’ять є багаторівневою; є апаратна підтримка реалізації мультипроцесорних систем; введено внутрішні засоби самотестування та налагодження. МП МС 68060 має суперскалярну структуру з паралельною роботою двох виконавчих пристроїв обробки цілочисельних операндів і одного пристрою обробки операндів з плаваючою точкою. На базі моделі МС68020 розроблено сімейство спеціалізованих комунікаційних контролерів М 683 ХХ.

32-розрядні МП МС 680 Х 0 сумісні програмно “знизу догори” і мають ту ж саму програмну модель користувача, що й базова модель МП МС 68000.

МП МС 68020 зреалізовує розширений набір команд та способів адресування, які стали базовими для всіх наступних моделей сімейства, має внутрішню кеш-пам’ять команд на 256 байт і передбачає підключення зовнішніх співпроцесорів. МП МС 68030 і старші моделі вміщують вже додатково кеш-пам’ять даних та блок керування пам’яттю, який виконує сторінкове адресування.

Програмну модель користувача МП сімейства М 680 Х 0 подано на рис. 11.18.

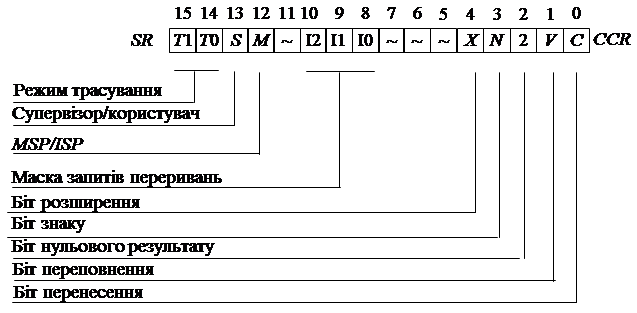

Програмна модель складається з восьми 32-розрядних регістрів даних – D 7… D 0, восьми 32-розрядних регістрів адрес – А 7… А 0, з яких регістр А 7 є вказівник стека користувача USP, 32-розрядного регістра-лічильника команд РС та 16-розрядного регістра стану SR, молодші 8 розрядів якого є регістр коду умов (прапорців) CCR користувача, а 8 старших розрядів вміщують біти стану процесора в режимі супервізора. Регістрову модель супервізора подано на рис. 11.19.

| D 0 | A 0 | ||||||||||||

| D 1 | A 1 | ||||||||||||

| D 2 | A 2 | ||||||||||||

| D 3 | A 3 | ||||||||||||

| D 4 | A 4 | ||||||||||||

| D 5 | A 5 | ||||||||||||

| D 6 | A 6 | ||||||||||||

| D 7 | A 7(USP) | ||||||||||||

| PC | |||||||||||||

| SR | CCR |

Рисунок 11.18 – Програмна модель користувача

| ISP | A '7 | |||||||||

| MSP | A "7 | |||||||||

| CCR | SR | |||||||||

| VBR | ||||||||||

| SFC | ||||||||||

| DFC | ||||||||||

| C | CE | F | Е | CACR | ||||||

| INDEX | Резерв | CAAR | ||||||||

Рисунок 11.19 – Регістрова модель супервізора МС 68020

Регістрова модель вміщує додатково два 32-розрядні регістри ISP (A 7') та MSP (A 7"). Регістр ISP виконує функції вказівника стека супервізора при обробці переривань та виключень, а регістр MSP використовується операційною системою при роботі у багатозадачному режимі. Він вказує на головний стек, до якого при перемиканні задач заноситься адреса повернення до попередньої задачі. Регістр VBR вміщує базову адресу таблиці векторів переривань, яка може переміщуватись у адресному просторі.

До трьох молодших розрядів регістрів SFC та DFC заноситься код адресного простору, який надходить на зовнішні виводи FC 2… FC 0 при пересиланні даних поміж регістрами процесора D 7… D 0 або A 7… A 0 та зовнішньою пам’яттю у привілейованих командах.

Під час запису даних з регістра Dn або An у пам’ять функціональний код FC 2… FC 0 відповідно до таблиці:

| FC 2 | FC 1 | FC 0 | Простір пам’яті |

| Пам’ять даних користувача | |||

| Пам’ять команд користувача | |||

| Пам’ять даних супервізора | |||

| Пам’ять команд супервізора |

надходить на входи МП з регістра DFC, а при зчитуванні з пам’яті – до регістра Dn або An – з регістра SFC. Одночасно функціональний код надходить до блока керування пам’яттю MMU, який звертається до відповідного адресного простору в пам’яті.

Регістри CACR та CAAR керують кеш-пам’яттю; окремі біти регістра CACR мають таке призначення:

Е = 1 дозволяє роботу кеш-пам’яті, Е = 0 забороняє звернення до кеша, але вміст кеша зберігається;

СЕ = 1 анулює вміст рядка кеша, номер якого задається вмістом поля INDEX у регістрі СААR;

F = 1 забороняє заповнення рядка кеша у разі кеш-промаху, фіксуючи поточний стан кеша;

С = 1 анулює вміст всіх рядків кеш-пам’яті.

На рис. 11.20 подано біти умов регістра стану.

|

Рисунок 11.20 – Регістр стану SR

Біти Т 1... Т 0 задають режими трасування:

| Т 1 | Т 0 | Режим |

| Трасування відсутнє | ||

| Покроковий режим | ||

| Зупин виконування програми після команд JMP, JSR, BRA тощо |

Біт S = 1 визначає режим супервізора, S = 0 – режим користувача.

Біт М = 1 при значенні біта S = 1 зумовлює вибір головного вказівника стека MSP, а M = 0 – вибір регістра ISP – вказівника стека переривань.

Контрольні питання:

1 Які нові регістри порівняно з МП МС 68000 вміщує програмна модель користувача МП МС 68020?

2 Які основні регістри має регістрова модель супервізора МС68020?

3 Чи має МП МС 68020 конвеєр команд?

4 В чому полягає різниця щодо розміщення у пам’яті таблиць векторів переривань у мікропроцесорів фірми Intel та Motorola?

5 Які нові прапорці вміщують старші 8 розрядів регістра SR і на що вони вказують?

6 Що таке маска переривань і з якою метою вона використовується?

Контрольні питання підвищеної складності:

1 Що таке MMU і які функції він виконує?

2 Як працює блок MMU за взаємодії з жорстким диском?

3 Як зорганізовується у МП МС 68010 і старших його моделей процедура перезапису відсутньої у ОЗП сторінки з жорсткого диску: апаратно чи програмно?