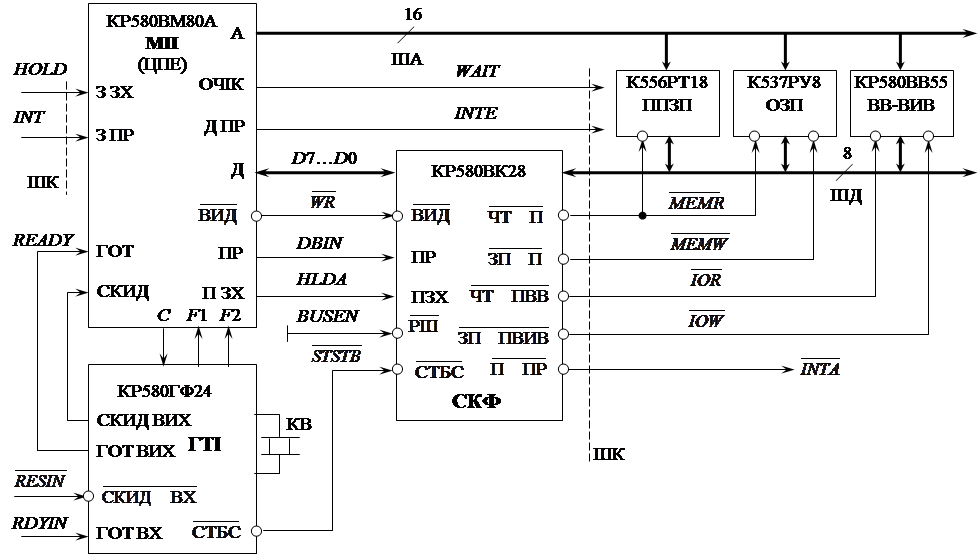

Наведена на рис. 7.5 структурна схема МПС складається з трьох підсистем – центрального процесорного елемента, підсистеми пам’яті та підсистеми введення-виведення і побудована на мікропроцесорному комплекті КР580.

Підсистема центрального процесорного елемента складається з МП типу КР580ВМ80А, генератора тактових імпульсів (ГТІ) типу КР580ГФ24 та системного контролера-формувача (СКФ) типу КР580ВК28. ГТІ виробляє кварцовану двофазову послідовність синхроімпульсів F 1 та F 2 та СТБС (строб синхронізації в інверсній формі), а також формує вхідні сигнали керування МП – скидання та готовності ГОТ. СКФ формує основні керувальні сигнали ШК.

Рисунок 7.5 – Структурна схема МПС КР580

Сигнали видачі даних від МП на ШД для інших підсистем  , прийому даних з ША у МП ПР (DBIN – DATA BUS INPUT) та підтвердження захоплення шин для пристроїв, які працюють у режимі ПДП, ПЗХ (HLDA – HOLD ACKNOWLEDGE) видаються безпосередньо з виводів МП на СКФ, а інші – короткочасно з ШД у вигляді 8-розрядного слова стану процесора ССПЦ (PCSW – PROCESSOR STATUS WORD), яке фіксується у СКФ. ССПЦ має такий порозрядний склад:

, прийому даних з ША у МП ПР (DBIN – DATA BUS INPUT) та підтвердження захоплення шин для пристроїв, які працюють у режимі ПДП, ПЗХ (HLDA – HOLD ACKNOWLEDGE) видаються безпосередньо з виводів МП на СКФ, а інші – короткочасно з ШД у вигляді 8-розрядного слова стану процесора ССПЦ (PCSW – PROCESSOR STATUS WORD), яке фіксується у СКФ. ССПЦ має такий порозрядний склад:

D 7 – ЧТ П (MEMR – MEMORY READ), читання даних з пам’яті.

D 6 – ЧТ ПВВ (INP – INPUT CYCLE), читання даних з пристроїв введення.

D 5 – М 1, робота МПС у циклі читання та виконання першого байта команди.

D 4 – ЗП ПВИВ (OUT – OUTPUT CYCLE), запис/виведення даних через пристрої виведення.

D 3 – П ЗУП (HLTA – HALT ACKNOWLEDGE), підтвердження виконання операції зупину МПС.

D 2 – СТ (ST – STACK), використання стекової пам’яті.

D 1 – ЗП-ВИВ ( – WRITE-OUTPUT), запис даних у пам’ять або виведення через пристрій виведення.

– WRITE-OUTPUT), запис даних у пам’ять або виведення через пристрій виведення.

D 0 – П ПР (INTA – INTERRUPT ACKNOWLEDGE), підтвердження переривання МПС.

СКФ синхронізується сигналом  (STSTB – STATE STROBE) – строб синхронізації. За необхідності СКФ можна відключити від ШК установленням його виходів у високоімпедансний стан; для цього на його вхід ДШ (BUSEN – дозвіл шин) треба подати сигнал, який дорівнює 1.

(STSTB – STATE STROBE) – строб синхронізації. За необхідності СКФ можна відключити від ШК установленням його виходів у високоімпедансний стан; для цього на його вхід ДШ (BUSEN – дозвіл шин) треба подати сигнал, який дорівнює 1.

Таким чином на ШК з СКФ подаються такі сигнали:

–  – читання даних з пам’яті;

– читання даних з пам’яті;

–  (

( – MEMORY WRITE) – запис даних у пам’ять;

– MEMORY WRITE) – запис даних у пам’ять;

–  (

( – INPUT-OUTPUT READ) – читання даних з пристроїв введення;

– INPUT-OUTPUT READ) – читання даних з пристроїв введення;

– ЗП ПВИВ ( – INPUT-OUTPUT WRITE) – запис даних у пристрій виведення;

– INPUT-OUTPUT WRITE) – запис даних у пристрій виведення;

–  (INTA) – підтвердження переривання;

(INTA) – підтвердження переривання;

–  (WAIT) – очікування, робота МПС призупиняється;

(WAIT) – очікування, робота МПС призупиняється;

–  (INTE – INTERRUPT ENABLE) – дозвіл переривання.

(INTE – INTERRUPT ENABLE) – дозвіл переривання.

МП може отримувати від різних зовнішніх пристроїв керувальні сигнали:

– З ЗХ (HOLD) – запит на захоплення шин пристроями, які працюють у режимі ПДП;

– З ПР (INT – INTERRUPT) – запит на переривання роботи МПС;

–  (

( – RESET IN) – СКИД (RESET) – скидання МП, установлення в нуль програмного лічильника РС;

– RESET IN) – СКИД (RESET) – скидання МП, установлення в нуль програмного лічильника РС;

– ГОТ ВХ (RDYIN – READY IN) – ГОТ (READY) – сигнал готовності зовнішніх пристроїв до обміну даними.

СКФ організує буферування ШД та її двонаправленість. Для спрощення на схемі не показані також буфери ША та ШК.

ППЗП призначене для зберігання програм і підпрограм та ОЗП, призначене для тимчасового зберігання проміжних результатів та організації стека, складає підсистему пам’яті. Підсистема введення-виведення може складатися, наприклад, з паралельного або послідовного інтерфейсів, контролерів ПДП або переривань.

Функціонування МПС

Для виконання команди програми необхідна взаємодія якнайменш двох підсистем МПС: підсистеми центрального процесорного елемента та підсистеми пам’яті. Команда зчитується з ППЗП, декодується та виконується. На всі процедури, залежно від типу команди, витрачається від одного до п’яти машинних циклів М1...М5.

У кожному циклі МП один раз звертається до пам’яті або пристрою введення-виведення.

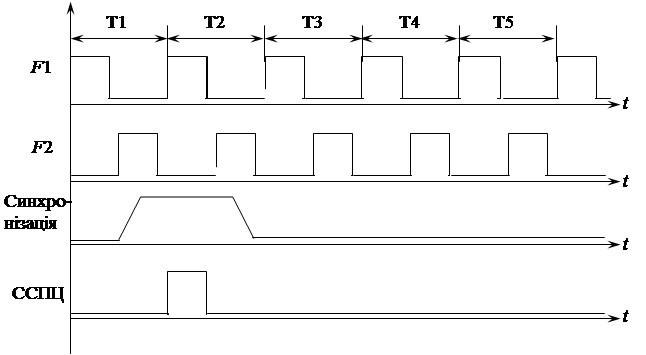

Кожний з машинних циклів складається з трьох-п’яти машинних тактів Т1...Т5, тривалість такту визначається періодом тактових імпульсів ГТІ (рис. 7.6).

|

Рисунок 7.6 – Часова діаграма циклу з п'яти тактів

Такти відраховуються від фронтів імпульсів F 1. Якщо МП К580ВМ80А працює на частоті 2 МГц, то тривалість одного такту складає 0,5 мкс. За цей час у системі виконується одна або водночас декілька елементарних дій – мікрооперацій. Набір керувальних сигналів, які керують самим МП, змінюються кожного такту, а в МПС сигнали керування оновлюються тільки на початку кожного машинного циклу команди, тобто за кілька тактів – від 4 до 18 залежно від команди.

У МПС може вироблятися до 10 різних ССПЦ, тобто до 10 різних типів машинних циклів, які показані в табл. 7.1.

Таблиця 7.1 – Типи машинних циклів

| № пп. | Тип циклу | Код ССПЦ |

| Вибірка коду операції команди | ||

| Читання пам’яті | ||

| Запис у пам’ять | ||

| Читання із стека | ||

| Запис у стек | ||

| Читання з пристрою введення | ||

| Запис у пристрій виведення | ||

| Дозвіл переривань | ||

| Дозвіл зупину | ||

| Дозвіл переривань під час зупину |

Виконання будь-якої команди завжди починається з основного машинного циклу М1, який складається з чотирьох або п’яти тактів:

Т1 – з програмного лічильника (РС) через буфер адреси (БА) на ША МП видає адресу комірки ППЗП з кодом операції виконуваної команди, після чого вміст РС збільшується на 1 (інкрементується); в інших циклах М2...М5 на такті Т1 на ША видається адреса комірки пам’яті для зчитування або запису даних або номер (адреса) пристрою введення-виведення. Одночасно у Т1 кожного циклу в СКФ по ШД надходить слово стану процесора (ССПЦ).

Т2 – ССПЦ фіксується у регістрі СКФ, після чого формуються сигнали ПР (DBIN) та  (

( ) для керування подальшим зчитуванням у МП коду операції та його декодування. Одночасно в Т2 аналізуються сигнали готовності ГОТ (READY), запиту захоплення шин ЗЗХ (HOLD) та ЗУП (HАLТ). При виконанні Т2 у машинних циклах М2...М5 ССПЦ також фіксується в СКФ, але далі виконуються дії залежні від команди.

) для керування подальшим зчитуванням у МП коду операції та його декодування. Одночасно в Т2 аналізуються сигнали готовності ГОТ (READY), запиту захоплення шин ЗЗХ (HOLD) та ЗУП (HАLТ). При виконанні Т2 у машинних циклах М2...М5 ССПЦ також фіксується в СКФ, але далі виконуються дії залежні від команди.

Т3 – за адресою пам’яті, поданої на ША, зчитується з пам’яті код операції команди та надходить із ШД на регістр коду операції МП (РКОП) для декодування. При виконанні інших циклів М2...М5 у такті Т3 вибираються дані з пам’яті, пристроїв введення, стека або дані виводяться в пам’ять, пристрої виведення та стек.

Т4, Т5 – у МП розшифровується прийнятий код операції команди, визначається її формат, виконуються однобайтові команди або формуються машинні цикли М2...М5 для виконання дво- та трибайтових команд. При виконанні циклів М2...М5 у Т4 виконуються дії залежно від команди, а Т5 може бути відсутній.

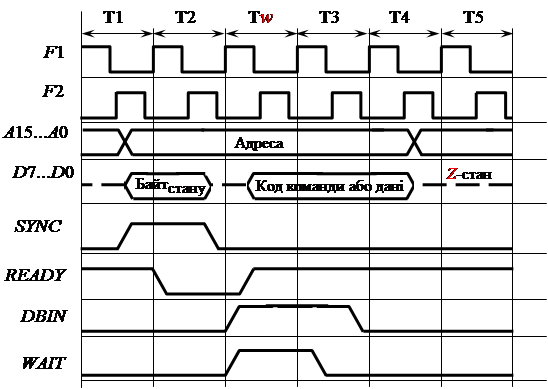

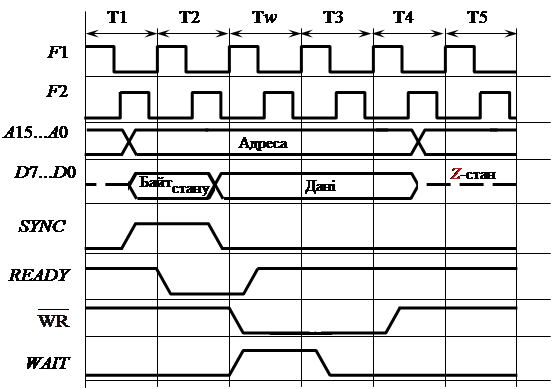

На рис. 7.7 показані спрощені часові діаграми циклів вибірки та читання пам’яті, а на рис. 7.8 – часові діаграми циклу запису в пам’ять.

|

Рисунок 7.7 – Часові діаграми циклів вибірки (читання пам’яті)

|

Рисунок 7.8 – Часові діаграмі циклу запису в пам’ять

На діаграмах показано також реакцію МП на наявність сигналу неготовності, який перевіряється в Т2. Якщо зовнішні пристрої неготові до обміну або надійшов сигнал ЗЗХ, сигнал ГОТ = 0 й обмін даними здійснюватись не може і після такту Т2 уставляється один, як показано на рис. 7.7 і 7.8, або кілька тактів очікування Tw залежно від готовності зовнішніх пристроїв або пам’яті.