Функционирование схемы декодера (рисунок 7) сводится к следующему. Принятая кодовая комбинация, которая отображается полиномом Р(х) поступает в декодирующий регистр и одновременно в ячейки буферного регистра, который содержит k ячеек. Ячейки буферного регистра связаны через логические схемы "нет", пропускающие сигналы только при наличии "1" на первом входе и "0" - на втором (этот вход отмечен кружочком). На вход буферного регистра кодовая комбинация поступит через схему И1. Этот ключ открывается с выхода триггера Т первым тактовым импульсом и закрывается k+1 тактовым импульсом (полностью аналогично работе триггера Т в схеме кодера). Таким образом, после k=501 тактов информационная группа элементов будет записана в буферный регистр. Схемы НЕТ в режиме заполнения регистра открыты, ибо на вторые входы напряжение со стороны ключа И2 не поступает.

Одновременно в декодирующем регистре происходит в продолжение всех n=511 тактов деление кодовой комбинации (полином Р(х) на порождающий полином g(х)). Схема декодирующего регистра полностью аналогична схеме деления кодера, которая подробно рассматривалась выше. Если в результате деления получится нулевой остаток- синдром S(х)=0, то последующие тактовые импульсы спишут информационныеэлементы на выход декодера.

При наличии ошибок в принятой комбинации синдром S(х) не равен 0. Это означает, что после n-го (511) такта хотя бы в одной ячейке декодирующего регистра будет записана “1”.Тогдана выходе схемы ИЛИ появится сигнал. Ключ 2 (схема И2) сработает, схемы НЕТ буферного регистра закроются, а очередной тактовый импульс переведет все ячейки регистра в состояние "0". Неправильно принятая информация будет стерта. Одновременно сигнал стирания используется как команда на блокировку приемника и переспрос.

Рисунок 7 – Структурная схема декодера

2.6 Получение схемы кодирующего и декодирующего устройства циклического кода с применением пакета «SystemView»

На вход кодера подается сигнал 1 и 510 нулей

Рисунок 8 – Схема кодера

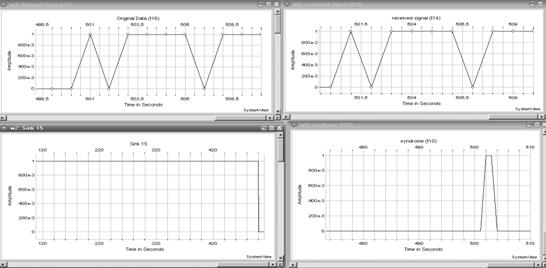

На рисунке 10 представлены входной и выходной сигналы кодера, а также исправляющая комбинация к.

Рисунок 10 - Входной и выходной сигналы кодера

Рисунок 11 – Схема декодера

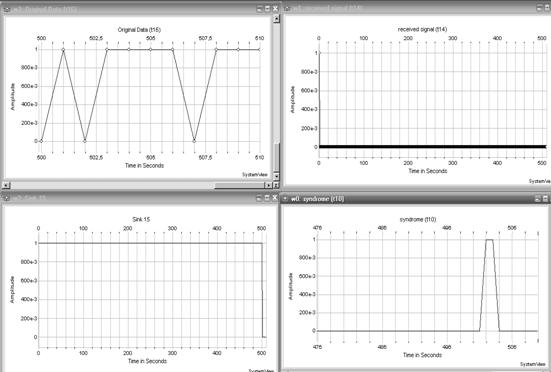

Рисунок 12 – сигналы декодера, полученные в окне анализа

На рисунке 13 представлен декодер с исправлением ошибок.

Рисунок 13 - Декодер с исправлением ошибок

Рисунок 14 - Сигналы декодера с исправлением ошибок

2.7 Определение объема передаваемой информации при заданном температуреTпер и критерии отказа t отк.

Объем передаваемой информации находится по формуле (22).

W = R.B.(Tпер – tотк). (22)

(бит).

(бит).

где R - наибольшая относительная пропускная способность для выбранных параметров циклического кода.