Счётчик - устройство, на выходах которого получается код, определяемый числом поступивших импульсов. Счётчики могут строиться на Tили JK -триггерах. Основной параметр счётчика - модуль счёта (максимальное число единичных сигналов, которое может быть сосчитано счётчиком). Счётчики классифицируют:

· по модулю счёта: двоично-десятичные; двоичные; с произвольным постоянным модулем счёта; с переменным модулем счёта;

· по направлению счёта: суммирующие; вычитающие; реверсивные;

· по способу формирования внутренних связей: с последовательным переносом; с параллельным переносом; с комбинированным переносом; кольцевые;

Двоичный счетчик.

Действие четырехразрядного двоичного счетчика на JK-триггерах (рис.1) поясняют временные диаграммы, из которых следует, что до прихода первого импульса все триггеры находились в нулевом состоянии.

|

| ||

Рис. 1. Двоичный счетчик. Структурная схема. Временные диаграммы.

Срез первого импульса переключает нулевой триггер в единичное состояние. Затем срез второго импульса переключает его в нулевое состояние и т. д. Триггер под номером 1 переключается срезом импульса с выхода триггера 0 и т. д. Из временных диаграмм видно, что частота следования импульсов каждым триггером делится на 2. После прихода шестнадцати импульсов все четыре триггера находятся в таком же состоянии, как и до прихода первого импульса. Наблюдая состояние выходов Q0, Q1, Q2 и Q3 можно судить о том, сколько пришло импульсов. Например, при нуле импульсов Q0 = Q1 = Q2 = Q3= 0. После прихода пятнадцати импульсов Q0 = Q1 = Q2 = О3= 1. В первом случае это соответствует записи числа 0 в виде 0000, а во втором - записи числа 15 в виде 1111. После прихода восьми импульсов Q0=Ql=Q2=0 и Q3=1. Следовательно, числа записываются в обратном порядке - последний разряд является высшим. В интегральном исполнении выпускаются 4-, 8- и 12-разрядные счетчики. Счетчики одновременно являются и делителями частоты в 2n раз, где n - число разрядов. Описанный выше счетчик называется асинхронным или последовательным. В нем каждый последующий каскад считает после предыдущего.

Десятичный счетчик.

Десятичный счетчик состоит из декадных счетчиков, причем число декадных счетчиков равно максимальному разряду десятичных чисел, которые счетчик может считать. Каждый декадный счетчик является двоично-десятичным. Он считает в двоично-десятичном коде от 0 до 10. При поступлении на вход декадного счетчика десятого импульса все его выходы устанавливаются в нулевое состояние. Схема декадного счетчика и временные диаграммы показаны на рис.2.

|

|

|

Рис. 2. Декадный счетчик. Временные диаграммы. Структурная схема.

Благодаря обратной связи инвертирующего выхода третьего триггера со входом первого триггера на входе первого триггера J = Q 3 = 1, пока не пришел и не закончился восьмой импульс. После окончания восьмого импульса Q 3 = 0. В соответствии с таблицей состояний JK-триггера выход первого триггера (на рис. 2 второй справа) Q1 = 0, так как для него J = Q 3 = 0; К = 1. Второй триггер (на рис. 13.3 а третий справа) является Т-триггером, так как у него J = К = 1 = const, и управляется он срезом импульса Q1. В соответствии с временными диаграммами (рис.2) его переключение произойдет лишь после 14-го импульса. Третий триггер имеет J = J1 = J2 = 0; К = K1 = К2 = 1. По окончании десятого импульса он переключается в нулевое состояние срезом импульса Q0. Из временных диаграмм видно, что после десятого импульса выходы всех триггеров находятся в нулевом состоянии. Если выход Q3 подать на вход С нулевого триггера следующего декадного счетчика, то на выходе этого триггера Q0 становится равным 1 по окончании импульса Q3 первого декадного счетчика. Очевидно, что первый декадный счетчик считает единицы, а второй - десятки.

Делитель частоты

Делитель частоты - электронное устройство, уменьшающее в целое число раз частоту подводимых к нему периодических колебаний. Их используют в синтезаторах частоты, кварцевых часах, в телевизионных устройствах синхронизации генераторов развёрток и др. Для деления частоты применяют: электронный счётчик (см. Триггер), самовозбуждающийся генератор синусоидальных колебаний и т.д..

Делители частоты считают входные импульсы до некоторого задаваемого коэффициентом счета состояния, а затем формируют сигнал переключения триггеров в нулевое состояние, вновь начинают счет входных импульсов до задаваемого коэффициента счета.

Регистры

Регистр - последовательное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств.

Регистры классифицируются по следующим видам:

1. Параллельные или накопительные (регистры памяти, хранения);

2. Последовательные или сдвигающие.

В свою очередь сдвигающие регистры делятся:

· по способу ввода-вывода информация: параллельные; последовательные; комбинированные;

· по направлению передачи информации: однонаправленные; реверсивные.

Типичными являются следующие операции:

· прием слова в регистр;

· передача слова из регистра;

· поразрядные логические операции;

· сдвиг слова влево или вправо на заданное число разрядов;

· преобразование последовательного кода слова в параллельный и обратно;

· установка регистра в начальное состояние (сброс)

Элементарной ячейкой электронной памяти является триггер, способный сохранять 1 бит записанной в нем информации. Регистром называется устройство из триггеров, предназначенное для записи, хранения и выдачи информации. Каждый разряд двоичного числа записывается в своем триггере, поэтому число триггеров в регистре определяет разрядность записываемого числа. Наиболее распространенным видом регистров являются регистры сдвига.

Регистры сдвига.

Регистром сдвига называют цифровую схему, состоящую из последовательно включенных триггеров, содержимое которых можно сдвигать на один разряд влево или вправо подачей тактовых импульсов. Регистры сдвига широко применяются в цифровой вычислительной технике для преобразования последовательного кода в параллельный или параллельного в последовательный, а также при построении арифметико - логических устройств. Составляется регистр сдвига из соединенных последовательно триггеров, в которые записываются разряды обрабатываемого кода. При наличии разрешающих сигналов импульс, приходящий на тактовый вход регистра, вызывает перемещение записанной информации на один разряд влево или вправо. На рис. 1 приведена структурная схема регистра сдвига на синхронных JK-триггерах.

Рис. 3 Регистр сдвига на JK - триггерах.

Рассмотрим действие регистра при записи в него числа 0011, начиная с правого - младшего - разряда. До записи числа все триггеры устанавливают в нулевое состояние. Затем на вход схемы подается серия импульсов, соответствующая записываемому числу, а на вход С подаются тактовые импульсы. Сначала на вход поступает импульс, соответствующий первому из записываемых разрядов. В конце тактового импульса он дает Q3 = 1 на выходе левого триггера. В конце следующего тактового импульса информационный импульс продвигается на выход следующего триггера и т. д. Одновременно продвигаются вправо и другие цифры записываемого числа. После прихода четырех тактовых импульсов все число оказывается записанным в четырех триггерах, причем старший разряд числа записи в левом триггере, а младший - в правом. Чтобы записанная информация сохранилась, дальнейший сдвиг прекращается. Это осуществляется прекращением подачи тактовых импульсов. Описанный регистр называется регистром сдвига с последовательным приемом информации. Выдача информации у него может быть как параллельной, так и последовательной. При параллельной выдаче информация снимается одновременно с выходов всех триггеров. Последовательная выдача осуществляется с выхода Q0 при последующих тактовых импульсах. Параллельный прием информации может быть осуществлен подачей ее на выводы предустановки. Мы рассмотрели работу простейшего регистра, осуществляющего сдвиг в одну сторону. Существуют реверсивные регистры сдвига, переключаемые на сдвиг вправо и влево. Если 0 и 1 в регистре трактовать как двоичную запись числа, то сдвиг в одну сторону соответствует делению на 2, а в другую - умножению на 2. Как известно, умножение двух десятичных чисел "столбиком" соответствует сложению частных произведений, сдвинутых поразрядно влево. Аналогично столбиком перемножаются и двоичные числа, но эта операция выполняется проще, так как частные произведения получаются умножением единиц и нулей умножаемого числа на единицы и нули множителя. Следовательно, умножение сводится к операции сложения сдвинутых поразрядно двоичных чисел. Аналогично осуществляется и деление двоичных чисел.

.

Суть сдвига состоит в том, что по сигналу синхроимпульса происходит одновременная перезапись содержимого каждого триггера в соседний триггер. При этом не меняется само двоичное слово (число), записанное в регистре, оно лишь сдвигается на один разряд и только содержимое последнего триггера ТТ3 пропадает из регистра, а на вход первого ТТ0 поступает новый бит(см. рис.1)

а) б)

Рис. 1. Сдвигающий регистр

а) схема на непрозрачных триггерах

б) условное обозначение

Сдвигающий регистр в отличие от регистра памяти должен обязательно состоять из непрозрачных триггеров, иначе при первом же сигнале сдвига бит, поступивший на вход первого триггера регистра сдвига, сразу же пройдёт на выход этого триггера и соответственно, на вход второго триггера, а значит и на выход второго триггера и т. д. до последнего триггера регистра сдвига.

В некоторых сдвиговых регистрах сдвиг происходит не только в одну сторону, а и влево и вправо - это так называемые реверсивные регистры.

Чтобы обеспечить реверс сдвига и параллельную запись сразу во все триггеры к D-входу каждого i-того триггера подключён мультиплексор, который при подаче " 1 " на один из управляющих входов - SL(Shift Left - сдвиг влево), SR(Shift Right - сдвиг вправо) или PL(Parallel load - параллельная загрузка) подключает вход i-того триггера соответственно к выходу младшего соседа (направление A), старшего соседа (направление B) или к выходу параллельной загрузки Di (см. рис.2). Точка A самого младшего триггера (разряда) является входом DR, точка В самого старшего разряда - входом DL (входы DL и DR используются для наращивания разрядности реверсивных регистров). Выход i-го триггера подключён к соответствующим входам мультиплексоров соседних разрядов. По С-сигналу триггеры регистра принимают информацию с направлений, диктуемых мультиплексорами.

Рис.2 Схема одного разряда реверсивного регистра.

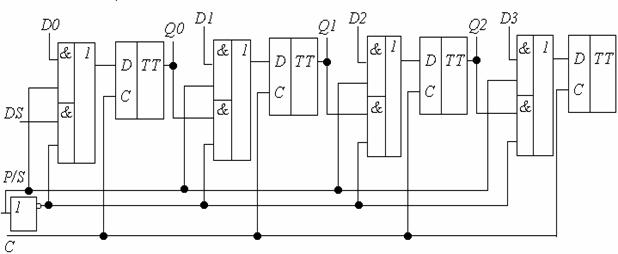

На рис.3 представлена принципиальная схема сдвигового регистра с параллельным и последовательным вводом данных.

Рис.3 Сдвиговый регистр с возможностью параллельного и последовательного ввода данных.

DS - Data Serial - вход для последовательного ввода данных

P/S - Parallel/Serial - выбор режима работы

Чтобы 4-х разрядное двоичное число, представленное в параллельном коде, преобразовать в последовательный код, надо сначала разряды этого числа подать на входы D0,D1,D2,D3 регистра, а одновременно с этим подать разрешение на параллельную запись, т.е. P/S = 1 и подать один или несколько импульсов на С-вход регистра.

После этого нужно запретить параллельную запись в регистр и тем самым разрешить последовательный режим регистра (P/S = 0). Теперь на каждый синхроимпульс выход D3 будет выдавать поочерёдно разряды записанного двоичного числа.

Обычно последовательный код начинается младшим разрядом, а в данном регистре первым на выход поступит разряд числа, записанный ранее на триггер ТТ3, значит при параллельной записи следует проследить, чтобы младший разряд был записан в триггер ТТ3, а старший - в ТТ0.

Рассмотрим схему преобразования параллельного кода в последовательный, приведённую на рис.4. Данные параллельным кодом загружаются в регистр RG1, пока P/S=1. Затем при P/S=0 RG1 переходит в режим сдвига (последовательный режим) и в течение 4-х импульсов на С- входе RG1 содержимое этого регистра с его выхода Q3 разряд за разрядом передаётся на RG2 на вход DS, где записывается последовательным кодом благодаря подаче 4-х синхроимпульсов на вход C RD2. После этого данные могут быть считаны параллельным кодом с выходов Q0-Q3 регистра RG2.

Рис.4 Преобразование параллельного кода в последовательный

Рис.5 Условное обозначение и цоколевка микросхемы К155ИР1

Доп.информация (учебник:Касаткин, Электротехника стр. 321)+схемы из тетради по лекциям.