Дешифратор - это устройство, предназначенное для распознавания различных кодовых комбинаций (слов). Это, как правило, комбинационная схема, обеспечивающая преобразование двоичной кодовой информации, записанной в счетчике, регистре, в управляющие сигналы. Эти управляющие сигналы поступают либо на исполнительные элементы вычислительных машин (например, для преобразования адресов ячеек памяти в сигналы выборки ячеек при записи и считывании информации из них), либо в устройства отображения информации (световые табло, цифровые индикаторы и др.).

Дешифратор имеет несколько входов (по числу выводов счетчика или регистра) и несколько выходов. Количество выходов дешифратора равно числу разрешенных наборов выходных сигналов. В дешифраторе с  входами и

входами и  выходами

выходами  .

.

Дешифратор, имеющий  выходов, называется полным, а при меньшем числе выходов - неполным.

выходов, называется полным, а при меньшем числе выходов - неполным.

На входы дешифратора поступает информация в виде различных комбинаций “0” и “1”. Каждой комбинации состояний на выходах дешифратора соответствует определенная комбинация состояний на входах. Если выходы дешифратора обозначать  , где

, где  - номер выхода, например, в десятичной системе счисления, то каждой комбинации “0” и “1” на входах (двоичное кодовое число) будет соответствовать “1” на том выходе

- номер выхода, например, в десятичной системе счисления, то каждой комбинации “0” и “1” на входах (двоичное кодовое число) будет соответствовать “1” на том выходе  , номер “

, номер “  ” которого есть десятичное представление этого двоичного числа.

” которого есть десятичное представление этого двоичного числа.

Функционирование дешифраторов описывается системой логических функций, так, например, при трех входах это:

Применяют три основных способа построения дешифраторов: линейный, пирамидальный, ступенчатый.

Линейный дешифратор является наиболее простым и строится непосредственно в соответствии с системой логических функций без дополнительных преобразований функции выходов. Время задержки распространения сигнала в линейном дешифраторе равно времени задержки распространения сигнала в цепи последовательно включенных элементов “И” (“И-НЕ”) и инвертора.

Пирамидальный дешифратор строится на основе последовательной (каскадной) реализации входных функций. Сначала реализуется конъюнкция (“И”) двух переменных, например,  . На втором этапе реализуются конъюнкции трех переменных путем логического умножения каждой полученной конъюнкции двух переменных на переменную

. На втором этапе реализуются конъюнкции трех переменных путем логического умножения каждой полученной конъюнкции двух переменных на переменную  и т.д. В результате на каждом последующем этапе получают вдвое больше конъюнкций (“И”), чем на предыдущем этапе. Количество последовательно включенных элементов равно

и т.д. В результате на каждом последующем этапе получают вдвое больше конъюнкций (“И”), чем на предыдущем этапе. Количество последовательно включенных элементов равно  , где

, где  - число входов, поэтому быстродействие низкое.

- число входов, поэтому быстродействие низкое.

Ступенчатый дешифратор строится на основе двух дешифраторов на “  ” и “

” и “  ” входов и

” входов и  двухвходовых конъюнкторов. При большом числе входов ступенчатые дешифраторы имеют существенно меньшие аппаратурные затраты, чем линейные и пирамидальные, и большее быстродействие.

двухвходовых конъюнкторов. При большом числе входов ступенчатые дешифраторы имеют существенно меньшие аппаратурные затраты, чем линейные и пирамидальные, и большее быстродействие.

Дешифраторы выпускают в виде отдельных ИМС. Наиболее часто применяется дешифратор, реализованный на ИМС К155ИД1, и преобразующий двоичный код в десятичное число. Дешифраторы широко применяют в вычислительной и информационно-измерительной технике. Одно из направлений - управление индикаторами, отображающими знаковую информацию.

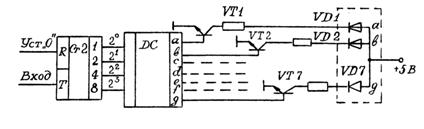

Примером такого применения может быть схема счета и отображения числа импульсов, приведенная на рис.8.1. Она содержит двоичный счетчик  , который представляет число поступивших на его вход импульсов в двоичном коде,

, который представляет число поступивших на его вход импульсов в двоичном коде,  - дешифратор, управляющий транзисторными ключами на VT1-VT7 и семисегментный светодиодный индикатор VD1-VD7.

- дешифратор, управляющий транзисторными ключами на VT1-VT7 и семисегментный светодиодный индикатор VD1-VD7.

Рис. 8.1 Схема счета и отображения числа импульсов.

Регистры

Регистры и счетчики являются цифровыми устройствами последовательного типа. Они относятся к цифровым автоматам с памятью.

Числа, которыми оперируют регистры и счетчики, представлены в двоичном коде.

Регистром называют цифровой узел, предназначенный для записи и,хранения, преобразования и выдачи информации.

По своей структурной схеме и вытекающим отсюда возможностям регистры подразделяются на параллельные, последовательные и последовательно – параллельные.

| Таблица 13 | |||

| N | N | ||

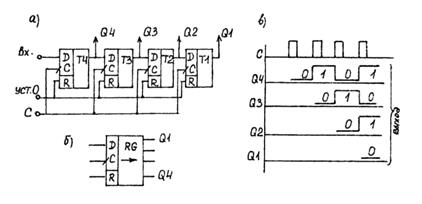

На рис. 8.2 представлена функциональная схема, условное обозначение и временные диаграммы, поясняющие работу последовательного регистра – регистра сдвига.

Регистр сдвига (последовательный регистр) предназначен для записи, хранения, преобразования информации путем ее сдвига под воздействием тактового импульса и выдачи информации.

Перед началом работы все триггеры сигналом по шине “уст.0” устанавливаются в нулевое состояние. С каждым тактовым импульсом информация в виде последовательного кода “продвигается” по Д – триггеру, и после четвертого импульса она оказывается записанной в регистр. Считывать информацию можно в виде параллельного кода с выходов Q4…Q1 или в виде последовательного кода с Q1 после четырех тактовых импульсов

Рис. 8.2 Функциональная схема а), условное обозначение б) и