Генератор тактовых импульсов обеспечивает синхронизацию работы МПС. В составе МПК К1810 имеется микросхема К1810ГФ84 (далее ГФ84), предназначенная для формирования серий синхроимпульсов, сигналов сброса и готовности системы на основе микропроцессора ВМ86.

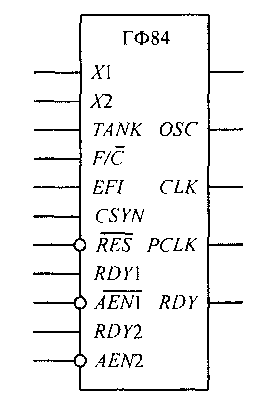

Генератор ГФ84 характеризуется: схемотехнологией – ТТЛШ; частотой синхронизации – до 80 МГц; напряжением питания – плюс 5 В и потребляемой мощностью – 0,7 Вт; амплитудой импульсов – 4,5 В (рисунок 8.3.4.1.).

Рисунок 8.3.4.1. Структура ГТИ К1810ГФ84

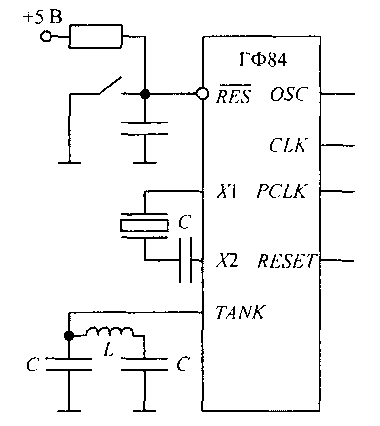

Микросхема ГФ84 содержит схемы задающего генератора G, делители частоты на три DIV3 и два DIV2, которые вместе с логическими элементами вырабатывают прямоугольные импульсы CLK, PCLK и синусоидальный сигнал OSC. Они предназначены соответственно для тактирования работы микропроцессора ВМ86, портов периферии или внешних устройств системы. Сигналы синхронизации могут формироваться из колебаний основной частоты кварцевого резонатора, подключенного к входам Z1 и Х2 (рисунок 8.3.4.2.).

|

|

Рисунок 8.3.4.2. Генератор тактовых импульсов ГФ84: а – условное графическое обозначение; б – схема подключения кварцевого резонатора

С помощью LC -фильтра, соединенного с входом TANK, можно изменить частоту колебаний резонатора.

Генератор может синхронизироваться и от внешнего источника сигналов, который подключается ко входу EFI. Режим синхронизации задают уровнем сигнала на входе F/  : при высоком – от внешнего генератора, при низком – от кварцевого генератора. В обоих режимах синхронизации частота сигналов CLK вдвое больше частоты PCLK, однако в три раза меньше частоты OSC или внешнего генератора (рисунок 8.3.4.3, а).

: при высоком – от внешнего генератора, при низком – от кварцевого генератора. В обоих режимах синхронизации частота сигналов CLK вдвое больше частоты PCLK, однако в три раза меньше частоты OSC или внешнего генератора (рисунок 8.3.4.3, а).

|

|

Рисунок 8.3.4.3. Временные диаграммы сигналов: а – синхронизации; б – готовности

Вход CSYN служит для синхронизации нескольких ГТИ системы: если CSYN = 1, то на выходах CLK и PCLK устанавливаются высокие уровни; при CSYN = 0 на выходы CLK и PCLK поступают синхросерии.

Схема формирования сигнала сброса RESET имеет на входе триггер Шмидта, а на выходе – D-триггер, который формирует фронт сигнала RESET по спаду CLK. Обычно ко входу  подключается RС -цепь, которая обеспечивает автоматическое формирование сигнала сброс при включении источника напряжения.

подключается RС -цепь, которая обеспечивает автоматическое формирование сигнала сброс при включении источника напряжения.

Схема формирования сигнала готовности к обмену данными RDY построена с учетом шины Multibus. Она имеет две пары одинаковых сигналов RDY1,  и RDY2,

и RDY2,  , объединенных схемой И ИЛИ:

, объединенных схемой И ИЛИ:

REDY  REDYI

REDYI  AENI

AENI  REDY2

REDY2  AEN2.

AEN2.

D -триггер формирует фронт сигнала RDY по спаду CLK и подает его на вход готовности микропроцессора.