Ѕуферные регистры и двунаправленные шинные формирователи обеспечивают в ћѕ— соответственно временное хранение (фиксацию) адреса с выходов ÷ѕ и двунаправленный обмен данными между локальной и системной шинами. ¬ составе ћѕ –580 дл€ выполнени€ этих функций имеетс€ регистр –580»–82 (далее »–82) и шинный формирователь –580¬ј86 (далее ¬ј86).

¬осьмиразр€дный буферный регистр »–82

¬осьмиразр€дный буферный регистр »–82 с трем€ состо€ни€ми характеризуют следующие параметры: схемотехнологи€ Ц ““ЋЎ; число транзисторов на кристалле Ц 524; напр€жение питани€ Ц плюс 5¬ и потребл€ема€ мощность 1 ¬т.

–егистр »–82 имеет восемь триггеров, стробированна€ запись данных в которые выполн€етс€ по сходам DI7-DI0 при значении сигнала STB = 1 (рисунок 8.3.4.4). ѕр€мые выходы D07-D00 регистра подключены к буферным схемам SW трем€ состо€ни€ми.

ѕри значении сигнала  0 буферы открываютс€ и данные передаютс€ на выход. ≈сли

0 буферы открываютс€ и данные передаютс€ на выход. ≈сли  = 1, то буферы устанавливаютс€ в Z -состо€ние. —игнал

= 1, то буферы устанавливаютс€ в Z -состо€ние. —игнал  не вли€ет на состо€ние триггеров и функцию записи информации.

не вли€ет на состо€ние триггеров и функцию записи информации.

–исунок8.3.4.4. Ѕуферный регистр »–82: а Ц условное обозначение; б Цфункциональна€ схема

Ўинный формирователь ¬ј86 обеспечивает двунаправленный обмен данными между локальной и системной шинами, усиление сигналов и отключение от шины в определенные моменты времени. ћикросхема ¬ј86 характеризуетс€ следующими параметрами: ““ЋЎ схемотехнологией, числом транзисторов на кристалле Ц 567; напр€жением питани€ Ц плюс 5 ¬ и потребл€емой мощностью Ц 1 ¬т.

Ўинный формирователь (Ў‘) имеет двунаправленные входы-выходы ј7-ј0 и ¬7-¬0, вход “ дл€ управлени€ направлением обмена и вход  дл€ сн€ти€ Z-состо€ни€ определенного направлени€ переходу (рисунок 8.3.4.5).

дл€ сн€ти€ Z-состо€ни€ определенного направлени€ переходу (рисунок 8.3.4.5).

аждый разр€д формировател€ содержит две схемы SW с трем€ состо€ни€ми кажда€. ѕри ќ≈ = 1 все SW -схемы наход€тс€ в Z -состо€нии, при  = 0 и “ = 0 обмен данными выполн€етс€ в направлении от ј к ¬. ѕри

= 0 и “ = 0 обмен данными выполн€етс€ в направлении от ј к ¬. ѕри

0 и “ = 1 обмен данными выполн€етс€ от ¬ к ј.

0 и “ = 1 обмен данными выполн€етс€ от ¬ к ј.

‘ормирователь потребл€ет от ÷ѕ ток около одного миллиампера, а может отдавать в системную шину дес€тки миллиампер

|

|

–исунок 8.3.4.5. Ўинный формирователь ¬ј86: а Ц условное обозначение; б Ц функциональна€ схема

онтроллер системной шины

ƒл€ управлени€ обменом данными в ћѕ— используетс€ системный контроллер. ¬ составе ћѕ 1810 имеетс€ микросхема 1810¬√88 (далее ¬√88), котора€ реализует функции системного контроллера шины ( Ў). ћикросхема ¬√88 имеет следующие технические характеристики: схемотехнологи€ Ц ““ЋЎ; частота синхронизации Ц 8 ћ√ц; напр€жение питани€ Ц плюс 5 ¬; потребл€ема€ мощность Ч 85 ¬т.

онтроллер шины реализует в ћѕ— следующие функции: дешифрацию состо€≠ний микропроцессора, формирование управл€ющих и командных сигналов дл€ локальных и системных шин; выработку сигналов управлени€ Ў‘, буферными регистрами и контроллером прерываний. ¬ состав Ў вход€т (рисунок 8.3.4.5.): дешифратор состо€ний ƒш—, схема управлени€ —х”, формирователь командных ‘1 и управл€ющих ‘2 сигналов.

|

|

|

–исунок 8.3.4.5. —труктура контроллера шины ¬√88

‘ункциональное назначение входных сигналов Ў:  ,

,  ,

,  Ц состо€ни€ микропроцессора; CLK Ц синхронизаци€ от √“»;

Ц состо€ни€ микропроцессора; CLK Ц синхронизаци€ от √“»;  Ц разрешение выдачи синалов по командным выводам; CEN Ц разрешение выдачи командных сигналов и сигналов управлени€ DEN,

Ц разрешение выдачи синалов по командным выводам; CEN Ц разрешение выдачи командных сигналов и сигналов управлени€ DEN,  ; IO¬ Ц управление режимом работы.

; IO¬ Ц управление режимом работы.

¬ыходные сигналы Ў по функциональным признакам распределены на командные сигналы интерфейса и сигналы управлени€.

командным сигналам интерфейса относ€тс€:  - чтение пам€ти;

- чтение пам€ти;  Ц запись в пам€ть;

Ц запись в пам€ть;  Ц ввод из порта;

Ц ввод из порта;  предупреждающие подготовительные сигналы записи в пам€ть или вывода в порт;

предупреждающие подготовительные сигналы записи в пам€ть или вывода в порт;  Ц подтверждение прерывани€.

Ц подтверждение прерывани€.

выходным управл€ющим сигналам јЎ относ€тс€: DT/  Ц выбор направ≠лени€ передачи данных через Ў‘; DEN Ц разрешение выдачи данных; ALE Ц строб записи адреса в буферный регистр; MCE/

Ц выбор направ≠лени€ передачи данных через Ў‘; DEN Ц разрешение выдачи данных; ALE Ц строб записи адреса в буферный регистр; MCE/  Ц в режиме работы с сис≠темной шиной используетс€ как строб чтени€ номера ведомого контроллера прерываний. ѕри работе с Ў¬¬ используетс€ дл€ управлени€ состо€нием УвключенФ Ў‘.

Ц в режиме работы с сис≠темной шиной используетс€ как строб чтени€ номера ведомого контроллера прерываний. ѕри работе с Ў¬¬ используетс€ дл€ управлени€ состо€нием УвключенФ Ў‘.

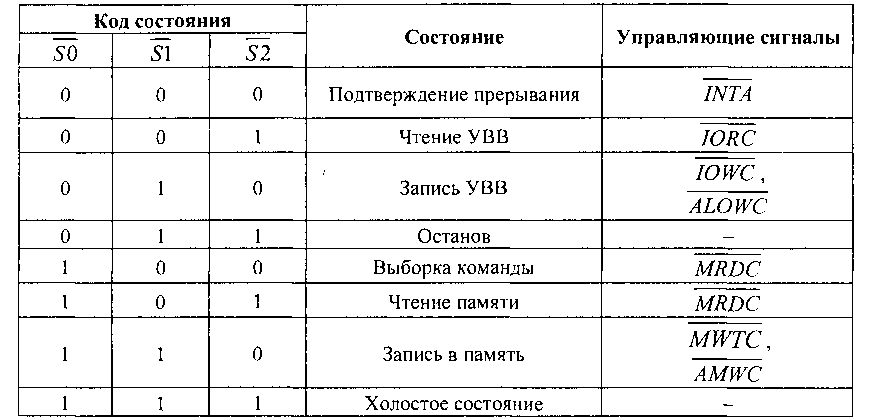

ќсновной информацией дл€ работы Ў €вл€етс€ код состо€ни€  ,

,  ,

,  , который декодируетс€ дешифратором (таблица 8.3.4.1).

, который декодируетс€ дешифратором (таблица 8.3.4.1).

“аблица 8.3.4.1.

¬ходные сигналы IO ¬, CEN,  определ€ют два режима работы контроллера Ц с —Ў и Ў¬¬. –ежим работы с —Ў устанавливаетс€ при IO ¬ = 0, при этом Ў формирует командные сигналы и сигналы управлени€ ALE, DEN, DT /

определ€ют два режима работы контроллера Ц с —Ў и Ў¬¬. –ежим работы с —Ў устанавливаетс€ при IO ¬ = 0, при этом Ў формирует командные сигналы и сигналы управлени€ ALE, DEN, DT /  фиксаторами адреса и Ў‘.

фиксаторами адреса и Ў‘.

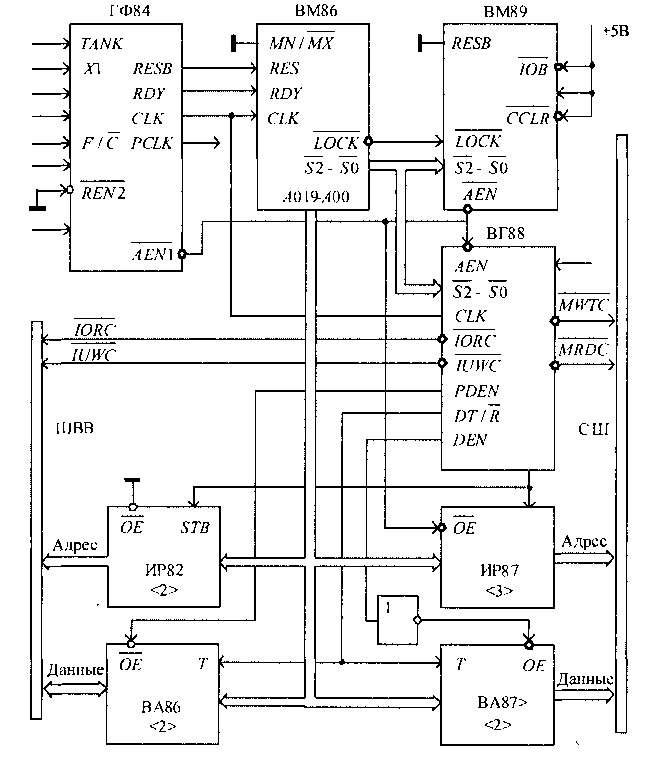

“ипова€ схема включени€ Ў в однопроцессорных системах на основе ÷ѕ ¬ћ86 в максимальном режиме показана на рисунке 8.3.4.6.):.

Ќа входах формируютс€ посто€нные значени€  = 0 и CEN = 1, которые разрешают выдачу командных сигналов и сигналов управлени€. Ќа выходе MCE/

= 0 и CEN = 1, которые разрешают выдачу командных сигналов и сигналов управлени€. Ќа выходе MCE/  при таком включении формируетс€ сигнал MCE. ќн используетс€ в ћѕ— с каскадированием контроллеров прерываний дл€ определени€ момента пе≠редачи номера ведомого контроллера, который запрашивает прерывание. —игнал ALE определ€ет момент фиксации адреса в буферных регистрах »–82. ¬ыходные

при таком включении формируетс€ сигнал MCE. ќн используетс€ в ћѕ— с каскадированием контроллеров прерываний дл€ определени€ момента пе≠редачи номера ведомого контроллера, который запрашивает прерывание. —игнал ALE определ€ет момент фиксации адреса в буферных регистрах »–82. ¬ыходные

сигналы DT /  и DEN используютс€ дл€ управлени€ работой Ў‘. —игнал DEN имеет высокий уровень, поэтому он должен инвертироватьс€ перед подачей на вход

и DEN используютс€ дл€ управлени€ работой Ў‘. —игнал DEN имеет высокий уровень, поэтому он должен инвертироватьс€ перед подачей на вход  микросхемы ¬ј86.

микросхемы ¬ј86.

—истемна шина в этом случае работает только с пам€тью и ÷ѕ получает доступ к ней по сигналу  от арбитра шин, а командные сигналы дл€ портов не используютс€.

от арбитра шин, а командные сигналы дл€ портов не используютс€.

–исунок8.3.4.6. “ипова€ схема подключени€ ¬√88 к ÷ѕ ¬ћ86

јрбитр шин

¬ многопроцессорной ћѕ— приоритетный доступ к —Ў обеспечивает јЎ. ¬ составе ћѕ 1810 имеетс€ микросхема 1810¬Ѕ89 (далее ¬Ѕ89), котора€ реализует функции арбитра.

¬ структуру јЎ вход€т (рисунок 8.3.4.7.):

Ј схема арбитра ј–Ѕ и дешифратор состо€ний ƒш—;

Ј схема управлени€ арбитражем —х” и блок шинного интерфейса Ѕ»‘.

¬ јЎ входы и сигналы на них имеют следующее функциональное назначение:

Ј  ,

,  ,

,  Ц сигналы состо€ний микропроцессора;

Ц сигналы состо€ний микропроцессора;

Ј CLK Ц вход синхронизации;

Ј  Ц вход системной синхронизации;

Ц вход системной синхронизации;

Ј  Ц начальна€ установка (сброс) јЎ;

Ц начальна€ установка (сброс) јЎ;

Ј  Ц блокирование —Ў;

Ц блокирование —Ў;

Ј RESB Ц выбор резидентной шины;

Ј  Ц выбор режима работы с Ў¬¬;

Ц выбор режима работы с Ў¬¬;

Ј  Ц сигнал совместного блокировани€ —Ў;

Ц сигнал совместного блокировани€ —Ў;

Ј AQST Ц любой запрос;

Ј SB/  Ц выбор системной или локальной шины.

Ц выбор системной или локальной шины.

|

|

–исунок 8.3.4.7. јрбитр шин ¬Ѕ89: a Ц структура; б Ц условное графическое обозначение

‘ункциональное назначение выходов и сигналов на них:

Ј  ,

,  ,

,  ,

,  Ц используютс€ дл€ организации схемы определени€ приоритетов;

Ц используютс€ дл€ организации схемы определени€ приоритетов;

|

|

|

Ј  Ц разрешение —Ў.

Ц разрешение —Ў.

¬ многопроцессорной ћѕ— с помощью јЎ организовывают следующие схемы обработки приоритетов: последовательные; параллельные с фиксированным приоритетом; параллельны с циклично измен€емыми приоритетами. ¬ многопроцессорной ћѕ— каждый ÷ѕ имеет свой јЎ.

¬ схеме последовательного арбитража приоритетный выход  арбитра с высшим приоритетом подключаетс€ ко входу

арбитра с высшим приоритетом подключаетс€ ко входу  арбитра с низшим приоритетом (рисунок 8.3.4.8.).

арбитра с низшим приоритетом (рисунок 8.3.4.8.).

–исунок 8.3.4.8. —хема последовательного арбитра

¬ход  арбитра с наивысшим приоритетом подключаетс€ к земле. ≈сли нескольким јЎ необходим доступ к —Ў, то сигнал

арбитра с наивысшим приоритетом подключаетс€ к земле. ≈сли нескольким јЎ необходим доступ к —Ў, то сигнал  = 0 у арбитра с наивыс≠шим приоритетом поступает на вход BPRN соседнего арбитра и запрещает ему захват шины.

= 0 у арбитра с наивыс≠шим приоритетом поступает на вход BPRN соседнего арбитра и запрещает ему захват шины.

—хема последовательного определени€ приоритета наиболее проста и не требует дополнительных микросхем. ќднако при таком соединении приоритет к последнему јЎ приходит с задержкой. ѕоскольку доступ к —Ў должен осуществл€тьс€ за один период сигнала  , то при частоте 10 ћ√ц можно последовательно соединить не более трех јЎ.

, то при частоте 10 ћ√ц можно последовательно соединить не более трех јЎ.

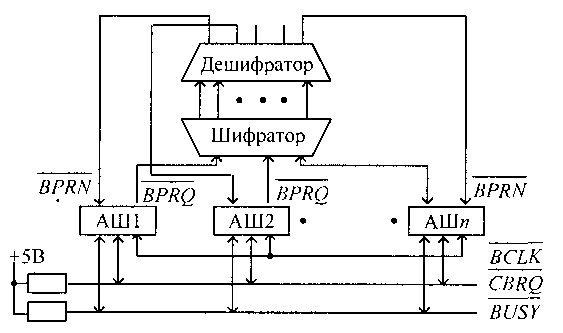

—хема параллельного определени€ приоритетов позвол€ет подключитьс€ к 16 арбитрам, дл€ их организации дополнительно используютс€ приоритетный шифратор и дешифратор (рисунок 8.3.4.9.).

–исунок8.3.4.9. —хема параллельного арбитража

—игнал с выхода запроса шины  каждого јЎ подаетс€ на вход приоритетного шифратора, который формирует двоичный код номера запроса с наивысшим приоритетом. Ётот код декодируетс€ дешифратором и поступает на вход

каждого јЎ подаетс€ на вход приоритетного шифратора, который формирует двоичный код номера запроса с наивысшим приоритетом. Ётот код декодируетс€ дешифратором и поступает на вход  выбранного јЎ, разреша€ ему захват шины.

выбранного јЎ, разреша€ ему захват шины.

—хема циклического определени€ приоритетов аналогична схеме параллельного арбитража, однако она имеет более сложные дополнительные микросхемы, с помощью которых приоритеты обрабатываютс€ по очереди.

¬о всех схемах арбитража имеетс€ лини€  , на которую выставл€етс€ низкий уровень арбитром, запрашивающим —Ў. ≈сли —Ў свободна, то арбитр, который получил доступ к шине, формирует сигнал

, на которую выставл€етс€ низкий уровень арбитром, запрашивающим —Ў. ≈сли —Ў свободна, то арбитр, который получил доступ к шине, формирует сигнал  = 0. ѕосле этого дл€ выбранного Ў разрешаетс€ выдавать на —Ў командные сигналы с Ў, а также адрес и данные соответственно с фиксаторов и формирователей.

= 0. ѕосле этого дл€ выбранного Ў разрешаетс€ выдавать на —Ў командные сигналы с Ў, а также адрес и данные соответственно с фиксаторов и формирователей.

¬ зависимости от конфигурации ћѕ— и сигналов на входах  , RESB можно задавать четыре режима работы с јЎ. —игнал на входе SYSB/

, RESB можно задавать четыре режима работы с јЎ. —игнал на входе SYSB/  выполн€ет вспомогательную роль Ц определени€ усл овий доступа к —Ў.

выполн€ет вспомогательную роль Ц определени€ усл овий доступа к —Ў.

–ежим работы с —Ў задают сигналы  = 1, RESB = 0, вход SB/

= 1, RESB = 0, вход SB/  игнорируетс€. ѕри этой комбинации сигналов ÷ѕ может подключитьс€ только к одной —Ў (рисунок8.3.4.10.).

игнорируетс€. ѕри этой комбинации сигналов ÷ѕ может подключитьс€ только к одной —Ў (рисунок8.3.4.10.).

ѕри исполнении цикла обращений к —Ў арбитр вначале получает приоритетный доступ, затем формирует сигнал  = 0 и подает его на схему шинного интерфейса —Ў1 (она содержит Ў, фиксатор адреса и формирователь данных). јрбитр удерживает —Ў и использует адресное пространство пам€ти (то есть, управл€етс€ сигналами

= 0 и подает его на схему шинного интерфейса —Ў1 (она содержит Ў, фиксатор адреса и формирователь данных). јрбитр удерживает —Ў и использует адресное пространство пам€ти (то есть, управл€етс€ сигналами  и

и  ).

).

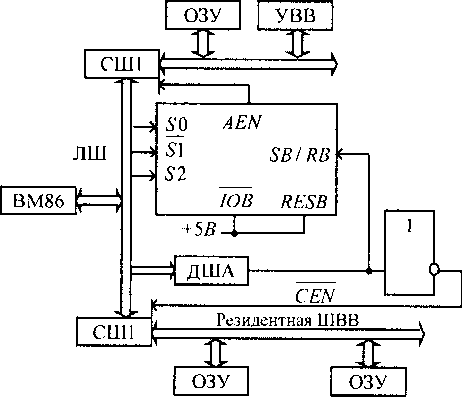

–ежим работы с —Ў пам€ти и резидентной Ў¬¬ задают сигналы IO¬ = RESB = 0 и SB/  = 0. ѕри этой комбинации сигналов ÷ѕ подключаетс€ к —Ў, котора€ обслуживает только пам€ть, и к резидентной Ў¬¬, котора€ выполн€ет обмен данными с периферией (рисунок 8.3.4.11.).

= 0. ѕри этой комбинации сигналов ÷ѕ подключаетс€ к —Ў, котора€ обслуживает только пам€ть, и к резидентной Ў¬¬, котора€ выполн€ет обмен данными с периферией (рисунок 8.3.4.11.).

–исунок8.3.4.10. —хема подключени€ јЎ к системной шине

–исунок8.3.4.10. —хема подключени€ јЎ к системной шине

|  –исунок8.3.4.11. —хема подключени€ јЎ к —Ў и резидентной Ў¬¬

–исунок8.3.4.11. —хема подключени€ јЎ к —Ў и резидентной Ў¬¬

|

¬ этом режиме сигнал  = 0 вырабатываетс€ арбитром только при необхо≠димости ÷ѕ обратитьс€ к пам€ти и наличии приоритетного разрешени€. ƒоступ к резидентной Ў¬¬ предоставл€етс€ процессору всегда при исполнении команд ввода IN и вывода OUT сигналом

= 0 вырабатываетс€ арбитром только при необхо≠димости ÷ѕ обратитьс€ к пам€ти и наличии приоритетного разрешени€. ƒоступ к резидентной Ў¬¬ предоставл€етс€ процессору всегда при исполнении команд ввода IN и вывода OUT сигналом  = 0. —хема —Ў2, котора€ св€зывает локальную шину с резидентной Ў¬¬, не содержит системного контроллера ¬√88. ≈го функции выполн€ет Ў в блоке —Ў1, установленный в режим IO¬ = 1. ѕри этом командные сигналы управлени€ пам€тью

= 0. —хема —Ў2, котора€ св€зывает локальную шину с резидентной Ў¬¬, не содержит системного контроллера ¬√88. ≈го функции выполн€ет Ў в блоке —Ў1, установленный в режим IO¬ = 1. ѕри этом командные сигналы управлени€ пам€тью  ,

,  ) поступают на —Ў, а управлени€ вводом-выводом (

) поступают на —Ў, а управлени€ вводом-выводом ( ,

,  ), а также INTA Ч на резидентную Ў¬¬.

), а также INTA Ч на резидентную Ў¬¬.

ƒетальна€ схема расширенного ÷ѕ в режиме обслуживани€ —Ў и резидентной Ў¬¬ показана на рисунке8.3.4.12.

–ежим работы с системной и резидентной шинами задают сигналами

= RESB = 1. ќн используетс€ в ћѕ— с системной и резидентной шинами и в каждой из них обеспечиваетс€ доступ к пам€ти и ”¬¬ (рисунок8.3.4.13).

= RESB = 1. ќн используетс€ в ћѕ— с системной и резидентной шинами и в каждой из них обеспечиваетс€ доступ к пам€ти и ”¬¬ (рисунок8.3.4.13).

|

|

|

—игнал  , который обеспечивает доступ к —Ў, вырабатываетс€ при SB/

, который обеспечивает доступ к —Ў, вырабатываетс€ при SB/  = 1 (при условии, что јЎ получил разрешение на доступ). ƒл€ формирова≠ни€ сигналов доступа к системной SB /

= 1 (при условии, что јЎ получил разрешение на доступ). ƒл€ формирова≠ни€ сигналов доступа к системной SB /  = 1 или к резидентной SB/

= 1 или к резидентной SB/  = 0 шине используют дешифратор адреса ƒЎј, подключенный к —Ў.

= 0 шине используют дешифратор адреса ƒЎј, подключенный к —Ў.

–ежим работы с —Ў пам€ти, резидентной шиной и резидентной Ў¬¬ задают сигналы  0 и RESB = 1. Ёту комбинацию сигналов используют в ћѕ—, где нар€ду с —Ў, котора€ обеспечивает доступ только к пам€ти, имеетс€ две резидентные шины. ќдна из них выполн€ет доступ как к пам€ти, так и к ”¬¬, втора€ Ц только к ”¬¬.

0 и RESB = 1. Ёту комбинацию сигналов используют в ћѕ—, где нар€ду с —Ў, котора€ обеспечивает доступ только к пам€ти, имеетс€ две резидентные шины. ќдна из них выполн€ет доступ как к пам€ти, так и к ”¬¬, втора€ Ц только к ”¬¬.

–исунок8.3.4.12—хема ÷ѕ в режиме обслуживани€ —Ў и резидентной Ў¬¬

–исунок8.3.4.13—хема использовани€ јЎ с системной и резидентной шинами