ИСПОЛЬЗОВАНИЕ СИСТЕМЫ DESIGNLAB ДЛЯ МОДЕЛИРОВАНИЯ АНАЛОГОВЫХ И ЦИФРОВЫХ УСТРОЙСТВ

Моделирование активных аналоговых устройств

Для моделирования аналогового устройства необходимо выполнить графический ввод компонентов схемы в программе Schematics, используя различные библиотеки компонентов:

- ANALOG.slb — для пассивных элементов (R, L, С);

- BIPOLAR.slb — для биполярных транзисторов;

- EDIODE.slb — для диодов;

- JFET.slb — для полевых транзисторов;

- PORT.slb — для заземления (компонент AGND — для аналоговых устройств).

Следует сказать, что в демо-версии системы DesignLab присутствуют не все перечисленные библиотеки компонентов. Так модель транзистора для схемы усилителя размещена в библиотеке EVAL.slb. Для питания схемы по постоянному току обычно используется компонент VDC (источник постоянного напряжения), расположенный в библиотеке SOURCE.slb. В качестве атрибутов источника VDC задается величина постоянного напряжения DC. После ввода компонентов схемы моделируемого устройства необходимо ввести источник сигнала, расположенный также в библиотеке SOURCE.slb.

Ввод источников аналоговых сигналов

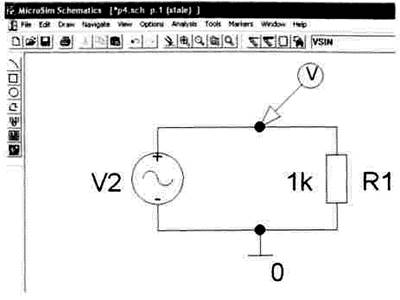

Задание источника сигналов осуществляется в зависимости от типа активного устройства и от того, какие его характеристики необходимо исследовать. Так, например, для моделирования временных и частотных характеристик устройств в качестве источника сигналов следует выбирать компонент VSIN (источник синусоидального напряжения). Рассмотрим параметры источника сигнала VSIN для схемы, представленной на рис. 2-1, а.

а б

Рис. 2-1. Схема для исследования параметров (а)и окно с атрибутами компонента V2 (б)

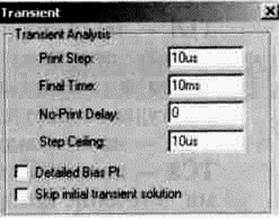

В окне Analysis Setup зададим параметры директивы моделирования схемы в режиме анализа переходных процессов (Transient) таким образом, чтобы на графике было видно 10—15 периодов колебания.

Рис. 2-2. Окно задания параметров директивы моделирования Transient

Последовательно изменяя атрибуты источника сигнала VAMPL = 5, FREQ = 5k, TD = 2ms, DF = 30, PHASE = 180 и запуская каждый раз режим моделирования схемы с вновь заданным значением атрибута, можно наблюдать изменение временного представления сигнала источника VSIN.

а б в

Рис. 2-3. Условные графические обозначения источников сигналов: а - VPULSE, б - VEXP и в - VPWL_FILE

Для исследования процессов прохождения различных сигналов через аналоговые устройства возможно использование следующих источников сигналов: VPULSE - импульсный источник напряжения (рис. 2-3, а), VEXP - экспоненциальный источник напряжения (рис. 2-3, б)и VPWL_FILE - источник напряжения, заданный в файле (рис. 2-3, в),атрибуты которых, обязательные для заполнения, представлены ниже. В скобках указаны ориентировочные значения атрибутов. Атрибуты источника сигнала VPULSE:

АС — амплитуда напряжения при анализе в частотной области (1);

V1 — минимальное напряжение (0);

V2 — максимальное напряжение (2);

TD — задержка (0);

TR — длительность переднего фронта (0);

TF — длительность заднего фронта (0);

PW — длительность импульса (lm);

PER — период повторения импульсов (4т).

Заменив в предыдущей схеме источник сигнала VSIN на PULSE и заполнив обязательные атрибуты, выполните моделирование схемы в режиме анализа переходных процессов. Последовательно изменяя атрибуты источника сигнала V1 = 2, V2 = 5, TD = 2ms, TR = 0,2m, TF = 0,5m, PW = 2m, PER = 5m и запуская каждый раз режим моделирования схемы с вновь заданным значением атрибута, но наблюдать изменение временного представления сигнала источника VPULSE.

Атрибуты источника сигнала VEXP:

АС — амплитуда напряжения при анализе в частотной области (1);

V1 — минимальное напряжение (0);

V2 — максимальное напряжение (1);

TD1 — задержка (0);

ТС1 — постоянная времени переднего фронта — время, в течение которого мгновенное значение амплитуды возрастает до уровня 0.63*V2 (0.2m);

TD2 — начало заднего фронта (2m);

ТС2 — постоянная времени заднего фронта — время, в течение которого мгновенное значение амплитуды убывает до уровня V2-0,63*V2 (0,2m).

Заменив в предыдущей схеме источник сигнала VPULSE на VEXP и заполнив обязательные атрибуты, выполните моделирование схемы в режиме анализа переходных процессов. Последовательно изменяя атрибуты источника сигнала V1 = 1, V2 = 3, TD1 = 1ms, TC1 = 0,3m, TD2 = 4m, TC2 = 0,3m и запуская каждый раз моделирование схемы с вновь заданным значением атрибута, можно наблюдать изменение временного представления сигнала источника VEXP.

Атрибуты источника сигнала VPWL_FILE:

АС — амплитуда напряжения при анализе в частотной области (1);

TSF — масштабный множитель по времени (1);

VSF — масштабный множитель по уровню (1);

FILE — имя файла (primer.txt);

REPEAT_VALUE — количество циклов повторения (3).

Имя файла для источника сигнала VPWL_FILE должно состоять из латинских букв (расширение txt). Данные в файле необходимо представить в следующем формате:

(<отсчет времени 1>, <отсчет амплитуды 1>)

(<отсчет времени 2>, <отсчет амплитуды 2>)

………………………………………………..

(<отсчет времени N>, <отсчет амплитуды N>)

Файл с таким источником сигнала можно создать в программе «Блокнот» и затем поместить в папку, где расположен файл с моделируемой схемой. Пример файла с источником сигнала представлен на следующем рисунке.

Рис. 2-4. Окно программы «Блокнот» с файлом источника сигнала

Пример схемы с таким источником сигнала, а также сам файл источника сигнала расположены в каталоге схем. Загрузите схему p4.sch и выполните моделирование во временной области, убедитесь в том, что созданный из файла источник сигнала действительно воспроизводит отсчеты сигнала в заданные моменты времени.

Следует сказать, что в системе DesignLab имеется встроенный редактор входных сигналов Stimulus Editor, позволяющий создавать аналоговые и цифровые сигналы непосредственно с помощью курсора мыши. Эти сигналы записываются в файл и включаются в схему с помощью источника сигналов VPWL_FILE, рассмотренного выше.

После ввода источника сигнала схема аналогового устройства проверяется на отсутствие «плавающих» (неподключенных) узлов, в контрольные точки устанавливаются маркеры, и выполняется моделирование.