ВСТУП

Методичні вказівки до виконання лабораторних робіт з дисциплін "Цифрові пристрої"та"Схемотехніка радіоелектронних апаратів" призначені для студентів радіотехнічного факультету НТУУ "КПІ" очної та заочної форм навчання напрямків 6.050901 «Радіотехніка» та 6.050902 «Радіоелектронні апарати».

Методичні вказівки містять

- опис спеціалізованого обладнання, на базі якого виконується практична частина кожної роботи;

- програми виконання робіт;

- особливості практичної реалізації та ладнання цифрових пристроїв;

- перелік теоретичного матеріалу, який має бути засвоєним для успішного виконання робіт, наводиться безпосередньо при описі кожної лабораторної роботи, наводяться базові відомості з того чи іншого питання, що має сприяти цілеспрямованому вивченню та поглибленому засвоєнню необхідного матеріалу;

- вказівки з виконання робіт;

- протоколи до виконання лабораторних робіт;

- необхідні довідкові дані.

МЕТА ТА ОСНОВНІ ЗАВДАННЯ ЛАБОРАТОРНИХ РОБІТ

Мета лабораторних робіт - набуття студентами навичок з розробки принципових електричних схем цифрових пристроїв, їх практичної реалізації і ладнання.

Кожна з лабораторних робіт включає етапи:

- побудова функціональної схеми, яка реалізує задані функції;

- розробка електричної принципової схеми цифрового пристрою (ЦП) з використанням мікросхем, заданих типів;

- збирання та ладнання макету ЦП на базовому шасі;

- підтвердження правильності функціонування ЦП та оформлення результатів роботи.

При оформленні звіту за результатами лабораторної роботи, згідно встановленої форми (див. додаток 1 – 5), мають бути наведені

- мета роботи та постановка задачі;

- матеріали синтезу функціональної схеми ЦП;

- принципова електрична схема ЦП, виконана на мікросхемах, які були використані при виконанні роботи;

- висновки, в яких слід навести результати випробування ЦП на предмет його відповідності технічному завданню.

Для успішного виконання лабораторних робіт необхідно засвоєння студентом відповідного теоретичного матеріалу. Обсяг необхідного теоретичного матеріалу вказується при описі кожної лабораторної роботи. Узагальнений перелік рекомендованої літератури наведено у відповідному розділі в кінці методичних вказівок). Для побудови електричної принципової схеми на підставі функціональної схеми ЦП, необхідно мати відповідні довідкові відомості про мікросхеми, які планується використати при виконанні лабораторної роботи (типи мікросхем задаються викладачем). Дані для мікросхем, які використовуються при виконанні лабораторних робіт, наведені в додатку 6 та в тексті лабораторної роботи №5.

ПРАВИЛА ТЕХНІКИ БЕЗПЕКИ ПРИ ВИКОНАННІ ЛАБОРАТОРНИХ РОБІТ

В учбовій лабораторії при виконанні лабораторних робіт використовується робоча напруга небезпечна для життя (±5 В для живлення лабораторних макетів та 24 В змінного струму для живлення паяльників). Але наявність високої (220 В) напруги на розподільних електрощитах, використання паяльників, робоча температура яких перевищує 200 оС, обумовлює необхідність виконання певних правил техніки безпеки та виробничої санітарії з метою запобігання нещасних випадків, надання шкоди здоров'ю (як власному так і оточуючих).

1. Забороняється студентам самостійно виконувати будь-які вмикання на розподільних електрощитах або заміну запобіжників.

2. Вмикання лабораторного макета після збирання схеми можливо лише в присутності керівника робіт.

3. Збирання схеми, внесення будь-яких змін до неї слід виконувати лише при вимкненому електроживленні. Виконувати будь-які перемикання в схемах, що знаходяться під напругою забороняється.

4. Робоче місце в процесі виконання робіт має бути організоване - вільне від сторонніх предметів (книг, конспектів та ін.), невикористаних монтажних провідників тощо.

5. На робочому місці має знаходитись не менше двох осіб. Виконувати лабораторні роботи поодинці заборонено.

6. При збиранні пристрою на базовому шасі необхідно уникати взаємного торкання монтажних провідників, щоб не допускати режимів короткого замикання, які можуть призвести до аварійного стану пристрою, відмови комплектуючих елементів або базового шасі.

7. Недопустимо вмикати в розетки електромережі будь-які провідники без штепсельних вилок.

8. При залужуванні кінців монтажних провідників та їх припаюванні до контактних елементів базового шасі необхідно бути особливо обережним, щоб запобігти розбризкуванню розплавленого припою.

9. Під час паяння відбувається виділення шкідливих для здоров'я речовин, тому необхідно слідкувати, щоб приміщення, де відбуваються лабораторні роботи, провітрювалось.

ОПИС ОБЛАДНАННЯ, ЩО ВИКОРИСТОВУЄТЬСЯ ПРИ ВИКОНАННІ ЛАБОРАТОРНИХ РОБІТ

Практична реалізація розробленого ЦП здійснюється на базовому шасі.

Базове шасі - основний технічний засіб, який використовується при виконанні кожної лабораторної роботи. Він забезпечує можливість збирання та налагодження ЦП, електрична принципова схема якого має бути отримана студентом на етапі підготовки до виконання роботи.

Базове шасі (БШ) являє собою пристрій, призначення якого полягає в тому, щоб забезпечити:

- кріплення мікросхем,

- з'єднання виводів мікросхем між собою та з джерелом живлення згідно принципової схеми ЦП,

- можливість налагодження ЦП,

- контроль функціонування ЦП.

Загальний вигляд базового шасі наведено на рис. 1.

Базове шасі складається з корпусу I (рис. 1); монтажного поля II (рис. 2); клемної групи для підключення джерела живлення III (рис. 3); набірного поля IV (рис. 4); елементів керування тактовим генератором V (рис. 5).

Рис. 1. Загальний вигляд базового шасі.

Рис. 1. Загальний вигляд базового шасі.

|

Корпус БШ виконаний з металу і є несучою основою усього пристрою. Всередині корпусу розміщено генератор імпульсів та здійснено необхідні з'єднання окремих елементів БШ, що забезпечує можливість його багаторазового використання та реалізацію будь-якого ЦП з числа запропонованих для виконання лабораторних робіт. Монтажне поле забезпечує можливість виконання всіх операцій з монтажу, налагодження та тестування ЦП.

На монтажному полі розміщуються (див. рис. 2):

- панелі 1 (4 шт.) та 2 (2 шт.) для встановлення мікросхем, причому різновид панелей забезпечує можливість встановлення мікросхем, що розміщені у різних корпусах, а саме: БІР-14 та БІР-16, відповідно (наявність на монтажному полі додаткової панелі, обумовлена використанням даного БШ в лабораторних роботах з інших курсів);

- світлодіоди 3 (4 шт.) та 7 (1 шт.);

- контактні елементи 4, 5, 6, 8; при цьому: контактні елементи 4 приєднані до виводів світлодіодів 3 та мають відповідне позначення; контактні елементи 5 приєднані до відповідних виводів панелей 1 та 2; контактні елементи 6 приєднані до перемикачів задавання логічних рівнів (розміщених на набірному полі); контактний елемент 8 приєднаний до виходу вмонтованого в БШ генератора імпульсів.

2 3 4

Рис. 2. Монтажне поле.

Рис. 2. Монтажне поле.

|

Контактні елементи 5 розміщуються на БШ групами в безпосередній близькості до відповідних панелей. Слід звернути увагу, що кількість цих контактних елементів в кожній групі на два менше кількості виводів відповідних панелей. Це обумовлено тим, що виводи, на які подається напруга від джерела живлення, приєднані до клемної групи III безпосередньо всередині корпусу БШ. Клемна група III розміщена на одній з бокових поверхонь БШ, її призначення і порядок використання зрозумілі з рис. 3.

Світлодіоди 3 (загальною кількістю 4 шт.) призначені для контролю сигналу (0 чи 1) на входах або виходах логічних елементів (складових) зібраного ЦП та використовуються при його налагодженні і тестуванні.

Рис. 3. Клемна група для підключення джерела живлення.

Контактні елементи 6 приєднані до перемикачів задавання логічних рівнів, які входять до складу набірного поля IV і розміщені на одній з бокових поверхонь БШ. Розміщення та порядок використання перемикачів набірного поля зрозумілі з рис.4.

Рис.4. Набірне поле.

Перемикачі набірного поля надають можливість незалежно встановити на кожному контактному елементі, що входить до групи контактних елементів 6, напругу низького або високого рівня, що відповідає логічним рівням "0" або "1", тобто виступають як своєрідний генератор двійкового коду, необхідний, як при ладнанні, так і при тестуванні зібраного ЦП.

До складу БШ входить генератор імпульсів, вихід якого приєднано до контактного елементу 8 та світлодіоду 7. Елементи керування цього генератора розміщені на одній з бокових панелей БШ (див. рис. 5).

Рис. 5. Елементи керування генератором імпульсів.

До складу елементів керування генератором імпульсів входять перемикач I, призначений для вибору режиму роботи (генерація послідовності імпульсів чи поодиноких імпульсів при ручному запуску) та кнопка II, призначена для ручного запуску генератора в режимі генерації поодиноких імпульсів.

Монтаж ЦП полягає в з’єднанні виводів мікросхем між собою та з іншими складовими, згідно розробленої принципової схеми та здійснюється перемичками, кінці яких підпаюють до відповідних контактних елементів.

ТИПОВІ СИТУАЦІЇ, ЩО ВИНИКАЮТЬ ПРИ РЕАЛІЗАЦІЇ ЦИФРОВИХ ПРИСТРОЇВ НА СТАНДАРТНИХ ІНТЕГРАЛЬНИХ СХЕМАХ

Розроблена функціонально-логічна схема ЦП має бути реалізована на базі набору стандартних інтегральних схем (ІС) тої чи іншої серії, або на базі набору бібліотечних елементів тієї чи іншої великої (надвеликої) інтегральної схеми (ВІС або НВІС) з програмованою структурою. В обох випадках можлива ситуація, коли наявні елементи і елементи потрібні для реалізації схеми не співпадають, як за кількістю, так і за можливостями виконання необхідних функцій.

Типовими ситуаціями є наявність в корпусах стандартних ІС "зайвих" (тобто таких, що не використовуються в даному випадку) логічних елементів, входів, або, навпаки, кількість входів мала, їх навантажувальна спроможність недостатня. Детальна інформація, щодо вирішення вказаних проблем наведена в [2, с. 64-72]. Нижче наводяться лише ті відомості, знання яких необхідне для успішного виконання лабораторних робіт.

Режими невикористаних входів.

Питання про режими "зайвих" входів вирішується з урахуванням конкретного типу схемотехнології, що використовується.

Наприклад, необхідно отримати кон'юнкцію (або її інверсію) п'яти змінних. В стандартних серіях не має відповідних елементів, що мають 5 входів. В цьому випадку доводиться використати елемент що має вісім входів, в якому виявляється три "зайві" входи. Принципово можливо:

- не звертати уваги на "зайві" входи (тобто залишити їх розімкненими);

- приєднати "зайві" входи до задіяних;

- подати на "зайві" входи якісь константи.

З точки зору логічних операцій всі три вказані можливості правомірні. Але, якщо взяти до уваги особливості тієї чи іншої схемотехнології, то вибір варіанту стає визначеним.

Для елементів, які виготовляються за технологіями КМОН або ТТЛ(Ш), невикористані входи розімкненими не залишають. Для елементів, виготовлених за КМОН-технологією, це сувора заборона, бо в цих елементах великі значення вхідних опорів і, відповідно, на розімкнених входах легко наводяться паразитні потенціали, які можуть змінити роботу схеми. Для елементів, виготовлених за ТТЛ(Ш)-технологією суворої заборони залишати входи розімкненими немає, але робити це небажано, так як при цьому погіршуються параметри швидкодії елемента. Приєднання "зайвих" входів до задіяних для КМОН и ТТЛ(Ш) елементів принципово можливе, але небажане, бо призводить до підвищення навантаження на джерело сигналу, що, в свою чергу, веде до зниження його швидкодії.

Таким чином, для елементів, виготовлених за технологіями КМОН або ТТЛ(Ш) проблема невикористаних входів вирішується шляхом приєднання їх до констант (логічним одиницям або нулям) таким чином, щоб запобігти зміни роботи схеми для задіяних входів. При цьому рівні напруги логічної "1" та логічного "0" для КМОН елементів співпадають з рівнями напруги джерела живлення та загальної шини ("землі"), до яких і приєднують невикористані входи. Для ТТЛ(Ш) елементів рівень "1" на 1,5 - 2 В нижчий за рівень напруги джерела живлення, тому для запобігання пробою незадіяні входи приєднують до джерела живлення через резистор, величина опору якого (звичайна рекомендація) повинна складати 1 кОм, причому до одного резистору дозволяється приєднати до 20 входів.

ЛАБОРАТОРНА РОБОТА №1

Вивчення особливостей роботи базових логічних елементів

Мета роботи.

Вивчення особливостей роботи та порівняльний аналіз базових логічних елементів різних серій.

Постановка задачі.

В середовищі комп’ютерного моделювання вивчити роботу базових логічних елементів. Зняти основні характеристики. Провести порівняльний аналіз.

1.1. Короткі теоретичні відомості

Визначення високого та низького рівнів сигналу.

Високий рівень вхідної напруги ( )– мінімальний рівень напруги на вході, що являє собою логічну 1. Будь-яке значення напруги нижче даного рівня не входить в діапазон високого рівня сигналу для даної логічної схеми.

)– мінімальний рівень напруги на вході, що являє собою логічну 1. Будь-яке значення напруги нижче даного рівня не входить в діапазон високого рівня сигналу для даної логічної схеми.

Низький рівень вхідної напруги ( )– максимальний рівень напруги на вході, що являє собою логічний 0. Будь-яке значення напруги вище даного рівня не входить в діапазон низького рівня сигналу для даної логічної схеми.

)– максимальний рівень напруги на вході, що являє собою логічний 0. Будь-яке значення напруги вище даного рівня не входить в діапазон низького рівня сигналу для даної логічної схеми.

Високий рівень вихідної напруги ( )– мінімальний рівень напруги на виході логічної схеми, що являє собою логічну 1 при заданому навантаженню.

)– мінімальний рівень напруги на виході логічної схеми, що являє собою логічну 1 при заданому навантаженню.

Низький рівень вихідної напруги ( )– максимальний рівень напруги на виході логічної схеми, що являє собою логічний 0 при заданому навантаженні.

)– максимальний рівень напруги на виході логічної схеми, що являє собою логічний 0 при заданому навантаженні.

Завадостійкість.

Рис.1.1.1. Завадостійкість логічної схеми.

На рис.1.1.1 проілюстровано діапазон значень напруг, що може приймати сигнал на виході логічної схеми. Будь-яке значення більше, ніж  , розглядається як логічна 1, значення нижче

, розглядається як логічна 1, значення нижче  – як логічний 0. В нормальному режимі роботи на виході логічної схеми не повинні з’являтися напруги з невизначеного діапазону. Також на даному рисунку зображено вимоги до значень напруг на вході логічної схеми. Логічна схема на будь-яке значення напруги, що перевищує

– як логічний 0. В нормальному режимі роботи на виході логічної схеми не повинні з’являтися напруги з невизначеного діапазону. Також на даному рисунку зображено вимоги до значень напруг на вході логічної схеми. Логічна схема на будь-яке значення напруги, що перевищує  реагує як на логічну 1, а на будь-яке значення, що нижче

реагує як на логічну 1, а на будь-яке значення, що нижче  – як на логічний 0. Значення напруги в невизначеному діапазоні призведуть до непередбачуваної реакції схеми.

– як на логічний 0. Значення напруги в невизначеному діапазоні призведуть до непередбачуваної реакції схеми.

Існує поняття завадостійкості схеми – значення напруги, викликане електричним шумом, яке схема може витримати без погіршення працездатності.

Запас завадостійкості для одиничного стану:

.

.

Запас завадостійкості для нульового стану:

.

.

В даній лабораторній роботі розглянемо базовий логічний елемент (ЛЕ) ТТЛ та ЛЕ, що виготовлені за КМОН технологією.

Елементи транзисторно-транзисторної логіки ТТЛ.

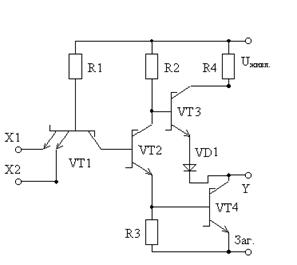

Рис. 1.1.2. Базовий елемент ТТЛ – І-НЕ.

Базовий елемент логічних схем ТТЛ – елемент І-НЕ,зображений на рис.1.1.2. Характеристики входів ТТЛ обумовлені внутрішньою структурою багатоемітерного транзистора VT1. Даний транзистор еквівалентний групі діодів, кожен з яких замінює перехід база- емітером. При подачі прямого зміщення на один або обидва емітера відбувається відпирання транзистора VT1. І навпаки, транзистор виявиться закритим, якщо подати на всі емітери одночасно зворотне зміщення. Багатоемітерні транзистори можуть мати до 8 емітерів, а ЛЕ – відповідно таку ж кількість входів.

Для пояснення роботи схеми базового елементу ТТЛ І-НЕ замінимо в схемі (рис.1.1.2) багатоемітерний транзистор його діодним еквівалентом (рис.1.1.3). Отримаємо еквівалентну схему елементу І-НЕ на рис.1.1.4.

Рис. 1.1.3. Діодний еквівалент транзистора

Рис. 1.1.4. Базовий елемент ТТЛ – І-НЕ з діодним еквівалентом транзистору VT1.

Розглянемо приклад, якщо на обидва входи X1 та X2 подати +5В (тобто логічні одиниці). Такий рівень напруги на катодах діодів VD2 і VD3 вимкне обидва діоди, тому вони практично не будуть пропускати через себе струм. Напруга живлення (+5В) призведе до появи струму через опір R1 та діод VD4 на базі транзистора VT2, який при цьому відкриється. Струм з емітера цього транзистора потече на базу VT4 і також ввімкне його. Струм з колектора транзистора VT2 призведе до падіння напруги на опорі R2, що зменшить напругу на колекторі VT2 до недостатнього значення для включення транзистора VT3.

Напруга на колекторі VT2 приблизно рівна 0.8 В. Вона складається з потенціалу 0.7 В на емітері транзистора VT2 відносно землі (викликаний прямим зміщенням на переході Е-Б транзистору VT4) і потенціалу 0.1 В колектору VT2 відносно його емітера (викликаний напругою К-Е). Ця напруга 0.8 В буде і на базі транзистора VT3. Його недостатньо для прямого зміщення переходу Е-Б транзистора VT3 та діода VD1. Сам діод VD1 запобігати прямому зміщенню на переході Е-Б транзистору VT3. Якщо на виході Y низький рівень напруги, транзистор VT4 відкривається і фактично замикає точку Y на землю.

Якщо ж, наприклад, на один з входів X1 подати напругу живлення, а другий X2 приєднати до землі. Нульовий рівень на ньому призведе до прямого зміщення діода VD3, а це, в свою чергу, до протікання струму від джерела +5В через опір R1, діод VD3 та вивід X2 на землю. Падіння напруги на діоді VD3 забезпечує рівень напруги величиною 0.7В в точці А. Цієї напруги недостатньо для прямого зміщення діоду VD4 і переходу Е-Б VT2, тобто вони залишаються закритими.

Оскільки транзистор VT2 закритий, то на базу транзистора VT4 струм не поступає і він також буде закритим. На колекторі VT2 струм також не протікає, тому на базі транзистора VT3 значення напруги виявиться достатньо великим для прямого зміщення транзистора VT3 та діоду VD1 і VT3 – відкритий. Оскільки між точкою Y та землею навантаження не підключене (транзистор VT4 закритий), то значення напруги буде розраховуватись як різниця між напругою живлення +5В та падіннями напруги по 0.7 В на діоді VD1 та переході Е-Б транзистора VT3 ( ). Маємо високий рівень напруги на виході схеми.

). Маємо високий рівень напруги на виході схеми.

Цей рівень сигналу буде зменшуватися при підключенні навантаження, оскільки воно буде зменшувати струм емітера VT3, що призведе до появи струму бази, що тече через опір R2, на якому падіння напруги збільшується.

Розглянемо випадок, якщо хоча б на один вхід транзистора VT1 не подати сигнал («залишити у повітрі»). Напруга живлення (+5В) призведе до появи струму через опір R1 та діод VD4 на базі транзистора VT2, який при цьому відкриється. Далі схема працює так само, як і у випадку, коли на обидва входи подали напругу живлення +5В. Отже, з цього можна зробити висновок, що «залишений у повітрі» вхід схеми ТТЛ еквівалентний високому рівню напруги на ньому, тобто значенню логічної одиниці.

Всі мікросхеми ТТЛ мають напругу живлення 5В. Напруга низького рівня (логічний нуль) для всіх мікросхем ТТЛ складає 0.4В, напруга високого рівня (логічна одиниця) 2.4В.

Комплекс серій мікросхем ТТЛ включає серії 130, К131 (імпортні аналоги – серії 54H, 74H), серії 133, К155 (54, 74), серії К134, КP134 (54L, 74L).

На зміну мікросхемам ТТЛ прийшли мікросхеми ТТЛШ серій 530, К531 (54S, 74S), 533, 555 (54LS, 74LS), К1531 (74F), К1533 (74ALS). Останні дві серії відрізняються значно меншим енергоспоживанням.

Елементи транзисторно-транзисторної логіки на базі транзисторів Шотки ТТЛШ.

Відмінність елементу ТТЛ від ТТЛШ полягає в тому, що в транзисторах другого присутні діоди Шотки, які ввімкнені в транзистор між базою та колектором, обмежуючи насичення транзистора, що забезпечує вищу швидкодію та менше енергоспоживання.

Рис.1.1.5. Транзистор Шотки

Рис.1.1.6. Базовий елемент ТТЛШ – І-НЕ.

Всі мікросхеми ТТЛ мають напругу живлення 5В. Напруга низького рівня (логічний нуль) для всіх мікросхем ТТЛШ складає 0.5В, напруга високого рівня (логічна одиниця) 2.7В.

Елементи на КМОН-транзисторах (КМОН – комплементарна метал-оксид-напівпровідник технологія).

Базовим логічним елементом на КМОН є елемент АБО-НЕ.

Ці мікросхеми виділяються серед інших найнижчим споживанням потужності від джерела живлення. Основу таких мікросхем складає ключовий каскад.

Керування польовим транзистором відбувається за допомогою напруги заслін-витік. Напруга заслін-витік  – вхідна напруга, що керує опором між стоком та витоком (тобто опором каналу). Якщо

– вхідна напруга, що керує опором між стоком та витоком (тобто опором каналу). Якщо  , то транзистор – закритий. Якщо

, то транзистор – закритий. Якщо  , тобто значенню напруги живлення, то транзистор – відкритий. (Порогове значення для відкриття транзистора 1.5 В). Отже, КМОН транзистор можна розглядати як еквівалентний ключ, що керується напругою заслін-витік.

, тобто значенню напруги живлення, то транзистор – відкритий. (Порогове значення для відкриття транзистора 1.5 В). Отже, КМОН транзистор можна розглядати як еквівалентний ключ, що керується напругою заслін-витік.

В схемах КМОН використовуються польові транзистори n-типу та p-типу. Функціонування цих двох типів транзисторів є аналогічним, за виключенням того, що p-канальний польовий транзистор використовує для роботи напругу від'ємної полярності.

Якщо на обидва входи логічного елемента подати сигнал низького рівня (лог.0), то транзистори VT1, VT4 (з каналом n -типу) будуть в закритому стані ( ), а транзистори VT3, VT2 (з каналом p-типу) – у відкритому (

), а транзистори VT3, VT2 (з каналом p-типу) – у відкритому ( ). На виході елементу встановиться напруга високого рівня (лог.1).

). На виході елементу встановиться напруга високого рівня (лог.1).

Якщо хоча б на одному з входів елемента, наприклад X1, буде присутня напруга високого рівня, то транзистор VT1 буде у відкритому стані, а VT2– у закритому. При цьому напруга на X2 відповідає рівню логічного нуля, тоді VT4 – закритий, напруга затвор-витік має значення високого рівня, тоді VT3 – відкритий. На виході встановиться напруга низького рівня.

В даній схемі логічного елементу для встановлення на виході значення напруги високого рівня є необхідним протікання струму через транзистори VT2 та VT3, тобто вони мають бути відкритими. У випадку, якщо хоча б один з них є закритим – на виході схеми встановлюється значення напруги низького рівня.

Для схем ЛЕ, виготовлених за технологією КМОН, заборонено залишати невикористані входи ЛЕ непідключеними, так як поведінка ІС, в даному випадку, є непередбачуваною.

Рис.1.1.7. Базовий елемент АБО-НЕ на КМОН.

Елементи на КМОН-ключах характеризуються підвищеною завадостійкістю: допустима напруга статичної завади рівна половині напруги живлення. Однак такі ІМС вирізняються підвищеною чутливістю до статичної напруги, через високий вхідний опір. Для захисту від впливу статичної напруги в структуру ІМС вводяться діодно-резистивні кола. Основна область застосування мікросхем КМОН типу - це цифрові пристрої невисокої швидкодії з обмеженим енергоресурсом. Швидкодія КМОН мікросхем характеризується частотою перемикання до 3МГц.

За КМОН технологією виготовлені мікросхеми серії К176, 164 (4000), К561, 564 (4000A), КР1561 (4000B) (в дужках вказані імпортні аналоги).

Мікросхеми вказаних серій працездатні при напругах живлення від 3 до 15В. Ця особливість вказаних ІМС дозволяє суттєво знизити вимоги до джерел живлення по відношенню до їх потужності та якості фільтрації і за рахунок цього отримати значний виграш в масі та розмірах цифрових пристроїв. Деякі серії, наприклад, К176, вимагають напруги живлення 9В, але вони також спроможні працювати при зміні напруги живлення в значних межах.

На сьогоднішній день є тенденція витеснення ТТЛ логічних елементів логічними елементами, виготовленими за КМОН технологією.

Табл.1.1.1. Довідкові дані деяких мікросхем вітчизняного виробництва.

| Тип логіки | Серія ІМС |  , напруга живлення , напруга живлення

|  ,

відповідає логічній 1 на виході ,

відповідає логічній 1 на виході

|  відповідає логічній 1 на виході

відповідає логічній 1 на виході

|

| ТТЛШ | К1531, К531, К1533, К555 | 2.7 | 0.5 | |

| ТТЛ | К131, К155, К134 | 2.4 | 0.4 | |

| КМОН | К176 | 7.7 | 0.5 | |

| К561 | 4.99 | 0.01 | ||

| К564 | 4.99 | 0.01 |

Порядок виконання роботи

Варіанти завдань.

Варіанти завдань на виконання лабораторної роботи №1 наведені в табл.1.2.1.

Таблиця 1.2.1. Варіанти завдань до лабораторної роботи №1

| № за списком | № варіанту | Завдання | |

| І | ІІ | ||

| 1; 4; 7;10; 13; 16 | ТТЛ* | ТТЛШ** | |

| 2; 5; 8; 11; 14; 17 | ТТЛ* | КМОН*** | |

| 3; 6; 9; 12; 15; 18 | ТТЛШ** | КМОН*** |

*- транзисторно-транзисторна логіка;

**- транзисторно-транзисторна логіка на базі транзисторів Шотки;

***- комплементарна метал-оксид-напівпровідник технологія;

Порядок виконання лабораторної роботи.

П.п.1-2 виконати для обох базових логічних елементів за варіантом завдання.

1. Зобразити електричні принципові схеми ЛЕ за варіантом для кожного з двох станів вхідних сигналів (ТТЛ, ТТЛШ –  КМОН –

КМОН –  ) з необхідними позначеннями на схемі: станів роботи транзисторів (відкритий, закритий), шляхи протікання струмів, значення керуючих напруг. Показати на схемі значення вхідних та вихідних сигналів.

) з необхідними позначеннями на схемі: станів роботи транзисторів (відкритий, закритий), шляхи протікання струмів, значення керуючих напруг. Показати на схемі значення вхідних та вихідних сигналів.

2. В середовищі програмного моделювання (Multisim або в аналогічному за можливостями середовищі) за варіантом завдання зобразити електричні схеми ЛЕ за варіантом. Провести тестування роботи ЛЕ для різних логічних рівнів на вході для отримання високих та низьких рівнів сигналу на виході.

3. Порівняти ЛЕ між собою (за швидкодією, завадостійкістю)

6. Зробити висновкипо завершенні лабораторної роботи та оформити звіт. Форму протоколу наведено в додатку 1.

Зміст протоколу.

üмета роботи;

üпостановка задачі;

üваріант завдання;

üелектричні схемиЛЕ за варіантом завдання для двох різних станів вхідних сигналів;

üрезультати моделювання роботи ЛЕ на комп’ютері за варіантом (PrintScreen програми):

· моделювання роботи ЛЕ з високим рівнем напруги на виході;

· моделювання роботи ЛЕ з низьким рівнем напруги на виході;

· порогове значення напруг для переключення ЛЕ з одного логічного стану до іншого (теоретично);

üвисновки по роботі (порівняння ЛЕ за різними технологіями виготовлення за швидкодією, завадостійкістю).

Контрольні питання.

1. Принцип роботи базового ЛЕ ТТЛ при різних значеннях вхідних напруг.

2. Принцип роботи базового ЛЕ ТТЛШ при різних значеннях вхідних напруг.

2. Принцип роботи базового ЛЕ на КМОП при різних значеннях вхідних напруг.

3. Сприймання ЛЕ різних технологій виготовлення непідключених входів.

4. Основні параметри роботи ЛЕ (швидкодія, завадостійкість, навантажувальна здатність).

5. Відмінність ТТЛ та ТТЛШ технологій виготовлення ЛЕ.

ЛАБОРАТОРНА РОБОТА №2

Спрощення логічних функцій та побудова цифрових комбінаційних схем на базових логічних елементах

Мета роботи.

Закріплення знань основних законів алгебри логіки. Оволодіння навичками розробки електричних принципових схем ЦП, їх збирання і налагодження.

Постановка задачі.

Реалізувати задану комбінаційну схему на запропонованій мікросхемі. Підтвердити працездатність реалізованої комбінаційної схеми.

2.1. Короткі теоретичні відомості

Етапи проектування цифрового пристрою (ЦП).

На сьогоднішній день, проектування ЦП доцільно проводити в 4 етапи.

1. Синтез та мінімізація логічної функції ЛФ.

2. Реалізація ЛФ у вигляді функціональної та електричної принципової схем.

3. Перевірка правильності функціонування схеми в пакеті комп’ютерного моделювання.

4. Виготовлення та налагодження фізичної реалізації ЛФ.

Форми запису логічних функцій.

Логічні функції ЛФ можуть бути задані:

¾ словами

¾ у вигляді таблиці істинності

¾ в арифметичній формі (у вигляді виразу).

ЛФ може бути задана будь-яким з цих способів, вони є рівнозначними між собою.

Розглянемо це на прикладі:

1. Словесний опис. Повністю визначена ЛФ

трьох аргументів A, B, C приймає значення «1», якщо хоча б два аргументи рівні 1. В усіх інших випадках ЛФ приймає значення «0».

трьох аргументів A, B, C приймає значення «1», якщо хоча б два аргументи рівні 1. В усіх інших випадках ЛФ приймає значення «0».

2. У вигляді таблиці істинності – перелік всіх можливих комбінацій вхідних аргументів та відповідні їм вихідні значення ЛФ.

Таблиця 2.1.1. Таблиця істинності ЛФ

| № |

|

|

|

|

3. Арифметична форма запису ЛФ. ЛФ можна записати за одиницями та за нулями.

При записі ЛФ за одиницями отримаємо диз’юктивну форму запису, де кожен з доданків є логічним добутком всіх аргументів.

Можемо перейти від таблиці істинності до диз’юктивної форми запису ЛФ. В таблиці істинності ЛФ залишаються тільки ті рядки, в яких ЛФ приймає значення 1. В результаті логічну функцію можна отримати у вигляді суми добутків вхідних аргументів. Кількість доданків дорівнює кількості рядків зі значенням ЛФ рівним 1. Доданки складаються з добутків вхідних аргументів: зі значенням рівним 1 аргументи входять до виразу без інверсії, зі значенням рівним 0 – з інверсією.

Таблиця 2.1.2. Диз’юктивна форма запису ЛФ

| № |

|

|

|

| ||

| перший доданок |

| |||||

| другий доданок |

| |||||

| третій доданок |

| |||||

| четвертий доданок |

|

При записі ЛФ за нулями отримаємо кон’юктивну форму запису, де кожен співмножник є логічною сумою всіх аргументів.

Можемо перейти від таблиці істинності до кон’юктивної форми запису ЛФ. В таблиці істинності ЛФ залишаються тільки ті рядки, в яких ЛФ приймає значення 0. В результаті логічну функцію можна отримати у вигляді добутків сум вхідних аргументів. Кількість добутків дорівнює кількості рядків зі значенням ЛФ рівним 0. Добутки складаються з сум вхідних аргументів: зі значенням рівним 0 аргументи входять до виразу без інверсії, зі значенням рівним 1 – з інверсією.

Таблиця 2.1.3. Кон’юктивна форма запису ЛФ

| № |

|

|

|

| ||

| перший множник |

| |||||

| другий множник |

| |||||

| третій множник |

| |||||

| четвертий множник |

|

Обидві форми запису є рівнозначними, оскільки відповідають одній таблиці істинності (табл.2.1.1.).

Кожна логічна операція реалізується за допомогою логічного елементу відповідного типу. Складність схеми, що реалізує ЛФ, її габарити, енергоспоживання, вартість залежать від кількості мікросхем, а не логічних елементів. До складу мікросхеми входить, як правило, тільки один тип логічних елементів. Тому при проектуванні основною задачею є мінімізація кількості використаних мікросхем. Тому одним з основних завдань при проектуванні схеми цифрового пристрою є мінімізація ЛФ та зведення її до єдиного базису.

Мінімізація ЛФ.

Мінімізація ЛФ – зменшення кількості логічних операцій в логічному виразі ЛФ. Це відповідає зменшенню кількості логічних елементів, що реалізує задану логічну функцію.

Мінімізація ЛФ базується на теоремах та аксіомах алгебри логіки.

Таблиця 2.1.4. Теореми та аксіоми алгебри логіки

| 1. |

| 8. |

|

| 2. |

| 9. |

|

| 3. |

| 10. |

|

| 4. |

| 11. |

|

| 5. |

| 12. |

|

| 6. |

| 13. |

|

| 7. |

| 14. |

|

15.

| |||

| Теорема де Моргана | |||

| 16. |

| 17. |

|

Приклади.

1.

Винесемо спільний множник  за дужки

за дужки  (табл.2.1.4. (6)).

(табл.2.1.4. (6)).

Використаємо тотожність(табл.2.1.4. (4)), маємо  .

.

Оскільки  , то

, то  . (табл.1.4. (9), (11))

. (табл.1.4. (9), (11))

2.

Розкриємо дужки (табл.2.1.4. (14)):

.

.

Оскільки  та

та  (табл.2.1.4. (1), (10)), то

(табл.2.1.4. (1), (10)), то  .

.

3.

Скористаємось теоремою де Моргана(табл.2.1.4. (16),(17)):

.

.

Оскільки  (15), то

(15), то  .

.

Завдання. Синтезувати схему ЦП, що реалізує ЛФ  .

.

Мінімізуємо ЛФ. Винесемо спільний множник для перших двох доданків:  . Оскільки

. Оскільки  , то

, то  .Винесемо множник

.Винесемо множник  за дужки

за дужки  .

.  (табл.2.1.4. (14)) маємо

(табл.2.1.4. (14)) маємо  .

.

Слід зауважити, що ЛФ не завжди можна мінімізувати. Наприклад, схема логічної рівнозначності (нерівнозначності) не піддається мінімізації, оскільки її форма є вже мінімально можливою.

Мінімізацію за допомогою теорем та аксіом алгебри логіки доцільно проводити, якщо кількість вхідних аргументів не перевищує трьох. Загалом, більш доцільно мінімізувати ЛФ за допомогою карт Карно або діаграм Вейча, що дозволяють формалізувати пошук спільних множників та спростити використання теорем та аксіом алгебри логіки.

Базові логічні елементи.

Кожній логічній операції відповідає логічний елемент. Для ЛФ  маємо 2 елементи «І» (

маємо 2 елементи «І» ( ,

,  ), 1 елемент «АБО» (+).

), 1 елемент «АБО» (+).

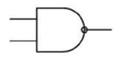

| Елемент 2 «І» (на 2 входи) | ||||||||||||||||||

позначення за стандартом ANSI

позначення за стандартом ANSI

|  традиційне позначення

традиційне позначення

|

|

| Елемент 2 «І-НЕ» (на 2 входи) | ||||||||||||||||||

позначення за стандартом ANSI

позначення за стандартом ANSI

|  традиційне позначення

традиційне позначення

|

| ||||||||||||||||

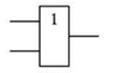

| Елемент 2 «АБО» (на 2 входи) | ||||||||||||||||||

позначення за стандартом ANSI

позначення за стандартом ANSI

|  традиційне позначення

традиційне позначення

|

| ||||||||||||||||

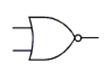

| Елемент 2 «АБО-НЕ» (на 2 входи) | ||||||||||||||||||

позначення за стандартом ANSI

позначення за стандартом ANSI

|  традиційне позначення

традиційне позначення

|

|

Складання функціональної схеми.

ЛФ  .

.

1. Позначити шини вхідних аргументів(рис.2.1.1).

3 вхідних аргументи  ,

,  ,

,  .

.

Рис.2.1.1. Шини вхідних аргументів

2. Визначити кількість базових логічних операцій та їх порядок.

Дві логічні операції «І», одна операція «АБО».

3. Для кожної логічної операції зобразити відповідний логічний елемент(рис.2.1.2) та з'єднати їх в порядку виконання логічних операцій (рис.2.1.3).

|

|

| Рис.2.1.2. Логічні елементи | Рис.2.1.3. Функціональна схема цифрового пристрою |

Дана схема реалізується на двох мікросхемах –наприклад, К155ЛИ1 (логічні елементи «І») та К155ЛЛ1 (логічні елементи «АБО»).

Зведення до єдиного базису. Теорема де Моргана.

Для зведення до одного базису (І, І-НЕ, АБО, АБО-НЕ) застосовують теореми де Моргана (табл.2.1.4. (16),(17)).

Зведемо ЛФ  до базису «І-НЕ».

до базису «І-НЕ».

. Дана ЛФ містить 3 логічні елементи І-НЕ. Для реалізації схеми, наприклад на мікросхемі К155ЛА3, що складається з чотирьох елементів І-НЕ на 2 входи (див. додаток 1), необхідна 1 мікросхема.

. Дана ЛФ містить 3 логічні елементи І-НЕ. Для реалізації схеми, наприклад на мікросхемі К155ЛА3, що складається з чотирьох елементів І-НЕ на 2 входи (див. додаток 1), необхідна 1 мікросхема.

Таким чином може бути зменшена складність реалізації, знижена вартість та габарити схеми при застосуванні однієї мікросхеми в базисі «І-НЕ» замість двох мікросхем базисів «І» та «АБО».

Побудова електричної принципової схеми.

Електрична принципова схема будується на основі функціональної схеми. Логічні елементи на електричній схемі нумерують відповідно до логічних елементів, що входять до складу мікросхем наступним чином DDi.j. (i – порядковий номер мікросхеми, j – порядковий номер логічного елементу в мікросхемі).

Побудуємо електричну схему для реалізації логічного виразу  на мікросхемі К155ЛА3 (рис.2.1.4.):

на мікросхемі К155ЛА3 (рис.2.1.4.):

Рис.2.1.4. Електрична принципова схема цифрового пристрою

Перевірка правильності функціонування схеми в пакеті комп’ютерного моделювання.

Існує безліч комп’ютерних пакетів для моделювання роботи схем. Наприклад, Electronic Workbench, Simulink Matlab, Multisim.

Для даної схеми пропонується провести симуляцію її роботи в середовищі Multisim (http://www.ni.com/downloads/evaluation.htm).

Наприклад, для вхідних аргументів  маємо на виході низький рівень сигналу

маємо на виході низький рівень сигналу  (рис.2.1.5а). Та для вхідної комбінації

(рис.2.1.5а). Та для вхідної комбінації  маємо на виході високий рівень сигналу

маємо на виході високий рівень сигналу  (рис.2.1.5.б).

(рис.2.1.5.б).

|

|

Рис.2.1.5.а.  , ,

| Рис.2.1.5.б.  , ,

|

Для всіх комбінацій вхідних аргументів за таблицею істинності перевіряємо роботу синтезованої схеми.

Особливості складання схеми та налагодження її роботи

Складання схеми та її налагодження може проводитись за двома алгоритмами:

1. Повна збірка схеми згідно електричної принципової схеми і перевірка виконується з виходу на вхід.

Спочатку проводиться перевірка сигналів на виході схеми. Якщо робота схеми відповідає таблиці істинності, то її робота вважається правильною. У протилежному випадку треба зміститись на крок ближче до входу схеми і перевірити правильність роботи даного етапу. (Якщо на цьому етапі схема працює без помилок, то несправним є останній логічний елемент.) Якщо ж зміщена на крок ближче до входу схема працює неправильно, то необхідно рухатись ще на крок назад і повторювати процедуру.

Такий метод збирання і налагодження використовують на виробництві при виготовленні схеми на друкованій платі.

2. Поетапна збірка та налагодження схеми.

В даному випадку виконується поетапне складання схеми зі входу на вихід та перевірка роботи кожного наступного логічного елементу.

При виконанні лабораторної роботи рекомендується використовувати другий метод, хоча він займає більше часу, але при цьому дозволяє відразу виправляти можливі помилки.

Для зручності збирання та налагодження схеми рекомендується на виході кожного логічного елементу підписувати значення логічної функції (рис.2.1.6).

рис.2.1.6. Схема ЦП для зручності налагодження та перевірки роботи

Порядок виконання роботи

Варіанти завдань.

Варіанти завдань на виконання лабораторної роботи №2 наведені в табл.2.2.1 ( ,

,  ,

,  - однорозрядні двійкові числа).

- однорозрядні двійкові числа).

Таблиця 2.2.1. Варіанти завдань до лабораторної роботи №2

| № за списком | № варіанту | Завдання |

| 1;8;15 | Реалізувати схему логічної рівності (А=В) | |

| 2;9;16 | Реалізувати схему логічної нерівності (А≠В) | |

| 3;10;17 | Реалізувати вираз А≥В | |

| 4;11;18 | Спростити та реалізувати вираз

| |

| 5;12;19 | Спростити та реалізувати вираз

| |

| 6;13;20 | Спростити та реалізувати вираз

| |

| 7;14;21 | Спростити та реалізувати вираз

|

Підготовка до виконання лабораторної роботи.

1. Здійснити мінімізацію ЛФ, використовуючи основні закони алгебри логіки, побудувати таблицю істинності даної логічної функції, привести її до заданого базису. (За замовчуванням базис І-НЕ).

2. Побудувати функціональну та електричну принципову схему ЦП, ознайомившись з довідковими даними заданої мікросхеми (за замовчуванням К155ЛА3 або 7400N) (див. додаток 1).

3. Перевірити правильність синтезу схеми, що реалізує дану ЛФ, провівши комп’ютерне моделювання схеми в пакеті напр. Multisim.

Виконання лабораторної роботи.

1. Зібрати макет та здійснити його налагодження.

2. Змінюючи значення вхідних аргументів  ,

,  ,

,  , скласти таблицю істинності логічної функції

, скласти таблицю істинності логічної функції  , реалізованої на макеті. Переконатися в правильності роботи схеми.

, реалізованої на макеті. Переконатися в правильності роботи схеми.

3. Зробити висновки по завершенні лабораторної роботи та оформити звіт. Форму протоколу наведено в додатку 2.

Зміст протоколу.

üмета роботи;

üпостановка задачі;

üваріант завдання:

· запис ЛФ за варіантом завдання;

· мінімізація ЛФ;

· запис в єдиному базисі;

· функціональна схема ЦП, що реалізує задану ЛФ;

· таблиця істинності заданої ЛФ;

üелектрична схема ЦП, що реалізує задану ЛФ;

üрезультати моделювання схеми на комп’ютері (PrintScreen програми);

üтаблиця істинності реалізованої на макеті схеми;

üпорівняння таблиці істинності синтезованого виразу та реалізованої схеми, перевірка правильності роботи схеми;

üвисновки по роботі.

Структура висновків.

1. Мета проведення мінімізації ЛФ.

2. Основні закони алгебри логіки, що використовуються для мінімізації.

3. Закони, за якими здійснюється перехід від одного базису до іншого.

4. Доцільність зведення ЛФ до одного базису.

5. Яким чином проводилась перевірка правильності роботи схеми.

Контрольні питання.

1. Основні закони алгебри логіки. Застосування.

2. Спрощення логічних виразів.

3. Теорема де Моргана. ЇЇ застосування.

4.Етапи проектування ЦП.

ЛАБОРАТОРНА РОБОТА №3

Дослідження цифрових комбінаційних схем на базі мультиплексора

Мета роботи.

Оволодіння навичками розробки електричних принципових схем комбінаційної логіки на базі мультиплексора; їх збирання та налагодження.

Постановка задачі.

Реалізувати задані комбінаційні схеми на запропонованій мікросхемі. Підтвердити працездатність реалізованих комбінаційних схем.

3.1. Короткі теоретичні відомості

Основні положення. Визначення.

Мультиплексор – цифрова інтегральна мікросхема комбінаційної логіки, що має декілька входів різного призначення та один вихід. Вся сукупність входів мультиплексора розподіляється на дві групи – інформаційні входи (або входи даних) та адресні входи. Призначення мультиплексора – здійснити комутацію інформаційних входів під впливом сигналів на адресних входах, тобто в залежності від сигналів на адресних входах, на вихід передається сигнал одного з інформаційних входів.

Таким чином, мультиплексор – цифрова мікросхема, яка має N адресних входів та  інформаційнихвходів.

інформаційнихвходів.

В якості прикладу розглянемо мультиплексор  . В мікросхемі вісім інформаційних входів

. В мікросхемі вісім інформаційних входів  , три адресних входи

, три адресних входи  і один вихід

і один вихід  (рис. 3.1.1).

(рис. 3.1.1).

Рис.3.1.1. Мультиплексор

Таблиця істинності роботи даного мультиплексора наведена в табл.3.1.1.

Таблиця 3.1.1. Таблиця істинності мультиплексора  .

.

| A2 | A1 | A0 | F |

| D0 | |||

| D1 | |||

| D2 | |||

| D3 | |||

| D4 | |||

| D5 | |||

| D6 | |||

| D7 |

З таблиці видно, що подана на адресні входи комбінація відповідає номеру інформаційного входу, що в даному випадку спрацьовує.

Мультиплексор можна віднести до універсальних логічних елементів тому, що в разі, коли число вхідних сигналів (аргументів функції) не перевершує  , реалізація будь-якої логічної функції не потребує додаткових елементів.

, реалізація будь-якої логічної функції не потребує додаткових елементів.

Приклад реалізації логічної функції з кількістю вхідних аргументів меншою, ніж кількість інформаційних входів.

Як приклад розглянемо реалізацію ЛФ  на базі мультиплексора з трьомаадресними входами.

на базі мультиплексора з трьомаадресними входами.

Таблиця істинності даної функції  :

:

|

|

|

За табл.3.1.1 подамо вхідні аргументи  і

і  на адресні входи двох молодших розрядів

на адресні входи двох молодших розрядів  ,

,