Государственное образовательное учреждение

высшего профессионального образования

«Кузбасский государственный технический университет»

Кафедра электропривода и автоматизации

ЭЛЕКТРОНИКА

Часть 2

Методические указания к лабораторным работам по курсам

«Физические основы электроники»,

«Физические основы промэлектроники»,

«Информационно-измерительная техника и электроника»

для студентов специальностей 140604 «Электропривод

и автоматика промышленных установок

и технологических комплексов»,

140211 «Электроснабжение»,

190702 «Организация и безопасность движения»,

всех форм обучения

Составители В. В. Демьянов

C. В. Сидельцев

Утверждены на заседании кафедры

Протокол № 11 от 26.06.2009

Рекомендованы к печати

учебно-методической комиссией

специальности 140604

Протокол № 15 от 26.06.2009

Электронная копия находится

в библиотеке ГУ КузГТУ

Кемерово 2009

ОПИСАНИЕ УНИВЕРСАЛЬНОГО СТЕНДА

ПО ОСНОВАМ ЦИФРОВОЙ ЭЛЕКТРОНИКИ

Стенд по основам цифровой электроники предназначен для проведения лабораторных занятий по курсам, связанным с цифровой электроникой в высших и других учебных заведениях.

Стенд позволяет проводить лабораторные работы по изучению и исследованию следующих элементов, узлов и устройств цифровой и вычислительной техники:

1. Логических элементов НЕ, ИЛИ, ИЛИ-НЕ, И, И-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕРАВНОЗНАЧНОСТЬ;

2. Комбинационных узлов, собранных на базовых логических элементах – трехразрядного устройства проверки на четность, устройства сравнения двух двухразрядных чисел, двоичного одноразрядного сумматора (два варианта);

3. Комбинационных узлов, выполненных в виде самостоятельных ИМС-дешифратора, демультиплексора мультиплексора, преобразователя двоичного кода в код семисегментного индикатора, четырехразрядного двоичного сумматора, четырехразрядного арифметико-логического устройства;

4. Последовательных элементов, собранных на базовых логических элементах – RS-триггера на элементах И-НЕ, RS-триггера на элементах ИЛИ-НЕ;

5. Последовательных элементов и узлов, выполненных в виде самостоятельных ИМС: RS-триггера, D-триггера, Т-триггера, двухразрядного параллельного регистра, двухразрядного последовательного регистра, четырехразрядного универсального регистра, кольцевого счетчика, суммирующего и вычитающего двоичных счетчиков, счетчика с коэффициентом счета, некратного степени 2, реверсивного счетчика с предустановкой, оперативного запоминающего устройства с организацией 16 ´ 4 бит.

6. Модели микроЭВМ в составе: АЛУ, ОЗУ, регистров операндов, команды и адреса, регистра-аккумулятора, мультиплексора общей шины, дешифратора сигналов управления, устройств ввода и вывода информации.

Стенд состоит из общего блока ввода-вывода информации и шести сменных плат, на которых установлены все исследуемые элементы, узлы и устройства. Стенд комплектуется набором сменных технологических карт (28 штук) с функциональными схемами исследуемых устройств.

В стенде используется ручной ввод данных и выбор режимов, т.е. при помощи тумблеров и кнопок и вывод данных на светодиодный дисплей в двоичном, десятичном и шестнадцатиричном кодах.

Техническое описание

На передней (наклонной) панели блока установлены тумблеры (SA1-SА5) и кнопки (SВ1-SB3) ввода информации и задания режимов работы исследуемых устройств. Переключатели SA1–SА4, SB2 и SB3 предназначены для подачи логических сигналов с уровнями 0 (соответствующий вывод замкнут на общий провод) или 1 (вывод замкнут на +5 В). Кнопка SB1 подключена к схеме защиты от «дребезга», выполненной на триггере. С помощью этой кнопки на выходе триггера формируется одиночный импульс с крутыми фронтами, необходимый для нормальной работы исследуемых триггеров, регистров и счетчиков. При нажатии SB1 на выходе появляется логический 0, а при отпускании – логическая 1. Этот блок в дальнейшем на схемах обозначается как формирователь одиночного импульса (Fл).

На передней панели блока установлен светодиодный дисплей для индикации режимов работы, а также входной и выходной информации исследуемого устройства. Дисплей состоит из девяти светодиодов HL1–HL9, позволяющих индицировать в 9 разрядах уровни логической 1 (светодиоды светятся) и логического 0 (не светятся), и семисегментного индикатора HG1 для индикации числа в десятичном или шестнадцатиричном кодах.

Индикатор HG1 подключается к исследуемой схеме через дешифратор на ИМС, преобразующий четырехразрядный двоичный код в семисегментный код индикатора HG1. При низком уровне напряжения на входе ИМС на индикаторе HG1 индицируется число в десятичном коде, при высоком уровне – в шестнадцатеричном. В дальнейшем устройство, содержащее дешифратор и индикатор HG1, обозначается как блок индикации (БИ).

Лабораторная работа №1

ИССЛЕДОВАНИЕ ОСНОВНЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ И ПРОСТЕЙШИХ КОМБИНАЦИОННЫХ УСТРОЙСТВ

ЦЕЛЬ РАБОТЫ: Исследовать элементы И-НЕ, ИЛИ-НЕ, И, ИЛИ, исключающее ИЛИ, неравнозначность, трехразрядное устройство проверки на четность, устройство сравнения двухразрядных чисел, двоичный одноразрядный сумматор

Работа проводится на плате П1 с технологическими картами I.1-I.9. На этих картах изображена принципиальная схема исследуемого устройства в виде соединений логических элементов, выполняющих определенные логические функции.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

| Х1 | Х2 | Y |

| 0 0 1 1 | 0 1 0 1 | 1 1 1 0 |

1.1. Элемент И-НЕ. Отрицание конъюнкции (карта I-1)

1.2. Элемент И. Конъюнкция (карта I-2)

| Х1 | Х2 | Y |

| 0 1 0 1 | 0 0 1 1 | 0 0 0 1 |

| Х1 | Х2 | Y |

| 0 1 0 1 | 0 0 1 1 | 1 0 0 0 |

1.3. Элемент ИЛИ-НЕ для положительной логики. Отрицание дизъюнкции (карта I-3)

| Х1 | Х2 | Y |

| 0 1 0 1 | 0 0 1 1 | 0 1 1 1 |

1.4. Элемент ИЛИ. Дизъюнкция (карта I-4)

1.5. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (карта I-5)

| Х1 | Х2 | Y |

| 0 1 0 1 | 0 0 1 1 | 0 1 1 0 |

1.6. Элемент логическая неравнозначность (карта I-6)

| Х1 | Х2 | Y |

| 0 1 0 1 | 0 0 1 1 | 1 0 0 1 |

1.7. Трехразрядное устройство для проверки на четность (карта I-7)

| Х1 | Х2 | Х3 | Y |

| 0 1 0 0 1 1 0 | 0 0 1 0 1 1 1 | 0 0 0 1 1 0 1 | 0 1 1 1 1 0 0 |

Четное число входов с сигналом высокого уровня – на выходе 0, нечетное – на выходе сигнал высокого уровня 1.

1.8. Устройство сравнения двухразрядных чисел (карта I-8)

| Х1 | Z1 | Х2 | Z2 | Y |

| 0 1 1 0 0 1 | 0 0 1 0 0 1 | 0 0 0 1 0 1 | 0 0 0 1 1 1 | 1 0 1 1 0 1 |

1.9. Двоичный одноразрядный сумматор (карта I-9)

| Х1 | Х2 | S | P |

| 1 0 1 0 | 0 1 1 0 | 1 1 0 0 | 0 0 1 0 |

Домашнее задание

1. Изучить основы алгебры логики.

2. Ознакомиться с элементной базой ТТЛ.

3. Зарисовать схемотехническую реализацию всех логических функций (И, НЕ, ИЛИ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ) на элементах типа И-НЕ. Разобрать работу логических схем.

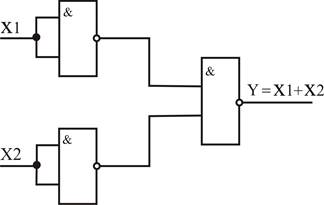

1. Комбинационная схема, выполняющая функции элемента И

2. Комбинационная схема, выполняющая функции элемента ИЛИ

3. Комбинационная схема, выполняющая функции элемента ИЛИ-НЕ

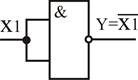

4. Логический элемент И-НЕ, выполняющий функции

элемента НЕ

5. Комбинационная схема, выполняющая функции элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

При защите лабораторной работы:

1. Объяснить назначение и применение исследуемых схем, их работу, полученные результаты.

2. Установить, какие узлы базового элемента ТТЛ определяют вид переходной характеристики и тип выполняемой логической функции.

3. Пользуясь законами алгебры логики, преобразовать заданную преподавателем схему в более простой вид.

4. Как изменятся логические функции заданных преподавателем устройств, если все его прямые входы и выходы изменить на инверсные?

Лабораторная работа № 2

ИССЛЕДОВАНИЕ ТРИГГЕРОВ RS- и D-ТИПОВ

ЦЕЛЬ РАБОТЫ: Исследовать триггеры RS-типа на элементах ИЛИ-НЕ, в интегральном исполнении на микросхеме К155ТМ2, триггера D-типа

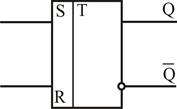

1. Триггер RS типа на элементах ИЛИ-НЕ

Trigger – (англ.) – спусковой крючок. Устройство, обладающее двумя состояниями устойчивого равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала.

Условное обозначение триггера на логических элементах ИЛИ-НЕ. Выходной информационный выход триггера обозначается через Q, инверсионный –

Условное обозначение триггера на логических элементах ИЛИ-НЕ. Выходной информационный выход триггера обозначается через Q, инверсионный –  .

.

Схема RS триггера

Схема RS триггера

Входы триггера:

S-set-установка 1, Reset-сброс 1, т.е. установка 0 на выходе Q.

При S=1 и R=0 на выходе Q устанавливается уровень логической 1, т.е. говорят, что триггер установлен в состояние 1.

При S=0, R=1 происходит очистка выхода Q, на нем устанавливается уровень логического 0.

| Режим работы | Входы | Выходы | Влияние на выход Q | ||

| S | R | Q |

| ||

| Запрещенное состояние | Не используется | ||||

| Установка 1 | Для установки Q в 1 | ||||

| Установка 0 | Для установки Q в 0 | ||||

| Хранение | Q |

| Зависит от предыдущего состояния |

Таблица истинности для RS триггера