Факультет информационных технологий и компьютерной безопасности

(факультет)

Кафедра Систем автоматизированного проектирования и информационных систем

ОТЧЕТ ПО ЛАБОРАТОРНОЙ РАБОТЕ № 1

по дисциплине Теория информационных процессов и систем

Тема ЗНАКОМСТВО С ALDEC HDL

Разработали студенты группы И.Н. Литовский

Подпись, дата Инициалы, фамилия

А.А. Зорин

Подпись, дата Инициалы, фамилия

Руководитель С.И. Короткевич

Подпись, дата Инициалы, фамилия

Защищена ___________________ Оценка _____________________________

дата

Лабораторная работа № 1

«ЗНАКОМСТВО С ALDEC HDL»

1 Цель работы: получение навыков для работы с отладчиком ALDEC HDL.

2 Задание на лабораторную работу

Лабораторное задание состоит в ознакомлении с назначением и возможностями отладчика моделей цифровых устройств на языке VHDL. Лабораторное задание включает ввод вашего варианта примера программы, написанной на VHDL, и освоение на ее примере принципов работы с данным CAD-продуктом.

3 Теоретическая часть

Aldec HDL транслирует и оптимизирует описания VHDL во внутренний формат, эквивалентный уровню примитивных логических элементов. Этот формат затем компилируется в технологию FPGA.

Aldec HDL выполняет три функции:

1. Транслирует VHDL во внутренний формат.

2. Оптимизирует представление блокового уровня с помощью различных методов оптимизации.

3. Размещает логическую структуру проекта в определенной технологической библиотеке Aldec с возможностью использования описаний элементов других производителей с помощью встроенных библиотек.

Когда проект VHDL открывается в FPGA Express, то он преобразуется во внутренний формат базы данных так, чтобы FPGA Express мог синтезировать и оптимизировать его. Когда FPGA Express оптимизирует проект, он может изменить структуру частей или всего проекта в целом. Управление идёт лишь степенью реструктуризации. Предоставляются следующие опции:

1. Полное сохранение иерархии проекта.

2. Перемещение целых модулей вверх или вниз по иерархии.

3. Комбинирование определенных модулей с другими.

4. Сжатие целого проекта в один модуль (сглаживание проекта), если это будет полезным.

Преимущества HDL.

Методология проекта, использующего HDL, имеет несколько фундаментальных преимуществ перед традиционной компонентно-уровневой методологией проектирования. Среди этих преимуществ необходимо отметить следующие:

Вы можете очень рано проверить функциональные возможности проекта и немедленно промоделировать его. Моделирование проекта на таком высшем уровне до трансляции в элементарное исполнение позволяет протестировать многие архитектурные и проектные решения.

FPGA Express обеспечивает логический синтез и оптимизацию, так что возможно автоматически преобразовать описание VHDL в исполнение элементарного уровня для выбранной технологии. Такая методология устраняет узкие места компонентного уровня и уменьшает время проектирования, а также количество ошибок, вносимых при ручной трансляции программы VHDL в конкретные элементы. С помощью логической оптимизации FPGA Express возможно автоматически преобразовать синтезированный проект в наименьшую и наискорейшую схему. Кроме того, допускается назначить информацию, полученную при синтезе и оптимизации схем, вновь к существующему описанию VHDL, что приводит к более точной подстройке архитектурных решений.

Описания HDL обеспечивают технологически независимую документацию проекта и его функциональных возможностей. Эти программы читаются и понимаются гораздо легче, чем списки цепей или схемы. Вследствие того, что начальное HDL описание проекта является технологически независимым, допускается использовать его для генерации проектов с различной технологией, не затрагивая при этом оригинальную.

VHDL, как и большинство языков высокого уровня, производит жесткую проверку типов. Компоненты, тип которых объявлен четырехбитовым сигналом, не могут соединяться с трех- или пятибитовым сигналом; такое несогласование приведет к ошибке при компиляции. Если диапазон переменных определен от 1 до 15, то ошибка возникнет при назначении им значения 0. Некорректное использование типов является основным источником ошибок при составлении описаний. Проверка типов обнаруживает такие ошибки даже перед генерацией проекта.

Отладка в ALDEC HDL

Для отладки необходимо осуществить следующие действия:

1. Создать описание проектируемого устройства (компонента) на языке VHDL в любом текстовом редакторе. При этом необходимым условием является то, что расширение данного файла должно быть: *.vhd.

2. Подключить созданный файл к проекту в Aldec HDL.

Для подключения файла к проекту необходимо создать сам проект.

Для удобства работы с файлом(ами) проекта в окне Design Browser выводятся название(ия), расположение(ия) файла(ов), а также наличие синтаксических и лексических ошибок или неточностей.

Также в этом контекстном меню есть возможность выбора разнообразных действий с данным проектом.

Open – открыть выбранный файл во внутреннем текстовом редакторе

Open in External Editor – открыть файл во файл во внешнем текстовом редакторе

Exclude from Compilation – не компилировать данный файл

Remove – удалить данный файл

Add to Design - подключение файла к проекту.

Refresh contents – обновить данные внутри проекта.

Design Compilation Order – правила компиляции проекта.

Assign HDL Files – связать HDL файлы в проекте.

Compile - проверка и сборка исходных описаний

Analyze – оптимизация исходного файла

3. После подключения файла к необходимо произвести компиляцию проекта или данного файла, чтобы можно было производить некоторые желаемые действия по моделированию. Если в файле есть синтаксические ошибки или логические, компиляция не пройдет успешно и будет выдан отчет об ошибках в меню «Console». С точным указанием места ошибки в самом тексте описания, что сходно с другими языками программирования и проектирования.

Редактирование файла происходит аналогично текстовым редакторам.

Успешно скомпилированный вариант отмечается «галочкой», неудачно – крестиком, некомпилированный – знаком вопроса, а если в процессе компиляции возникли какие-то некритичные ошибки, то будет выведено предупреждение в консоли и этот файл будет отмечен восклицательным знаком.

4 Ход работы

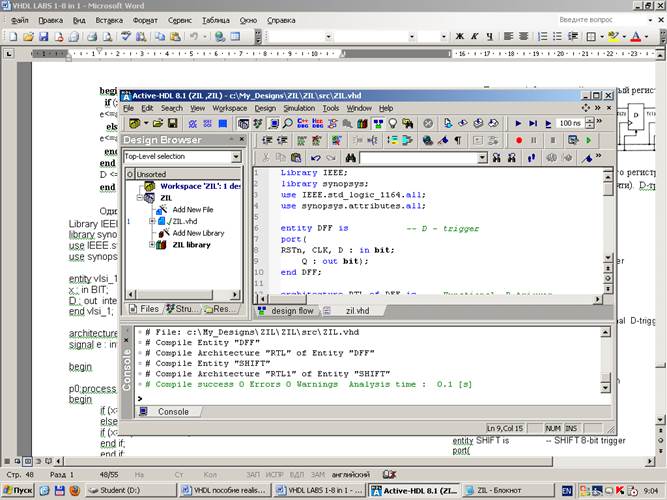

1. Для начала работы с Aldec HDL необходимо создать «Рабочее место» - Workspace (рисунок 1).

Для этого надо выбрать File > New > Workspace.

Рисунок 1 – «Рабочее место».

2. В текстовом документе набрали описание устройства, поменяли расширние на *.vhd.

3. Далее в созданное рабочее место было добавлено описание заданного устройства. Затем была проведена компиляция устройства (рисунок 2).

Рисунок 2 – «Результат компиляции устройства».

5 Исходный файл

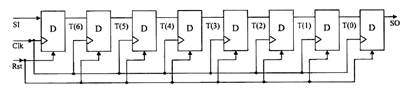

8-разрядный сдвиговый регистр

С состав 8-разрядного сдвигового регистра входит восемь подсхем - D-триггеров (элементов памяти). D-триггер имеет имя DFF. Схема SHIFT задает сдвиговый регистр - каскадное соединение D-триггеров (элементов памяти).

Компонент DFF конкретизирован (упомянут) восемь раз, чтобы получить сдвиговый регистр.

Каждый оператор создания экземпляра компонента должен иметь метку. Метки играют роль имен элементов схемы.

Карта портов дается в скобках после ключевых словport map.

Назначение портов компонентов является как позиционным (см. метки bit0, biti, bit2, bit3, bit5, bit6), так и ключевым (см. метки bit6, bit7).

Для выходных неиспользуемых портов компонентов нужно употребить ключевое словоopen.

Следующий фрагмент VHDL-кода показывает, что при создании экземпляра компонента addl на вход b1 можно подать константу 0 и выход с1 не использовать.

P1: addlport map (bl => '0', b2 => x, sl => sl, с1 => open);

VHDL описание имеет вид

Library IEEE;

library synopsys;

use IEEE.std_logic_1164.all;

use synopsys.attributes.all;

entity DFF is -- D - trigger

port(

RSTn, CLK, D: in bit;

Q: out bit);

end DFF;

architecture RTL of DFF is -- Functional D-trigger

begin

process (RSTn, CLK)

begin

if (RSTn = '0') then

Q <= '0';

elsif (CLK'event and CLK = '1') then

Q <= D;

end if;

end process;

end RTL;

entity SHIFT is -- SHIFT 8-bit trigger

port(

RSTn, CLK, SI: in bit;

SO: out bit);

end SHIFT;

architecture RTL1 of SHIFT is

component DFF

port(RSTn, CLK, D: in bit;

Q: out bit);

end component;

signal T: bit_vector(6 downto 0);

begin

bit7: DFF

port map (RSTn =>RSTn, CLK =>CLK, D =>SI, Q =>T(6));

bit6: DFF

port map (RSTn, CLK, T(6), T(5));

bit5: DFF

port map (RSTn, CLK, T(5), T(4));

bit4: DFF

port map (CLK=>CLK, RSTn=>RSTn, D=>T(4), Q=>T(3));

bit3: DFF

port map (RSTn, CLK, T(3), T(2));

bit2:DFF

port map (RSTn, CLK, T(2), T(1));

bit1: DFF

port map (RSTn, CLK, T(1), T(0));

bit0: DFF

port map (RSTn, CLK, T(0), SO);

end RTL1;

6 Вывод

В ходе лабораторной работы мы получили навыки работы с отладчиком Active-HDL. Также мы провели установку описания заданного устройства для дальнейшей отладки, используя исходный код в соответствии с полученным вариантом.