Электронная схема регулятора выполнена на 4-х отдельных платах.

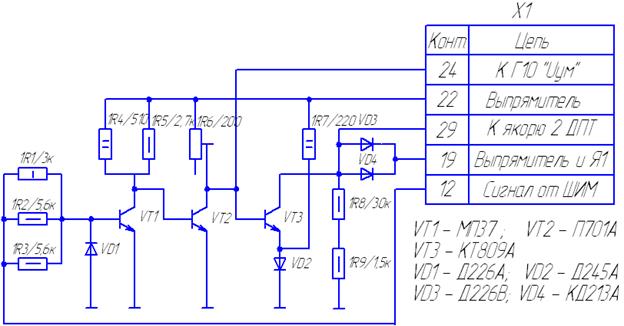

Плата 1.

Принципиальная схема платы приведена на рисунке 3.5.1.1.

На плате 1 собран 3х каскадный усилитель мощности (УМ). Первый каскад выполнен на транзисторе VT1 типа МП 37.

Второй каскад, промежуточный, выполнен на транзисторе VT2 типа П701. С его выхода сигнал подается на контрольное гнездо Г10 “U ум”. Транзистор закреплен на охладителе. Третий, выходной каскад, обеспечивающий большой ток в импульсе, выполнен на транзисторе VT3 типа КТ 809А, помещенном на охладителе. Цепочка 1R7,VD2 обеспечивает смещение на эмиттере транзистора VT3. Питание на коллектор транзистора VT3 подается от отдельного выпрямителя через якорную обмотку двигателя и тумблер 5П2, смонтированный на панели управления. Обмотка якоря зашунтирована диодами VD3,VD4 для того, чтобы предотвратить пробой транзистора VT3

Рис.3.5.1.1. Усилитель мощности.

большим импульсом напряжения, возникающим в момент закрывания транзистора VT3 на индуктивности якорной обмотки ДПТ.

Первый и второй каскады УМ питаются от отдельного выпрямителя.

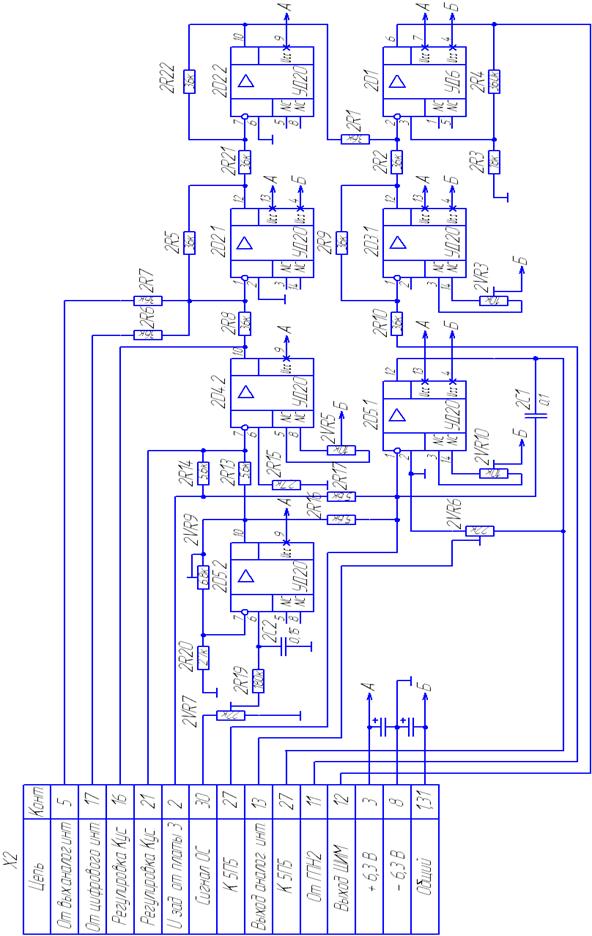

Плата 2

Первая часть схемы обработки сигналов.

Принципиальная схема платы приведена на рисунке 3.5.2.2.

Сигнал обратной связи с контакта 30 разъема Х2 подается через подстроечный многооборотный потенциометр 2VR7(22kOм) и фильтр НЧ 2R19..2C2 на неинвертирующий вход микросхемы 2D5.2, представляющей собой вторую половину микросхемы сдвоенного ОУ типа КР140УД20А. Этот сигнал подается также на контрольное гнездо Г4 “Uос”.

Качество фильтрации обеспечивается правильным подбором элементов пассивной инерционной RC-цепочки из 2R19(180кОм) и 2C2(0.15мкф). Коэффициент передачи фильтра подстраивается потенциометром 2VR9, подключенным к инвертирующему входу ОУ в цепи обратной связи 2D5.2. Подстройка необходима для согласования характеристик преобразования ПЧН2 и фильтра цепи ОС. Сигнал с выхода фильтра является аналоговым сигналом обратной связи, используемым для формирования сигнала ошибки пропорциональной составляющей закона регулирования и интегральной составляющей этого закона в в аналоговом интеграторе (АнИ).

Рис. 3.5.2.1. Схема обработки сигналов.

Напряжения с выходов задающего устройства ЗУ (контакт2 разъема

Х2) и фильтра 2D5.2 аналоговые сигналы Uзад и Uос, пропорциональные fзад и fдв соответственно, через входные резисторы 2R14 и 2R13 поступают на вход сумматора сигнала ошибки аналоговой составляющей закона управления, выполненного на второй половине ОУ типа КР140УД20 (микросхема 2D4.2). Коэффициент усиления сумматора регулируется с помощью потенциометра 5VR2, расположенного на панели управления. Потенциометр 5VR2 вместе с последовательно соединенным с ним резистором 5R2(5.6кОм) включен в цепь отрицательной обратной связи ОУ 2D4.2. Таким образом, минимальный коэффициент усиления сумматора составляет Кмин = -1. Выход сумматора подключен к контрольному гнезду Г11 “Стат. ош” и к сумматору ШИМ -формирователя 2D2 (резистор 2R8).

Параллельно входным цепям сумматора те же аналоговые сигналы Uзад и Uос через резисторы 2R16,2R17 поступают на первую половину микросхемы 2D5.1 (ОУ КР140УД20А). На данной микросхеме собран аналоговый интегратор сигнала ошибки необходимый для получения пропорционально-интегрального закона регулирования. В цепь ОС интегратора включена емкость 2C1(0.1мкф). Параллельно через тумблер 5П5,расположенный на панели управления, к емкости 2C1 может подключаться дополнительный конденсатор емкостью 0.5мкф. Выходное напряжение интегратора через многооборотный потенциометр 2VR6 поступает на тумблер 5П4 панели управления,с помощью которого можно включать и отключать интегральную составляющую закона управления. После тумблера сигнал аналогового интегратора (АнИ) выводится на контрольное гнездо Г8 “Сигн. АнИ”, а также подается на входной резистор 2R7 сумматора ШИМ-формирователя сигнала управления ДПТ.

Сигнал с выхода цифрового интегратора (ЦИ) через третий входной резистор 2R6 поступает на инвертирующий вход сумматора ФУЗР(2DA2.1), выполненного на первой половине ОУ типа КР140УД20А. На второй половине этой микросхемы выполнен инвертор 2D2.2, так же входящий в ФУЗР.

Первым элементом формирователя управляющего напряжения (ФУН) является компаратор 2D1(К140УД6А). Сигнал с инвертора 2D2.2 через резистор 2R1 подается неинвертирующий вход компаратора 2D1. Через резистор 2R2, сопротивление которого такое же, как и у резистора 2R1, на этот же вход 2D1 подается пилообразный сигнал с ГПН2 поступающий с платы 3. Как только уровень управляющего сигнала сравняется с напряжением выходного сигнала генератора пилообразного напряжения, произойдет возвращение компаратора 2DA1 в исходное положение и сформируется задний фронт ШИМ -сигналов управления ДПТ. Передний фронт же формируется при срабатывании компаратора 2DA1, которое происходит в случае когда сигнал пилообразного напряжения равен нулю.

Таким образом, длительность импульсов ШИМ -сигналов зависит от момента сравнения величин напряжений сумматора, пропорционального сигналу закона управления, и текущего напряжения ГПН2. Чем больше уровень Uсум, тем позже произойдет сравнение, тем больше длительность импульса ШИМ - сигнала, подавамого на усилитель мощности (УМ).

Выход ФУН подключен к контрольному гнезду Г9(“Вых. ШИМ”.1).

Плата 3.

Вторая часть схемы обработки сигналов.

Принципиальная схема платы приведена на рисунке 3.5.3.1

Преобразователь уровня напряжения U1 потенциометрического задатчика (5VR1) частоты вращения ДПТ в длительность импульсов пилообразной формы - это управляемый генератор пилообразного напряжения УГПН1.Длительность прямого хода пилы пропорциональна напряжению задатчика U1.Преобразователь представляет собой интегратор, выполненный на операционном усилителе (ОУ) 3DA6 типа КР140УД1А,в цепь обратной связи которого включен конденсатор 3C7 емкостью 0.033 мкф. Конденсатор зашунтирован электронным ключом на микросхеме 3DA5 типа 124КТ1А, представляющей собой микросборку двух транзисторов, соединенных в ключе по схеме составного транзистора. Базовая цепь ключа через резистор 3R17 сопротивлением 18 Ком соединена с выходом компаратора 3DA7 на ОУ К140УД6А. Выход интегратора соединен с гнездом Г5 “ГПН1” панели управления. Напряжения на выходе преобразователя Uгпн1 связано с входным напряжением U1 следующим соотношением:

(2)

(2)

Из формулы (2) видно, что крутизна пилы (т.е. скорость нарастания Uгпн1) прямо пропорциональна уровню напряжения U1 и обратно пропорциональна величинам сопротивлений резистора 3R22 и многооборотного подстроечного потенциометра 3VR22. Длительность прямого хода пилы зависит от момента достижения равенства напряжений Uгпн1 и напряжения порога срабатывания компаратора Uком. В момент равенства компаратор выдает на базу ключа открывающий импульс, и конденсатор 3C7 быстро разряжается через ключ. Начинается обратный ход УГПН1. Его выходное напряжение быстро падает до нуля, компаратор переходит в исходное состояние, ключ закрывается и начинается новый цикл заряда 3C7, т.е. прямой ход пилообразного напряжения. Уровень порога

срабатывания компаратора подстраивается с помощью многооборотного потенциометра 3VR4.

Рис. 3.5.3.1. Схема обработки сигналов.

На микросхеме 3DA4 типа КР140УД6А и микросхеме 3DA3 типа К1006ВИ1 собран формирователь Ф1 последовательности прямоугольных импульсов f зад. Микросхема 3DA4 – компаратор, который формирует из пилообразного напряжения прямоугольный импульс отрицательной полярности длительностью меньше периода пилообразного напряжения.

(период повторения этих импульсов равен периоду повторения импульсов пилообразного напряжения). Напряжение порога срабатывания компаратора выбирается меньше максимального значения пилообразного напряжения, а порог срабатывания задается цепочкой смещения 3R13,3VR2,3R15, запитанной от источника +6.3V. Срабатывание компаратора происходит в момент достижения равенства напряжения Uгпн1 и порога срабатывания компаратора. Как только начинается обратный ход УГПН1, происходит возвращение компаратора в исходное состояние, и начинает формироваться следующий отрицательный импульс формирователя. Выход формирователя Ф1 подключен к гнезду Г1 “fзад”. Импульсы fзад поступают на один из входов цифрового интегратора (ЦИ).

На микросхемах 3DA3 (К1006ВИ1), 3DA1 (К140УД1А) и 3DA2 (К140УД6А) собран преобразователь импульсов частоты fзад в постоянное напряжение задающего устройства ЗУ — ПЧН1. Уровень этого напряжения пропорционален частоте импульсов fзад, т. е. задаваемой частоте вращения ДПТ. На микросхеме интегрального таймера 3DA3 (К1006ВИ1) выполнен одновибратор вырабатывающий из последовательности отрицательных выходных импульсов компаратора 3DA4 последовательность прямоугольных импульсов положительной полярности с частотой повторения пилообразного напряжения и строго фиксированной амплитудой и длительностью. Микросхема 3DA2 выполняет роль фильтра интегрирующего типа: в обратную связь операционного усилителя К140УД6А включена параллельная RC-цепь,состоящая из емкости 3C3 (1мкф) и резистора 3R5 (51ком). На микросхеме 3DA1 собран инвертор.

Выход ПЧН1 является выходом всего задающего устройства ЗУ. Его сигнал (напряжение положительной полярности) подается на плату 2 и на контрольное гнездо Г3 “Uзад”.

На микросхеме 3DA13 (К140УД6А) выполнен формирователь (Ф2) последовательности импульсов действительной частоты вращения ДПТ. Схема представляет собой компаратор, преобразующий последовательность сферообразных импульсов ФДЧВ в последовательность прямоугольных импульсов с крутыми передними фронтами, частота которых равна частоте импульсов ФДЧВ, т.е.частоте fдв. Выход Ф2 подключен ко второму входу цифрового интегратора и контрольному гнезду Г2 “fдв”. С этого же выхода импульсы fдв поступают на преобразователь ПЧН2.

ПЧН2 выполнен на микросхемах 3DA12 (К1006ВИ1) и 3DA11 (К140УД6А). На микросхеме 3DА12 выполнен одновибратор, формирующий

последовательность прямоугольных импульсов с частотой fдв и строго фиксированной длительностью и амплитудой. 3DA12 (К1006ВИ1). Микросхема 3DA11 используется в схеме фильтра-интегратора. Фильтр преобразует последовательность импульсов fдв в постоянное напряжение, уровень которого прямо пропорционален частоте вращения двигателя. С выхода ПЧН2 напряжение подается на плату 2 на вход выходного фильтра формирователя ФОС.

На плате 3 на трех микросхемах выполнен генератор пилообразного напряжения ГПН2, входящий в узел формирования ШИМ- сигнала. На микросхеме 3DA9(К140УД1А) выполнен интегратор, в обратной связи которого включен конденсатор 3С9 емкостью 0.033 мкф зашунтированный электронным ключом 124КТ1А(микросхема 3DA8). Ключ управляется по базовому входу компаратором 3DA10 собранном на операционном усилителе К140УД6А. Порог срабатывания компаратора регулируется подстроечным многооборотным потенциометром 3VR6.

Выход ГПН2 подключен к плате 2 и контрольному гнезду Г6 “ГПН 2”.

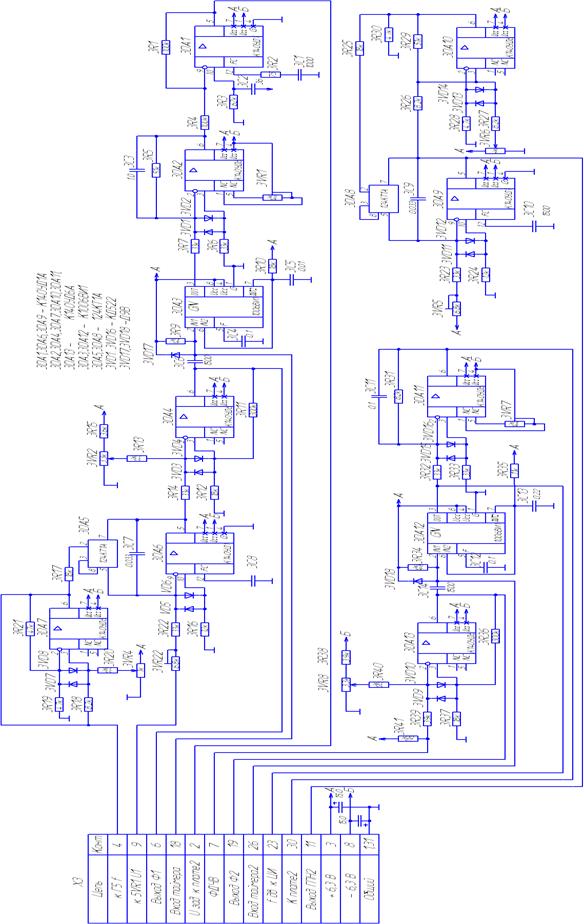

Плата 4.

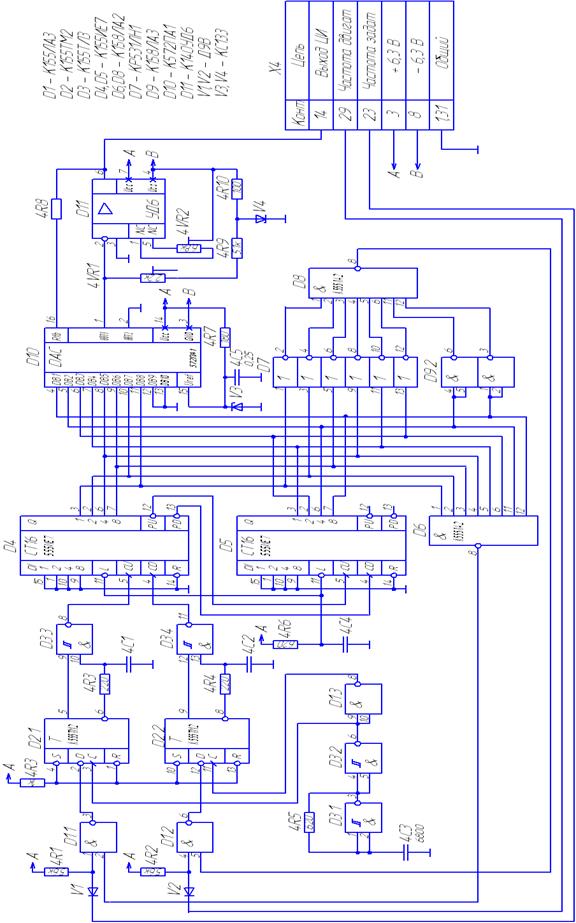

Принципиальная схема платы 4 (цифровой интегратор) приведена на рисунке 3.5.4.1.

Основу цифрового интегратора (ЦИ) составляет фазовый дискриминатор ФД, состоящий из:

1) двух входных ключей канала импульсов fдв на D1.1 и канала импульсов fзад на D1.2, выполненых на микросхеме К155ЛА3;

2) двух регистров-защелок счетных импульсов на D-триггерах D2.1 по каналу fдв и D2.2 по каналу fзад (микросхема К155ТМ2);

3) двух формирователей счетных импульсов D3.3 и D3.4 собранных на микросхеме содержащей триггеры Шмитта (К155ТЛ3);

4) двухкаскадного счетчика импульсов, содержимое которого пропорционально разности частот fзад-fдв, и выполненного на реверсивных двоичных счетчиках D4,D5 (микросхемы К155ИЕ7);

5) двух выключателей D6,D8 собранных на микросхеме К158ЛА2;

6) инверторов D7 (микросхема К531ЛН1).

Работу ФД обеспечивает генератор тактовых импульсов, два каскада которого построены на триггерах Шмитта, а третий каскад-это инвертор-формирователь тактовых импульсов по каналу fзад (D3.1,D3.2 и D3.3 соответственно).Сформированный цифровой код, пропорциональный интегралу сигнала ошибки df=fзад-fдв, необходимо преобразовать в аналоговый сигнал управления. Преобразователь построен на цифро-

-

-

Рис. 3.5.4.1. Схема цифрового интегратора.

аналоговом преобразователе (ЦАП) и выходном усилителе (D10 на микросхеме К572ПА1В и D11 на ОУ К140УД6А). Остальные элементы обеспечивают работу этих узлов.

Пусть на регулятор подано питание, но ротор двигателя еще не начал вращаться. На контакт 23 разъема Х4 поступают только импульсы fзад. На контакте 29 разъема Х4 нулевой потенциал - импульсы fдв не формируются, т.к. ротор двигателя не вращается.

Цепочка из диода и резистора, подключенная к плюсу источника питания на входе каждого канала (V1...4R1 и V2...4R2), обеспечивает надежное прохождение импульсов fзад и fдв без искажения переднего фронта и защиту от помех.

Ключ D1.1 подготовлен к пропуску импульсов fзад, т.к. на входе 2 D1.1 сигнал лог.1, который поступает с выхода D6. На всех входах этой микросхемы кроме нижнего по схеме низкие логические уровни (нули). Поскольку счетчики не работали, а при включении на входы предварительной записи информации «L» микросхем счетчиков с цепочки 4R6,4С4 был подан разрешающий сигнал, то во все разряды счетчиков кроме старшего будут записаны логические нули. В старший разряд счетчика записывается уровень «лог.1». Ключ D1.2 по каналу fдв тоже открыт, поскольку на выходе микросхемы D8 уровень «лог1».

При включении питания стенда - импульсы fзад через ключ D2.1 проходят на D-вход D-триггера D2.1, а на счетный вход С D2.1 с частотой 154 кГц поступают импульсы тактового генератора fтг. В результате суммирования сигналов поступающих с прямого выхода D-триггера D2.1 и задержанного RC цепочкой 4R3,4С1 сигнала поступающего с инверсного выхода указанного триггера на выходе триггера Шмитта D3.3 формируется последовательность коротких счетных импульсов. Уровень импульсов соответствует уровню «лог.0» а частота равна частоте fзад. В результате счетчик начинает подсчитывать импульсы с частотой fзад.

Если частота импульсов fзад. больше fдв счетчик будет накапливать свое содержимое, в противном случае его содержимое уменьшается. В случае полного заполнения счетчика (все выходы счетчика имеют уровни «лог.1») на выходе схемы совпадения D6 появляется уровень «лог.0» который поступая на вход ключа D1.1 запрещает прохождение импульсов fзад. на вход суммирования счетчика, предотвращая тем самым его переполнение. Аналогично, при достижении счетчиком нулевого состояния, срабатывает схема совпадения D8, запрещая опрокидывание счетчика (переход из обнуленного состояния в состояние полного заполнения). Поскольку в рассматриваемом случае fзад>fдв, то за определенный промежуток времени количество суммирующих и вычитающих импульсов неодинаково, в итоге постепенно на счетчике накапливается определенная сумма, пропорциональная интегралу от разности fзад - fдв. Накопление

прекращается, как только произойдет совпадение счетных импульсов на входах СD и СU. Код с выходов счетчика поступает на цифро-аналоговый преобразователь (ЦАП - микросхема D10 типа К572ПА1В), а выходной ток ЦАП пропорциональный входному коду, преобразуется в напряжение выходным ОУ D11 типа К140УД6А. Поскольку в схеме предусмотрена цепь смещения (4VR1,4R9,4R10,V4), обеспечивающая формирование вытекающего из точки соединения ЦАП и ОУ тока равного половине максимального тока формируемого ЦАП при максимальном коде на его входе, выходное напряжение ЦИ будет равно нулю при входном коде 80Н. При входном коде 00Н выходное напряжение будет максимальное и положительное, а при коде FFН – максимальное и отрицательное. В рассматриваемом случае на выходе ЦИ появляется напряжение отрицательной полярности, уровень которого пропорционален разности частот fзад - fдв. Это напряжение добавляется к напряжению пропорционального закона управления и стремится так увеличить частоту вращения, чтобы разность fзад - fдв свести к нулю.