Входы триггера

Входы триггеров обычно обозначают следующим образом:

· S (от англ. Set, установить) — вход в RS-триггере;

· R (от англ. Reset, сброс) — вход в RS-триггере;

· J (от англ. Jump [4], прыжок) — вход в JK-триггере;

· К (от англ. Kill, убить) — вход в JK-триггере;

· Т (от англ. Toggles, переключить) — счётный вход в Т-триггере;

· С (от англ. Clock, время) вход синхронизирующего сигнала. При тактировании по фронту он часто обозначается стрелкой: стрелка внутрь — тактирование по переднему фронту, наружу — по заднему.

· D (от англ. Delay, задержка) — вход в D-триггере;

· E или EN (от англ. Enable, разрешить) — дополнительный асинхронный управляющий вход для разрешения приёма информации (иногда используют букву V).

Входы J, К, Т, D всегда синхронные, т.е. тактируются по синхронизирующему сигналу на входе C. Разумеется, в каждом конкретном триггере имеются лишь некоторые из перечисленных входных линий. Входы S и R зачастую присутствуют не только в RS триггерах, но и в других типах триггеров, где предназначены, в основном, для асинхронного сброса устройства в 0 или установки в 1.

RS-триггер, или SR-триггер

Одна из наглядных схем реализации асинхронного RS-триггера на базе двух элементов 2И-НЕ (NAND2)

RS-триггер, или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от англ. Set - установить) выходное состояние становится равным логической единице. А при подаче единицы на вход R (от англ. Reset - сбросить) выходное состояние становится равным логическому нулю. Если RS-триггер синхронный, то состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса. Состояние, при котором на оба входа R и S одновременно поданы логические единицы, является запрещённым. Так, например, схема RS-триггера, изображённая на рисунке, при подаче на оба инверсных входа логического нуля перейдёт в состояние, когда на обоих выходах будут единицы, что не соответствует логике выхода триггера, поскольку инверсный выход  будет равен неинверсному

будет равен неинверсному  , т.е.

, т.е.  .

.

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами, отдельно управляемыми посредством стробов, разнесённых во времени.

JK-триггер

Символ JK-триггера с дополнительными асинхронными входами S и R, аналогично представлению в среде разработки

JK-триггер работает также как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (от англ. Jump - прыжок) аналогичен входу S у RS-триггера. Вход K (от англ. Kill - убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К [5].

D-триггер

Символ D-триггера с дополнительными асинхронными входами S и R

D-триггер (D от англ. delay - задержка) - запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы.

D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине.

T-триггер

Изображение T-триггера на схемах.

Работа схемы T-триггера (при T =1) на базе восьми 2И-НЕ логических вентилей. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер может строиться как на JK, так и на D-триггерах. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. Наличие в D-триггере динамического С входа позволяет получить на его основе T-триггер. При этом вход D соединяется с инверсным выходом, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение  , то есть будет переключаться в противоположное состояние.

, то есть будет переключаться в противоположное состояние.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

Триггеры. Практическая часть.

Триггеры имеют два устойчивых состояния. Эти состояния определяются по логическим уровням на выходах триггера. Триггер снабжается двумя выходами: прямым Q и инверсным Q. Состояние триггера определяет логический уровень на выходе Q. Говорят, что триггер находится в состоянии логической единицы, если на выходе Q уровень напряжения, соответствующий логической единице.

Обычно название триггера дают по имеющимся у него входам: RS-риггер, JK-триггер, D-триггер и др.

По способу записи информации триггеры подразделяются на асинхронные и синхронные. В асинхронных триггерах состояние на выходе изменяется сразу же после изменения сигнала на информационных входах. В синхронных триггерах для передачи сигнала с информационных входов на выходы требуется специальный синхронизирующий импульс. Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигнала с информационных входов на выходы осуществляется по фронту или по спаду синхронизирующего импульса.

Триггеры относятся к цифровым автоматам. В отличие от комбинационных схем состояние на выходе триггера в данный момент времени определяется не только состояниями на входах триггера в этот же момент времени, но и предыдущим состоянием триггера. Цифровые автоматы, к которым относятся триггеры, иногда называют последовательными схемами.

Триггеры строились по самым разнообразным электрическим схемам. В последнее время триггеры обычно конструируют, используя логические элементы.

Рассмотрим два варианта RS-триггера: RS-триггер с прямыми входами и RS-триггер с инверсными входами. Установка триггера в нужное состояние осуществляется подачей уровня логической «1» на соответствующий вход для триггера с прямыми входами и подачей сигналов логического «0» для триггера с инверсными входами.

Наибольшее распространение получили RS-триггеры, построенные на логических элементах 2И-НЕ или 2ИЛИ-НЕ. На рисунке 1.36,а приведена функциональная схема RS-триггера с инверсными входами на двух логических элементах 2И-НЕ, а на рисунке 1.36,б – его условное обозначение на принципиальных схемах.

RS- триггер с прямыми входами можно получить, имея в наличии два логических элемента 2ИЛИ-НЕ. Триггер получается путем соединения выхода первого логического элемента с одним из входов второго и соединения выхода второго логического элемента с одним из входов первого. Как видно из получившейся схемы (рис. 1.37,а), по отношению к логическим элементам триггер симметричен. По этой причине не имеет принципиального значения, выход какого из элементов считать прямым выходом триггера. Допустим, что прямым выходом триггера является верхний вывод. Определим, какой из входов триггера является входом R, а какой – входом S. Вспомним, что активным логическим уровнем для элементов ИЛИ-НЕ является уровень логической единицы, т.е. если на входе элемента 2ИЛИ-НЕ действует логическая «1», то на выходе будет «0». Зная, что вход R – это вход установки триггера в нулевое состояние, приходим к выводу, что входом R в данном случае будет верхний вход RS-триггера. Функциональная схема RS-триггера с прямыми входами на двух логических элементах 2ИЛИ-НЕ и его условное обозначение на принципиальных схемах приведены соответственно на рисунках 1.37а,б.

Работу RS-триггера можно описать различными способами: аналитически с помощью формулы; с помощью таблицы, в которой записываются состояния на входах и выходах триггера в различные моменты времени; с помощью временных диаграмм. На временной диаграмме показывают, как меняются сигналы на выходах триггера при изменении сигналов на его входах.

Рассмотрим временную диаграмму работы RS-триггера с прямыми входами. Для RS-триггера нужно показать 4 графика (рис. 1.38). Пусть на входах R и S установлены пассивные для элементов ИЛИ-НЕ уровни логического нуля (пассивные логические уровни не могут изменить состояние триггера) и пусть триггер находится в единичном состоянии, т.е. на выходеQ уровень логической единицы. Подадим на вход R в момент времени t1 уровень логической единицы. Для анализа работы RS-триггера, как и любого цифрового устройства, воспользуемся понятием активного логического уровня. Это существенно облегчает анализ работы схемы. Если на одном входе логического элемента действует активный логический уровень, то нет необходимости анализировать логические состояния на других входах элемента. Т.к. в момент времени t1 на входе R элемента DD1.1 действует активный логический уровень, то на выходе этого элемента, как следует из таблицы истинности, будет уровень логического нуля. На входах Х1 и Х2 элемента DD1.2 уровни логического нуля и, следовательно, на выходе этого элемента уровень логической единицы. Мы видим, что состояние триггера изменилось с единичного на нулевое. В момент времени t2 установим на входе R уровень логического нуля. На входе Х2 элемента DD1.1 уровень логической единицы и поэтому состояние триггера не изменится: на выходе Q логический нуль, а на выходеQ – логическая единица. В момент времени t3 на входе S установим уровень логической единицы, т.е. на входе Х2 элемента DD1.2 будет активный логический уровень и на выходе этого элемента установится уровень логического нуля. На входах Х1 и Х2 элемента DD1.1 будут уровни логического нуля, а на выходе этого элемента – уровень логической единицы. Триггер перешел из нулевого состояния в единичное. В момент времени t4 подадим на вход S уровень логического нуля и, проведя аналогичный анализ, увидим, что состояние триггера в момент времени t4 не изменится. В момент времени t5 подадим на вход S уровень логической единицы. Проведя аналогичный анализ, увидим, что состояние триггера не изменилось: на прямом выходе Q – уровень логической единицы, а на инверсном – уровень логического нуля. В момент времени t6 установим уровень логической единицы на входе R.В этом случае на выходе Q появится уровень логического нуля, и уровень логического нуля останется на выходе Q. В момент времени t7 установим на входах R и S одновременно уровень логического нуля. Состояние триггера в этом случае будет неопределенным. Может оказаться, что на выходе Q логическая единица, а на выходе Q логический нуль, или наоборот. Поэтому в устройствах цифровой техники одновременную подачу активных логических уровней на входы R и S триггера запрещают. Такой запрет делают не потому, что триггер выйдет из строя, а потому, что состояние триггера неоднозначно после одновременного снятия уровней логической единицы на входах R и S. В момент времени t8 подадим на вход R напряжение логической единицы, в результате чего на прямом выходе триггера получим напряжение логического нуля.

Рассмотренные триггеры относятся к так называемым асинхронным триггерам. В асинхронных триггерах состояние на выходе изменяется в момент поступления сигналов на информационные входы. В синхронных триггерах для передачи сигнала с информационных входов на выход требуется специальный синхронизирующий импульс.

Синхронные триггеры подразделяются на триггеры со статическим управлением и триггеры с динамическим управлением. В триггерах с динамическим управлением передача сигналов с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса.

На рисунках 1.39,а,в приведены функциональные схемы синхронного RS-триггера с прямыми входами, а условное обозначение этих триггеров на принципиальных схемах показано на рисунке 1.39,б.

Рассмотрим функциональную схему синхронного RS-триггера, приведенную на рисунке 1.39а. При С=0 на входах R, S асинхронного триггера на

элементах DD1.1 и DD1.2 действуют сигналы логического нуля (логический нуль является пассивным логическим уровнем для логических элементов 2ИЛИ-НЕ), поэтому при любых комбинациях сигналов на входах R, S синхронного RS-триггера состояние триггера не меняется. При С=1 рассмотренный синхронный RS-триггер работает точно так же, как рассмотренный чуть раньше асинхронный RS-триггер с прямыми входами. Рассмотренный только что синхронный RS-триггер относится к триггерам со статическим управлением.

На рисунках 1.40,а и 1.41,а приведены функциональные схемы синхронных RS-триггеров с динамическим управлением, а их условные обозначения на принципиальных схемах соответственно на рисунках 1.40,б и 1.41,б. Если в обозначении синхронного RS-триггера с динамическим управлением стрелочка на входе С направлена к триггеру, то передача сигналов с информационных входов на выходы происходит по фронту импульса, а если стрелочка направлена от обозначения триггера, то передача сигнала осуществляется по спаду импульса.

Рассмотрим синхронный RS-триггер с динамическим управлением, схема которого приведена на рисунке 1.40,а. Проанализировав функциональную схему синхронного RS-триггера с динамическим управлением, убедимся в том, что состояние триггера не меняется как при изменении сигналов на входах S и R при С=0, так и при С=1, если триггер переключился по фронту синхронизирующего импульса. При C=0 на выходах элементов DD2.1, DD2.2 будут сигналы логической единицы, и состояние на выходе триггера изменяться не будет при любых изменениях сигналов на входах R и S.

Установим на инверсном входе S уровень логического нуля, на инверсном входе R уровень логической единицы, и сигнал на входе С изменим с логического нуля на логическую единицу. На выходе элемента DD2.1 появится сигнал логического нуля и триггер перейдет в единичное состояние, или состояние триггера не изменится, если он находился в единичном состоянии. Оставляя на входе С сигнал логической единицы, перевести триггер в нулевое состояние не удается. Для перевода триггера в противоположное состояние обязательно необходимо подать синхронизирующий импульс.

В синхронных RS-триггерах со статическим управлением остается неоднозначность состояния на выходе триггера, если с входов R, S одновременно убирать активные уровни сигналов. Для устранения неоднозначности в схему синхронного RS-триггера добавляют логический элемент «НЕ». Получившийся триггер является D-триггером со статическим управлением. Функциональная схема этого триггера приведена на рисунке 1.42,а, а его условное обозначение на принципиальных схемах – на рисунке 1.42,б.

При С=0 состояние триггера изменяться не будет какой бы ни был сигнал на входе D, т.к. на выходах элементов DD2.1, DD2.2 будут сигналы логических нулей. При С=1 и D=1 на выходе элемента DD2.1 появится сигнал логического нуля, а на прямом выходе D-триггера – сигнал логической единицы. При С=1 и D=0 сигнал логического нуля появится на выходе элемента DD2.2, на инверсном выходе D-триггера установится логическая единица, а на прямом выходе –логический нуль. Таким образом, D-триггер воспринимает информацию с входа D и передает ее на выход Q при C=1, и затем хранит ее сколько угодно долго (пока подключен источник питания) при С=0. Т.е. мы имеем ячейку памяти для хранения 1 бита информации.

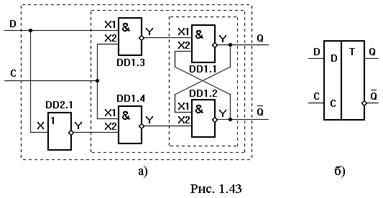

На рисунке 1.43,а приведен еще один вариант схемы D-триггера со статическим управлением. Условное обозначение обоих этих триггеров одинаковое.

Временная диаграмма работы D-триггера со статическим управлением приведена на рисунке 1.44. Из диаграммы следует, что передача информации с входа D на выход Q осуществляется во время действия синхронизирующего импульса. Счетный триггер из данного триггера путем соединения инверсного выхода с входом D получить нельзя.

Из D-триггера можно легко получить DV-триггер. Вместо логических элементов 2И-НЕ используют логические элементы 3И-НЕ и делают дополнительно вход разрешения V. Функциональная схемаDV-триггера и его условное обозначение на принципиальных схемах показаны соответственно на рисунке 1.45,а-б.

Широко используют D-триггеры с динамическим управлением. В них передача информации с информационных входов на выходы осуществляется либо по фронту синхронизирующего импульса, либо по спаду синхронизирующего импульса. Функциональная схема D-триггера с передачей информации с входа на выход триггера по фронту синхронизирующего импульса приведена на рисунке 1.46,а, а его условное обозначение на принципиальных схемах – на рисунке 1.46,б.

При С=0 на выходах элементов DD1.3, DD1.4 будут сигналы логических единиц и состояние на выходе триггера не изменится при любых изменениях сигнала на входе D. Установим на входе D сигнал логической единицы и изменим на входе С сигнал с логического нуля на единицу. Перед подачей на вход С сигнала логической единицы на выходе элемента DD1.2 логический нуль, а на верхнем входе элемента DD1.3 логическая единица. При появлении на входе С логической единицы на выходе элемента DD1.3 установится логический нуль, а на прямом выходе триггера – логическая единица. Сигнал логического нуля подается с выхода элемента DD1.3 на нижний вход элемент DD1.1 и на верхний вход элемента DD1.4. Оставляя на входе С логическую единицу, изменим сигнал на входе D с логической единицы на нуль. На выходе элемента DD1.2 установится логическая единица, а сигналы на выходах элементов DD1.1, DD1.3 не изменятся, следовательно, не изменится состояние на выходе триггера.

При D=0 изменим сигнал на входе С с логической единицы на нуль. На выходах элементов DD1.3, DD1.4 будут логические единицы, а на прямом выходе триггера останется сигнал логической единицы. Затем изменим сигнал на входе С с логического нуля на логическую единицу. На выходе DD1.4 установится логический нуль, на инверсном выходе триггера логическая единица, а прямом выходе – логический нуль. Из анализа работы данного триггера следует, что в нем передача информации с входа D на выход Q осуществляется по фронту синхронизирующего импульса, подаваемого на вход С.

Триггеры являются составной частью счетчиков электрических импульсов. D-триггер с динамическим управлением легко превратить в счетный триггер. С этой целью необходимо инверсный выход триггера соединить с информационным входом D, а импульсы подавать на синхронизирующий вход. Схема такого соединения приведена на рисунке 1.46,в.

Находят применение двухтактные RS-триггеры (рис. 1.47,а). На рисунке 1.47,б приведена схема счетного триггера, построенного на основе двухтактного RS-триггера. ДвухтактныйRS-триггер состоит из двух триггеров: главного и вспомогательного. Иногда главный триггер называют ведущим, а вспомогательный ведомым. По окончании синхронизирующего (тактового) импульса вспомогательный триггер переписывает информацию с выхода главного триггера. Используя двухтактные RS-триггеры, можно построить JK-триггер. В JK-триггере устранена неопределенность, возникающая в RS-триггере при одновременном снятии активных логических сигналов с входов R и S.

Функциональная схема JK-триггера, построенного с использованием двухтактных (двухступенчатых) RS-триггеров, приведена на рисунке 1.48,а, а его условное обозначение на принципиальных схемах – на рисунке 1.48,б.

В условных обозначениях триггеров, построенных с использованием двухтактного синхронного RS-триггера, ставят две буквы Т. Если входы J и K данного триггера соединить вместе и подать на них сигнал логической единицы, а импульсы подавать на вход С, то получим счетный триггер.

Широкое распространение получили JK-триггеры, построенные с использованием синхронных RS-триггеров с динамическим управлением. На рисунке 1.49,а приведена функциональная схема JK-триггера, переключающегося по спаду синхронизирующего импульса, а условное обозначение этого триггера на принципиальных схемах приведено на рисунке 1.49,б. Элементы DD1.1, DD1.2 образуют асинхронный RS-триггер.

Функциональная схема JK-триггера, переключающегося по фронту синхронизирующего импульса, показана на рисунке 1.50,а, а условное обозначение приведено на рисунке 1.50,б. При С=0 на выходах элементов DD2.1 и DD2.2 логические единицы и состояние RS–триггера DD3 не изменяется. Если на инверсных входах J и K логические единицы, то переключение сигнала на входе С с логического нуля на логическую единицу не изменит состояние на выходе JK–триггера.

На рисунке 1.50,в приведена схема использования JK-триггера в качестве счетного. На входы J и K подаются логические нули, а импульсы подаются на вход С. Вход С в данном случае является счетным входом Т. Частота импульсов на выходе данного счетчика в два раза меньше частоты импульсов на входе. Скважность импульсов на выходе счетчика равна двум независимо от скважности импульсов на входе счетчика.

Напомним, что триггеры относятся к цифровым автоматам. Цифровые автоматы состоят из комбинационных схем. Триггеры входят в состав счетчиков электрических импульсов, регистров, запоминающих устройств. Один из универсальных сдвиговых регистров рассмотрен в главе 2. Перейдем к рассмотрению счетчиков и запоминающих устройств.