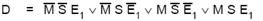

❒ Эксперимент 1: 1-битный полный вычитатель

| M | S | E 1 | D | E2 | |

| Неравнозначность |

Таблица 6.2.5.1

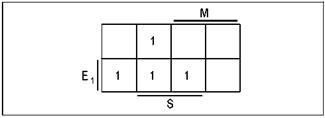

Рисунок 6.2.5.1 KV-диаграмма для D

|

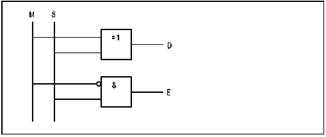

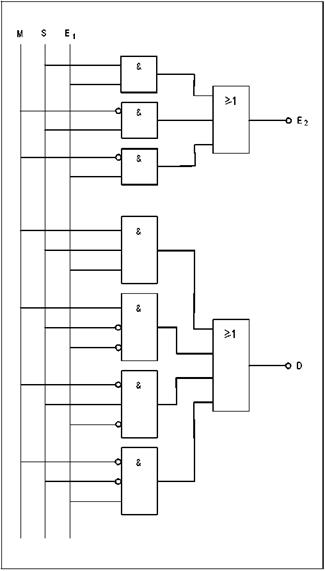

Рисунок 6.2.4.1 Схема 1

Рисунок 6.2.4.1 Схема 1

Рисунок 6.2.4.2 Схема 2

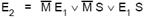

Рисунок 6.2.5.2 KV-диаграмма для E2

|  |

Вопрос 1: Полувычитатели можно использовать только с определенными ограничениями. Обоснуйте это мнение.

Вопрос 1: Полувычитатели можно использовать только с определенными ограничениями. Обоснуйте это мнение.

Вопрос 1: Сравните дедукцию схемы, представленной на рисунке 6.2.5.3, со схемой 1- битного полного сумматора.

Ответ: Полувычитатели можно использовать только при вычитании самых низких по значению разрядов двух двоичных чисел с разрядами n. В данном случае заимствование может не приниматься во внимание.

Ответ: Схема для образования разности(рисунок 6.2.5.3) является идентичной схеме для образования суммы в 1-битном полном сумматоре (рисунок 6.2.2.3).

|

❒ Эксперимент 2: Варианты схем 1-битного полного вычитателя

Обоснование:

D = M - S - E1

|

| Рисунок 6.2.5.4 Вариант схемы 1 |

|

| Рисунок 6.2.5.5 Вариант схемы 2 |

Разности от M - S образует первый полувычитатель, а поучающаяся промежуточная разность с E1 образует результат вычитания.

Рисунок 6.2.5.3 Схема 1-битного полного вычитателя

Примечания:

6.2.6 Вычитатель двоичных чисел ❒ Эксперимент 1:

| P - Q | CI | P3 | P2 | P1 | P0 | Q3 | Q2 | Q1 | Q0 | Σ 3 | Σ 2 | Σ 1 | Σ 0 | CO |

| 7 - 5 | ||||||||||||||

| 5 - 3 | ||||||||||||||

| 7 - 4 | ||||||||||||||

| 9 - 9 |

Таблица 6.2.6.

Рисунок 6.2.6.1 Схема

Вопрос 1: Положительные двоичные числа обозначаются через знаковый разряд с помощью «0». Как нужно дополнить схему на рисунке 6.2.6.1?

Вопрос 1: Положительные двоичные числа обозначаются через знаковый разряд с помощью «0». Как нужно дополнить схему на рисунке 6.2.6.1?

Ответ: Выход сигнала переноса CO должен быть инвертирован путем подключения элемента НЕ.

Ответ: Выход сигнала переноса CO должен быть инвертирован путем подключения элемента НЕ.

Вопрос 2: Следует решить примеры вычитания, результаты которых являются отрицательными, например, 6 – 9. Составьте соответствующие значения. Что они определяют?

Вопрос 2: Следует решить примеры вычитания, результаты которых являются отрицательными, например, 6 – 9. Составьте соответствующие значения. Что они определяют?

Вопрос 3: Исправьте схемотехническое проектирование, представленное на рисунке 6.2.6.1, таким образом, чтобы результат был следующим: CO Σ3 Σ2 Σ1 Σ0 = 10011. Если Вы удостоверились в правильности своей схемы, дополните рисунок 6.2.6.2 и занесите значения для отдельных входов и выходов. Указание: нет необходимости во втором 4-разрядном полном сумматоре.

|

| Рисунок 6.2.6.2 |

Ответ:

Ответ:

Ответ: Переноса не происходит, то есть CO = 0. Результат образуется во втором дополнении (Σ = 1101).

Ответ: Переноса не происходит, то есть CO = 0. Результат образуется во втором дополнении (Σ = 1101).