Микроконтроллер (МК) представляет собой функционально законченную МПС, которая реализована в виде одной большой интегральной микросхемы. МК объединяет в одном кристалле основные элементы МПС: центральный процессор (ЦП), постоянное запоминающее устройство (ПЗУ), оперативное запоминающее устройство (ОЗУ), порты ввода/вывода.

В настоящее время выпускается большая номенклатура микроконтроллеров, которые принято подразделять на 8-, 16- и 32-разрядные.

Наиболее многочисленной группой этих приборов являются 8-разрядные МК. Это простые и дешевые МК, ориентированные на использование в относительно несложных устройствах промышленной автоматики, измерительной технике, средств связи, бытовой технике. Эти МК имеют невысокую производительность, которая, однако, вполне достаточна для решения широкого круга задач управления различными объектами.

В настоящее время МК выпускаются в виде семейств. Семейство микроконтроллеров – это ряд (набор) МК, обладающих одинаковыми функциональными характеристиками. Обычно фирма-производитель дает имя семействам своих МК. Например, PIC16 – семейство микроконтроллеров фирмы Microchip, AVR – семейство микроконтроллеров фирмы Atmel.

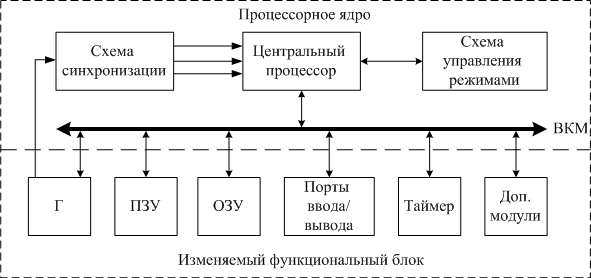

Большое разнообразие типов МК обеспечивает модульный принцип их построения. При этом все МК одного семейства содержат в себе базовый функциональный блок, одинаковый для всех МК семейства, и изменяемый функциональный блок, который отличает МК разных моделей в пределах одного семейства.

Базовый функциональный блок принято называть процессорным ядром МК. Процессорное ядро обозначают именем семейства МК, основой которого оно является. Например, ядро PIC16 - процессорное ядро семейства микроконтроллеров PIC16. Структура модульного МК приведена на рис. 1.

Процессорное ядро включает в себя:

· центральный процессор;

· внутреннюю контроллерную магистраль (ВКМ), состоящую из шин адреса, данных и управления;

· схему синхронизации МК, предназначенной для тактирования центрального процессора и шин магистрали;

· схему управления режимами работы МК, такими как - активный режим, в котором МК выполняет прикладную программу; режим пониженного энергопотребления; состояния начального запуска (сброса) и прерывания.

Изменяемый функциональный блок включает в себя модули памяти различного типа и объема (ПЗУ и ОЗУ), порты ввода/вывода, модуль тактового генератора (Г), таймеры и другие модули. Каждый модуль имеет выводы для подключения его к магистрали процессорного ядра. Это позволяет на уровне функционального проектирования новой модели МК подсоединить те или иные модули к магистрали процессорного ядра, создавая, таким образом, разнообразные по структуре МК в пределах одного семейства. Модули, объединенные в составе МК, размещаются на одном полупроводниковом кристалле. Отсюда появилось выражение «интегрированные на кристалле» периферийные модули.

Группа модулей периферийных устройств включает следующие основные типы:

· параллельные порты ввода/вывода;

· таймеры/счетчики, процессоры событий;

· контроллеры последовательного интерфейса нескольких типов (UART, SPI, I2C, CAN, USB);

· аналого-цифрового преобразования (АЦП);

· цифро-аналогового преобразования (ЦАП);

· контроллеры ЖК-индикаторов и светодиодной матрицы.

Возможны также некоторые другие типы модулей, например, модуль прямого доступа к памяти, модуль управления ключами силовых инверторов напряжения и т.п.

Рис. 1. Структура модульного микроконтроллера

В развитии элементной базы МК отчетливо прослеживается тенденция к закрытой архитектуре, при которой линии внутренних шин адреса и данных отсутствуют на выводах корпуса МК. И, как следствие, не представляется возможным использование внешних по отношению к МК микросхем запоминающих устройств. Поэтому разработчик микроконтроллерной системы при выборе элементной базы должен убедиться в том, чтобы прикладная программа проектируемой системы может разместиться во внутренней (резидентной) памяти МК. В противном случае придется перейти к МК с большим объемом внутреннего ПЗУ. Для подобных случаев производители обычно предлагают ряд модификаций МК с одним и тем же набором периферийных модулей и различными объемами резидентных памяти программ и данных.

Процессорное ядро микроконтроллера

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

· система команд процессора;

· способы адресации операндов в пространстве памяти;

· набор регистров для хранения промежуточных данных;

· организация процессов выборки и исполнения команд.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализуют на основе одного из двух принципов построения процессоров:

1) процессоры на основе CISC-архитектуры – это МК семейства MCS-51 фирм Intel, Atmel, Philips;

2) процессоры на основе RISC-архитектуры – это МК семейства PIC16, PIC17, PIC18 фирмы Microchip; семейство AVR фирмы Atmel.

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК с CISC-архитектурой процессор может иметь однобайтный, двухбайтный и трехбайтный (редко четырехбайтный) формат команд. При этом не все команды могут использовать любой из способов адресации применительно к любому из регистров процессора. Выборка команды из памяти осуществляется побайтно в течение нескольких машинных циклов. Время выполнения каждой команды с учетом времени выборки может составлять от 1 до 10 циклов. Длительность машинного цикла равна периоду частоты тактирования внутренней магистрали микроконтроллера ¦BUS. Максимально допустимое значение частоты ¦BUS является одной из важнейших характеристик процессорного ядра, так как чем больше ¦BUS, тем выше его производительность.

В микроконтроллерах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины: например, 12, 14 или даже 16 бит для МК с 8-разрядным форматом обрабатываемых данных. Выборка из памяти и исполнение подавляющего большинства команд осуществляются за один машинный цикл МК, т.е. один период ¦BUS – одна команда. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций.

Производительность микроконтроллеров, как и микропроцессоров, принято оценивать числом элементарных операций, которые могут быть выполнены в течение одной секунды. Единица измерения производительности – миллион операций в секунду (MIPS). Для расчета численного значения производительности в MIPS принято использовать время выполнения команды пересылки «регистр-регистр». Эта команда присутствует в перечне команд любого МК и имеет минимальное время выполнения. Таким образом,

Производительность (MIPS)=1/tкоманды (мкс).

С точки зрения организации процессов выборки и исполнения команд в современных 8-разрядных МК применяется одна из двух уже рассмотренных ранее архитектур МПС: Принстонская (Фон-неймановская) и Гарвардская.

Основной особенностью Принстонской архитектуры является использование общей памяти для хранения программ и данных. В этой архитектуре блок интерфейса с памятью выполняет арбитраж запросов к памяти, обеспечивая выборку команд, чтение и запись данных, размещаемых в памяти и внутренних регистрах процессора. Основное достоинство Принстонской архитектуры – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой памяти позволяет оперативно перераспределять ресурсы между областями программ и данных. Размещение стека в общей памяти облегчает доступ к его содержимому.

Основной особенностью Гарвардской архитектуры является использование раздельных памяти программ и памяти данных.

До конца 70-х годов Принстонская архитектура была основной в вычислительной технике и использовалась для создания универсальных компьютеров, включая и персональные компьютеры. Однако с началом разработки микроконтроллеров стали проявляться ее недостатки, и оказалось, что Гарвардская архитектура дает определенные преимущества для этих устройств.

Дело в том, что для реализации большинства алгоритмов управления, которые используются в микроконтроллерных системах, такие преимущества принстонской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, процессоры с Гарвардской архитектурой выполняют команды за меньшее количество машинных циклов, чем процессоры с Принстонской архитектурой, за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды.

Основной недостаток Гарвардской архитектуры – большое число шин и усложнение структуры процессора практически не оказывает влияние на стоимость изготовления микроконтроллеров, так как все элементы системы реализуются на одном кристалле, то есть внутри одной микросхемы.

Как и в любом микропроцессоре, система команд процессора МК включает в себя четыре основные группы команд:

· команды пересылки данных;

· арифметические команды;

· команды логические и сдвига;

· команды передачи управления.

Практика применения МК в системах управления показала, что в управляющих программах много операций с отдельными битами портов и регистров. Поэтому с целью создания эффективных программ и сокращения объема их кода в большинстве современных МК предусмотрены специальные средства, называемые битовым процессором. Команды битового процессора позволяют непосредственно изменять отдельные биты, выполнять логические операции с ними, а также тестировать их.

Система команд МК по сравнению с универсальными МП имеет менее развитые группы арифметических и логических команд, но зато более мощные группы команд пересылки данных и передачи управления. Эта особенность определяется сферой применения МК, которые ориентированы на реализацию программ управления в реальном масштабе времени.