Нетрудно заметить, что в шифраторе рассматриваемого типа сигнал, подаваемый на вход х о, не используется. Поэтому отсутствие сигнала на любом из входов х о,..., х 1 трактуется схемой как наличие на входе нулевого сигнала.

Нетрудно заметить, что в шифраторе рассматриваемого типа сигнал, подаваемый на вход х о, не используется. Поэтому отсутствие сигнала на любом из входов х о,..., х 1 трактуется схемой как наличие на входе нулевого сигнала.

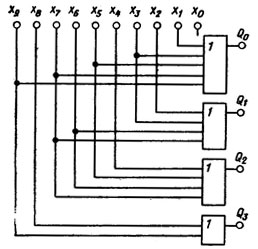

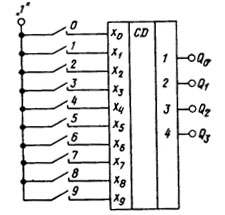

Основное применение шифратора в цифровых системах — это введение первичной информации с клавиатуры. При нажатии любой клавиши на соответствующий вход шифратора подается сигнал лог. 1, который и преобразуется на выходе в двоично-десятичный код. Вариант устройства ввода информации показан на рисунке ниже.

Устройство ввода информации с клавиатуры

Дешифратором, или декодером называется комбинационное логическое устройство для преобразования чисел из двоичной системы счисления в десятичную. Согласно определению дешифратор относится к классу преобразователей кодов. Здесь также понимается, что каждому входному двоичному числу ставится в соответствие сигнал, формируемый на определенном выходе устройства. Таким образом,

дешифратор выполняет операцию, обратную шифратору.

Если число адресных входов дешифратора n связана с числом его выходов m соотношением m = 2 n, то дешифратор называют полным. В противном случае, т.е. если m < 2 n, дешифратор называют неполным.

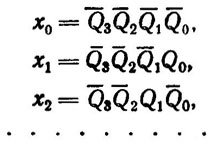

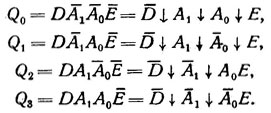

Поведение дешифратора описывается таблицей истинности, аналогичной таблице истинности шифратора (см.табл. выше), только в ней входные и выходные сигналы меняются местами. В соответствии с данной таблицей, так как выходной сигнал равен 1 только на одном единственном наборе входных переменных, т.е. для одной конституенты единицы, алгоритм работы дешифратора описывается системой уравнений вида

и так далее, где Q i — значение логической переменной на i -м входе устройства.

и так далее, где Q i — значение логической переменной на i -м входе устройства.

В общем виде эта система имеет вид

xi = (Q 3 Q 2 Q 1 Q 0) i

где x i — сигнал на i -м выходе дешифратора; (Q 3 Q 2 Q 1 Q 0) i — конституента единицы, соответствующая двоичному коду i -й десятичной цифры.

Нетрудно заметить, что ФАЛ дешифратора

отличается от ФАЛ мультиплексора

отличается от ФАЛ мультиплексора

только наличием в последней дополнительного множителя, соответствующего значению сигнала на информационном входе D. Поэтому при D = 1 демультиплексор функционирует как дешифратор. Обратное преобразование дешифратора в демультиплексор требует введения вспомогательных ЛЭ 2И, выполняющих операцию логического умножения между общим сигналом информационного входа D и соответствующим логическим произведением адресных сигналов (Q 3 Q 2 Q 1 Q 0). Схема построенного таким образом демультиплексора приведена на рисунке ниже, а.

только наличием в последней дополнительного множителя, соответствующего значению сигнала на информационном входе D. Поэтому при D = 1 демультиплексор функционирует как дешифратор. Обратное преобразование дешифратора в демультиплексор требует введения вспомогательных ЛЭ 2И, выполняющих операцию логического умножения между общим сигналом информационного входа D и соответствующим логическим произведением адресных сигналов (Q 3 Q 2 Q 1 Q 0). Схема построенного таким образом демультиплексора приведена на рисунке ниже, а.