Преобразователи кодов

Операция изменения кода числа называется его перекодированием. Интегральные микросхемы, выполняющие эти операции, называются преобразователями кодов.

Преобразователи кодов бывают простые и сложные. К простым относятся преобразователи, которые выполняют стандартные операции изменения кода чисел, например, преобразований двоичного кода в одинарный или обратную операцию. Сложные преобразователи кодов выполняют нестандартные преобразования кодов, и их схемы приходится разрабатывать каждый раз с помощью алгебры логики.

Будем считать, что преобразователи кодов имеют п входов и k выходов. Соотношения между п и k могут быть любыми: n-k, n<k и n>k. При преобразовании кода чисел с ними могут выполняться различные дополнительные операции, например, умножение на весовые коэффициенты. Примером невесового преобразования является преобразование двоично-десятичного кода в двоичный. Весовые преобразователи кодов используются при преобразовании числовой информации.

Интегральные микросхемы преобразователей кодов выпускаются только для наиболее распространенных операций:

• преобразователи двоично-десятичного кода в двоичный код;

• преобразователи двоичного кода в двоично-десятичный код;

• преобразователи двоичного кода в код Грея;

• преобразователи двоичного кода в код управления сегментными индикаторами;

• преобразователи двоичного или двоично-десятичного кода в код управления шкальными или

матричными индикаторами.

Примерами простейших преобразователей кодов, которые широко применяются в цифровых устройствах, являются шифраторы и дешифраторы.

Шифратором называют кодовый преобразователь, который имеет п входов и k выходов, и при подаче сигнала на один из входов (обязательно только на один) на выходах появляется двоичный код возбужденного входа. Очевидно, что число выходов и входов в полном шифраторе связано соотношением

n = 2k. (3.1)

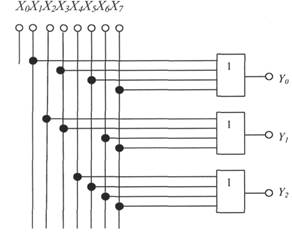

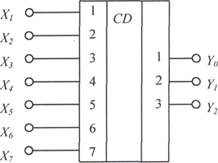

Рассмотрим принцип построения шифратора на примере преобразования 8-разрядного единичного кода в двоичный код. Схема такого шифратора приведена на рис. 15.3 а, а его условное схематичное обозначение — на рис. 15.3 б. Если все входные сигналы имеют нулевое значение, то на выходе шифратора будем иметь нулевой код Y0=Y1=Y2=0.

Младший выход, т. е. выход с весовым коэффициентом, равным 1, должен возбуждаться при входном сигнале на любом из нечетных входов, так как все

а б

Рис. 3.3. Схема шифратора восьмиразрядного единичного кода (а) и его условное схематическое

обозначение (б)

нечетные номера в двоичном представлении содержат единицу в младшем разряде. Следовательно, младший выход - это выход схемы ИЛИ, к входам которой подключены все входы с нечетными номерами.

Следующий выход имеет вес два. Он должен возбуждаться при подаче сигналов на входы с номерами 2, 3, б, 7, т. е. с номерами, имеющими в двоичном представлении единицу во втором разряде. Таким образом, входы элемента ИЛИ должны быть подключены к входным сигналам, имеющим указанные номера.

Старший разряд двоичного кода формируется из входных сигналов с номерами 4, 5, 6 и 7, т.е. из четырех старших разрядов единичного кода. Все рассмотренные состояния шифратора можно увидеть в таблице, приведенной на рис. 3.16.

Как следует из выполненного построения, при помощи шифратора можно сократить (сжать) информацию для передачи ее по меньшему числу линий связи, так как k < п. Обратное преобразование, т. е. восстановление информации в первоначальном виде можно выполнить с помощью дешифратора. Очевидно, что максимальное число входов шифратора не может превышать количество возможных комбинаций выходных сигналов, т. е. необходимо выполнение условия п< 2k (см. уравнение (3.1) для полного шифратора).

В цифровых системах с помощью шифраторов обеспечивается связь между различными устройствами посредством ограниченного числа линий связи. Так, например, в кнопочных пультах управления ввод числовых данных обычно выполняется в унитарном коде посредством нажатия одной из десяти кнопок, а ввод данных в микропроцессор выполняется в двоичном коде. Для преобразования кода кнопочного пульта в код микропроцессора также используется шифратор «из 10 в 4». Однако, поскольку четырехразрядный двоичный код имеет не 10, а 16 возможных комбинаций, такой шифратор будет неполным.

Состояние выходов шифратора, изображенного на рис. 3.3 а, приведено в табл. 3.1. Из этой таблицы следует, что для шифраторов должно выполняться условие хixj,= 0 при i ≠ j.

Если сигналы, поступающие на вход шифратора, являются независимыми, что бывает, например, при нажатии одновременно нескольких кнопок на кнопочном пульте управления, то условие хixj = 0 не выполняется. В этом случае каждому входу х, шифратора назначают.свой приоритет. Обычно считают, что чем выше номер входа, тем выше его приоритет. В этом случае шифратор должен выдавать на выходе двоичный код числа /', если х» = 1, а на все входы X/, имеющие больший приоритет, поданы нули. Такие шифраторы называются приоритетными, например, если на входе шифратора установлен код 0011, то на выходе будет код 01.

В качестве примера рассмотрим функционирование приоритетного шифратора К555ИВ1. Функционирование этого шифратора описывается табл. 3.2.

Условное схематическое изображение шифратора К555ИВ1 приведено на рис. 3.4 а. Назначение сигналов на входе шифратора: Е — сигнал включения шифратора (0 — выключен, 1 -включен). Сигналы на выходе: G сигнал, свидетельствующий о наличии хотя бы одного возбужденного входа х,- при включенном состоянии шифратора G=l при х,•> = 1, хотя бы для одного / при Е — 1); ЕО — сигнал разрешения, свидетельствующий об отсутствии возбужденных входов xt при включенном состоянии шифратора (ЕО=1 при Е =1 и х,; = 0 для всех /). Таким образом, трехразрядный двоичный код можно считывать с выхода шифратора только при условии, что G=l. Выходной сигнал ЕО можно использовать при каскадном включении шифраторов. Схема расширенного шифратора на ИМС

Таблица 3.1