Устройства обработки частотных и временных импульсных сигналов в настоящее время находят широкое применение в системах управления техническими объектами. Эти сигналы имеют частотно-импульсную и временно-импульсную модуляцию. Основными элементами устройств обработки являются всевозможные счетчики. Они выполняют функции сумматора, на которые слагаемые, представленные импульсным единичным кодом, поступают единичными приращениями. В общем случае аргументы функции могут поступать на устройство обработки единичными, разрядными приращениями и полными значениями.

Для обработки сигналов с частотной и временной импульсной модуляцией разработаны универсальные преобразователи: двоичный умножитель и двоичный делитель. С помощью этих преобразователей могут быть реализованы практически любые математические операции.

Двоичным умножителем называется устройство, реализующее функцию вида

f z = fxNy.

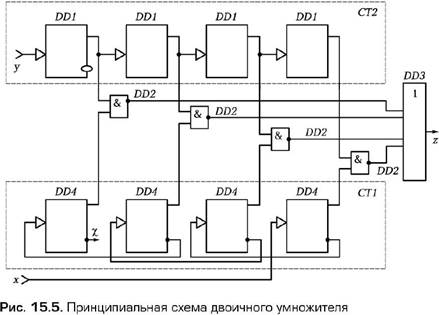

Принципиальная схема двоичного умножителя приведена на (рис. 15.5). Величина х, представленная импульсной последовательностью с частотой f 0, поступает на вход счетчика-делителя СТ1, состоящего из триггеров DD4. На выходе каждого разряда СТ1 формируются серии импульсов с частотами f 0 2‒ 1 , f 0 2‒ 2 ..., f 0 2‒ n, где n — число разрядов в счетчиках CT1 и СТ2. На счетный вход Т-триггера DD1 счетчика-регистратора СТ2 поступает величина y, представленная импульсной последовательностью, которая формирует в нем за время T 0 код Ny. Код Ny может вводиться в СТ2 и параллельно. Выходы младшего СТ2 и старшего СТ1 разрядов подключены к элементу И (DD2); аналогично и остальные разряды счетчиков подключены к соответствующим элементам И, выходы которых объединены элементом ИЛИ (DD3). Через элементы DD2 проходят импульсы, если соответствующие триггеры СТ2 находятся в состоянии «1». Подключение единичных выходов триггеров СТ1 к элементам DD2, а нулевых выходов — к триггерам старшего разряда обеспечивает несовпадение разрядных импульсов переноса на входе элемента DD3.

Число импульсов N на выходе двоичного умножителя без учета неравномерности периодов следования выходных импульсов за время T можно определить по формуле

N z = T 0 (anf 0 2‒ n + an ‒ 1 f 0 2‒(n ‒ 1) +... + a 1 f 0 2‒ 1 ) =  Ny,

Ny,

где a 1..., an — коэффициенты, равные соответственно 0 или 1; Ny — число в счетчике-регистраторе СТ2 в двоичном коде, сформированное за время T 0.

Средняя частота следования импульсов на выходе двоичного умножителя определяется выражением

f z = f 0 Ny / 2 n или f z = fxNy,

где fx = f 0/ 2 n.

Из полученного выражения следует, что двоичный умножитель может использоваться как преобразователь двоичного кода числа Ny в частоту следования импульсов f z.

Двоичные умножители находят широкое применение в измерительной технике для построения измерительных преобразователей и устройствах обработки информации и управления. Они используются также для построения генераторов с заданным законом изменения частоты в системах регулирования. Двоичный умножитель выпускается в промышленности в виде микросхемы.

Двоичным делителем называется устройство, реализующее функцию преобразования вида

f z = f 0/ Ny.

Принципиальная схема двоичного делителя представлена на (рис. 15.6). В регистр RG, состоящий из D-триггеров DD1, заносится код Ny. В качестве регистра RG может использоваться счетчик. По сигналу с выхода счетчика CT, состоящего из D-триггеров DD2, обратный код определяется выражением

Ny = 2 n ‒ Ny,

где n — число разрядов счетчика.

Следующий импульс на выходе появится через интервал T 0 = t 0 Ny, где t 0 = 1 / f 0. Двоичные делители являются преобразователями кода во временной интервал. Они могут использоваться для формирования временной задержки сигналов и в качестве фазовращателей. На двоичном двигателе, так же как и на двоичном умножителе, могут быть построены преобразователи частота — код с предельным быстродействием.