Рис. 1. Типовая схема интегрального регулятора напряжения.

На рис 1. не стабилизатор с малым напряжением потерь!!!

Требуемое для нормальной работы интегрального стабилизатора минимальное падение напряжения на нем составляет ~ 3 В. Для некоторых специальных случаев применения эта величина слишком велика. При использовании стандартного схемного решения стабилизатора она принципиально не может быть снижена. Как следует из схемы на рис. 14.14, источник тока I1 должен обеспечивать ток коллектора транзистора дифференциального каскада Т4 и базовый ток составного транзистора выходного каскада Т1', Т1. Для нормальной работы схемы источника тока необходимо падение напряжения ~ 1,5 В. Остальная часть общего падения напряжения приходится на эмиттерные переходы транзисторов выходного каскада; эта величина также составляет около 1,5 В.

Существенного снижения падения напряжения на стабилизаторе можно достичь путем применения в выходном каскаде р-п-р-транзисторов. В этом случае коллекторный ток транзистора дифференциального каскада может непосредственно использоваться в качестве базового тока транзистора выходного каскада; при этом отпадает необходимость в источнике тока I1. Схема такого стабилизатора приведена на рис. 2. Очевидно, что составной транзистор выходного каскада включен здесь по схеме с общим эмиттером. Вследствие возникающего в такой схеме дополнительного инвертирования фазы сигнала для управления выходным каскадом используется не транзистор T4, как в предыдущей схеме, а транзистор Т3. Минимальное падение напряжения на стабилизаторе равно напряжению насыщения транзистора T1 и не превышает 1 В.

Рис.2. Стабилизатор напряжения с малым напряжением потерь. Ua = [1+(R2/R1)]Uопори.

Более высокое по сравнению с эмиттерным повторителем выходное сопротивление оконечного каскада компенсируется в этой схеме тем, что выходной каскад имеет высокий коэффициент усиления по напряжению; последнее заметно повышает коэффициент петлевого усиления схемы стабилизатора.

Здесь могут использоваться те же методы ограничения тока стабилизатора, что и в классической схеме на рис. 1. Для измерения тока служит резистор R3, включенный в эмиттерную цепь выходного транзистора Т1. Подбором делителя напряжения на резисторах R5 и R4 также можно получить в этой схеме падающую выходную характеристику стабилизатора.

Для стабилизации отрицательных напряжений все транзисторы этой схемы должны быть заменены на транзисторы с противоположным типом проводимости. В этом случае выходной каскад выполняется на составном п-р-п-транзисторе. Такая схема может быть выполнена на базе интегральной технологии. На этой основе строятся схемы стабилизаторов отрицательных напряжений.

По подобной схеме построены, например, трех-выводные стабилизаторы напряжения малой мощности типа 1170ЕНхх, работающие при минимальном напряжении между входом и выходом 0.6 В. Они выпускаются в корпусах ТО-92 на фиксированные выходные напряжения 5, 6, 8, 9, 12 В при токе нагрузки до 100 мА и собственном потреблении не более 1.2 мА. Такие устройства в зарубежной литературе называют стабилизаторами типа LDO (low drop output — выход с малым перепадом). Мы в дальнейшем будем называть такие устройства МПН-стабилизаторами (стабилизаторами с малым падением напряжения).

Дальнейшее уменьшение минимально допустимого падения напряжения на стабилизаторе может быть достигнуто применением в качестве силового регулятора МОП-транзистора, включенного по схеме с общим истоком.

Упрощенная схема стабилизатора с регулирующим МОП-транзистором приведена на Рис. 3. Для стабилизации положительных напряжений используется транзистор с p-каналом, работающий в режиме обогащения. Схема работает следующим образом.

Рис. 3. Стабилизатор напряжения с регулирующим МОП-транзистором

При уменьшении сопротивления нагрузки выходное напряжение также уменьшается, и на входе усилителя появится ошибка V< 0. Выходное напряжение усилителя будет снижаться, уменьшая напряжение на затворе регулирующего МОП-транзистора. Поскольку это p-канальный транзистор, то уменьшение напряжения на его затворе вызовет увеличение тока стока и выходное напряжение увеличится до прежнего значения.

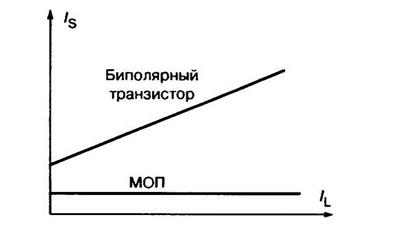

Большое достоинство стабилизаторов с регулирующим МОП-транзистором — независимость тока потребления (тока общего вывода) от тока нагрузки. Это связано с тем, что МОП-транзистор управляется напряжением, а ток его затвоpa (а следовательно, и выходной ток усилителя) совершенно ничтожен по сравнению с током нагрузки. На Рис. 4 представлены примерные зависимости тока собственного потребления Is от тока нагрузки IL стабилизаторов с регулирующими транзисторами различного типа.

Другое достоинство — падение напряжения на регулирующем элементе может быть снижено до очень малых величин, недостижимых для биполярных транзисторов.

Рис. 4. Сравнительные графики зависимостей тока потребления стабилизаторов с регулирующими транзисторами различного типа