¬ведение

¬ этой работе вы увидите, как разработать встроенную систему, использу€ процессорную систему (ѕ—) Zynq-7000 AP SoC.

—истема Zynq AP SoC состоит из €дра ARM Cortex A9 и программируемой логики (ѕЋ). ќна может быть использована двум€ способами:

1. ѕ— Zynq может быть использована в автономном режиме без подключени€ дополнительных модулей.

2. ¬строенные модули (IPs) могут быть присоединены к ѕ— Zynq как устройство, и вы можете использовать их комбинацию дл€ построени€ сложных и эффективных устройств на одной SOC.

—остав встроенной системы

—оздание системы Zynq включает в себ€ ее настройку и выбор соответствующих загрузочных устройств и периферии. ƒо тех пор пока периферийные устройства и доступные соединени€ MIO отвечают требовани€м системы, не требуетс€ битовый поток. Ёта работа проведет вас через создание такой системы.

—оздание нового проекта дл€ встроенной системы

1. «апустите приложение ISEЃ PlanAheadЩ.

2. ¬ыберете Create New Project, чтобы открытьNew Project wizard.

3. »спользу€ информацию из таблицы ниже сделайте соответствующие действи€ в открывшемс€ окне wizardТa.

| ќкно wizardТa | —войство системы | Ќастройка или команда |

| Project Name | Project name | ”кажите им€ проекта |

| Project location | ”кажите папку дл€ хранени€ проекта. ѕуть не должен содержать пробелы | |

| Create Project Subdirectory | ”берите галочку | |

| Project Type | ”кажите тип исходников дл€ системы. ¬ы можете начать с RTL или EDIF | ќставьте пункт по умолчанию. RTL Project |

| Add Sources | Ќичего не измен€йте | |

| Add Existing IP | Ќичего не измен€йте | |

| Add Constraints | Ќичего не измен€йте | |

| Default Part | Specify | ¬ыберите Boards. |

| Board | ¬ыберите Zynq-7 ZC702 Evaluation Board. | |

| New Project Summary | –езюме проекта | ѕросмотрите резюме и потом нажмите Finish дл€ создани€ проекта |

ѕосле нажати€ Finish, New Project wizard будет закрыт и только что созданный проект откроетс€ в PlanAhead.

“еперь, использу€ Add Sources wizard, создайте проект встроенного процессора. ƒл€ этого:

1. Ќажмите Add Sources в Project Manager. ќткроетс€ Add Sources wizard.

2. ¬ыберите пункт Add or Create Embedded Sources и нажмите Next.

3. Ќажмите Create Sub-Design.

4. ¬ведите название модул€, например, system и нажмите OK. —озданный модуль отобразитьс€ в списке источников (sources list).

5. Ќажмите Finish.

ѕрограмма PlanAhead создаст проект встроенной системы. ќна распознает, что у вас есть встроенна€ процессорна€ система и запустит Xilinx Studio (XPS).

–абота в XPS. —оздание встроенной системы на основе пустого проекта

1. ¬ XPS в открывшемс€ диалоговом окне согласитесь, что вы хотите создать систему на основе пустого проекта. ¬ы вручную добавите процессор к вашей системе.

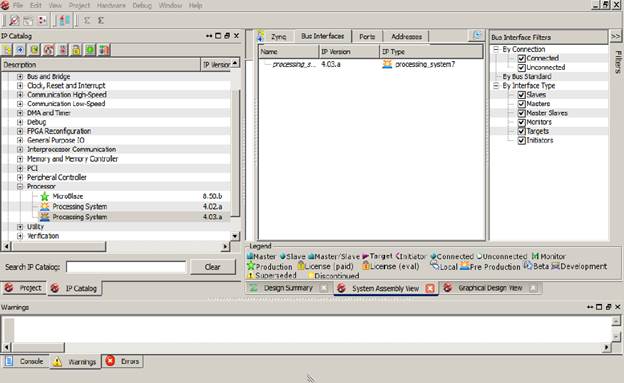

2. ¬ IP Catalog выберите Processor > Processing System, чтобы добавить его в систему. ќткроетс€ диалоговое окно, спрашивающее, хотите ли вы добавить экземпл€рprocessing_system7 4.03.a в вашу систему.

3. Ќажмите Yes, чтобы добавить экземпл€р процессора.

|

|

|

4. ѕерейдите на вкладку Bus Interfaces. «аметьте, что добавилс€processing_system7.

–исунок 1.XPS System Assembly View

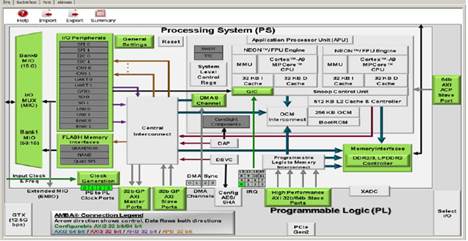

5. ѕерейдите на вкладку Zynq, чтобы открыть блок-схемуZynq Processing System.

–исунок 2.Zynq Processing System

ѕросмотрите содержимое блок-схемы. «еленым выделены блоки, которые могут настраиватьс€. ¬ы можете нажать на такой блок, чтобы открыть окно настройки.

6. Ќажмите на кнопку Import Zynq Configurations  . ќткроетс€ окно импорта конфигурации Zynq.

. ќткроетс€ окно импорта конфигурации Zynq.

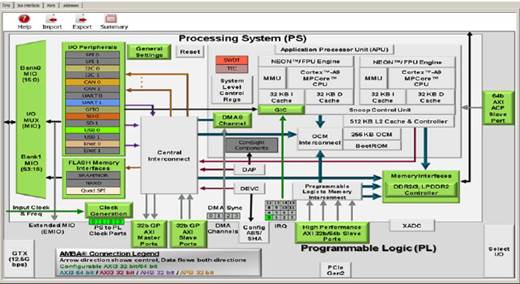

7. ¬ыберите конфигурационный шаблон (configuration template) дл€ платы ZC702. ѕо умолчанию выбран шаблон, наход€щийс€ в папке установки и соответствующий плате ZC702.

–исунок 3. ќкно выбора конфигурации Zynq

8. Ќажмите OK.

9. ¬ открывшемс€ окне с предупреждением, что будут обновлены Zynq MIO Configuration and Design, нажмите Yes.

10. «аметьте изменени€ в блок-схеме. ѕерифери€ ввода/вывода стала активной.

–исунок 4. ќбновленна€ блок-схема Zynq

11. «акройте окно Zynq PS MIO Configurations.

12. «акройте окно XPS. “екуща€ сесси€ программы PlanAhead применит изменени€ в настройках проекта.

Ёкспорт в SDK

¬ этой главе вы запустите SDK из PlanAhead.

1. Ќа панели ресурсов (Sources pane) под Design Sources, щелкните правойкнопкой мыши на system(system.xmp) и выберите Create Top HDL. PlanAhead сгенерирует system_stub.v Ц высокоуровневый модуль системы.

2. ¬ PlanAhead выберите File > Export > Export Hardware for SDK. ќткроетс€ окно экспорта аппаратной части (Export Hardware).

3. ќтметьте галочкой Launch SDK.

4. Ќажмите OK. ќткроетс€ SDK.

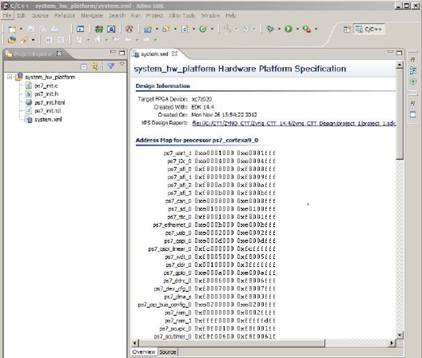

«аметьте, что файл описани€ аппаратуры автоматически считываетс€ при запуске SDK. ¬кладка system.xml показывает карту адресов всей системы.

–исунок 5. арта адресов на вкладке system.xml SDK

5. «акройте SDK.