÷»‘–ќ¬ќ√ќ ”—“–ќ…—“¬ј — »—ѕќЋ№«ќ¬јЌ»≈ћ я«џ ќ¬

ќѕ»—јЌ»я јѕѕј–ј“”–џ

—овременные методы и средства проектировани€ рассмотрим на примере разработки микропроцессорной системы, €вл€ющейс€ модернизацией более ранней разработки устройства на базе микроконтроллера ћ—S-51 (с целью сокращени€ объЄма примера описание будет упрощено относительно реальных условий). ѕереход на новую элементную базу в данном проекте прежде всего ограничиваетс€ естественным желанием проектировщика максимальным образом использовать ранее разработанные и проверенные решени€, в основном это касаетс€ фрагментов программного обеспечени€. ¬ состав системы должен входить двухканальный 10-разр€дный аналого-цифровой преобразователь, записывающий по запросу параллельный код в буферное ќ«” емкостью 256 дес€тиразр€дных слов, 8 входов и 28 выходов дл€ дискретных сигналов. »спользование схем класса —»— и ћ»— должно быть в модернизированном варианте минимизировано за счет использовани€ схем программируемой логики. дл€ определенности, кроме специально оговоренных случаев, будем ориентироватьс€ на микросхемы программируемой логики фирмы "Altera", а вследствие этого и на —јѕ– этой же фирмы ћј’ + PLUSII.

¬ј–»јЌ“џ –≈јЋ»«ј÷»» » ¬џЅќ– ЁЋ≈ћ≈Ќ“Ќќ… Ѕј«џ

–еализаци€ проекта возможна в различных альтернативных вариантах. —охранение задела по программному обеспечению заставл€ет обратитьс€ к вариантам, имеющим в качестве ћѕ-€дра тот или иной вариант контроллера ћ—S-51.

основным вариантам можно отнести следующие:

1) с использованием Ѕ»— класса Sќ–— geneгiс фирмы "Altera" и мегафункции (на пример, CAST) дл€ реализации ћѕ-€дра;

2) с использованием Ѕ»— класса Sќ–— фирмы "Triscend" семейства “≈5, содержащей в качестве ћѕ-€дра встроенный микроконтроллер 8052 и конфигурируемую логику типа FPGA;

3) с использованием микроконтроллера, совместимого по системе команд с ћ—S-51 со встроенными средствами аналого-цифровой обработки (например, Ѕ»— јDu—812 фирмы "Analog Devices" и с реализацией недостающих дискретных элементов в Ѕ»— ѕЋ фирмы "Altera".

4) с использованием обычного контроллера семейства ћ—S-51 автономных средств аналого-цифровой обработки и размещением всей дискретной части проекта в Ѕ»— ѕЋ фирмы "Altera".

–ассмотрим эти варианты более подробно.

1-й вариант реализации имеет укрупненную функциональную схему, соответствующую приведенной на рис. 8.12. ќснову проекта составл€ет Ѕ»— класса Sќ–— generic, конфигураци€ которой включает ћѕ-€дро (на базе стандартной мегафункции) и требуемую дополни- тельную логику: регистры выходные (Reg_A, Reg_B, Reg_BD), входной регистр (Reg_—), буферное ќ«” (RAM) и автомат, управл€ющий работой ќ«” (јvtRјћ). ѕомимо Ѕ»— ѕЋ схема содержит дополнительные элементы: »— врем€ задающего генератора (OSC), »— ѕ«” конфигурации (EEPROM Config), »— ѕ«” команд (EEPROM Instuction), »— аналогового коммутатора (MUX) и »— ј÷ преобразовател€ (ADC). ѕоскольку мегафункци€ микроконтроллера в этом варианте реализации требует (в зависимости от скоростных требований) от 2400 до 2860 логических €чеек, то проект потребует дл€ своей реализации Ѕ»— ѕЋ класса не ниже 10 50. —тоимость таких Ѕ»— превышает 80 дол. —Ўј, поэтому вариант вр€д ли экономически оправдан даже дл€ выпуска ќѕџ“Ќќ… партии устройств.

|

|

|

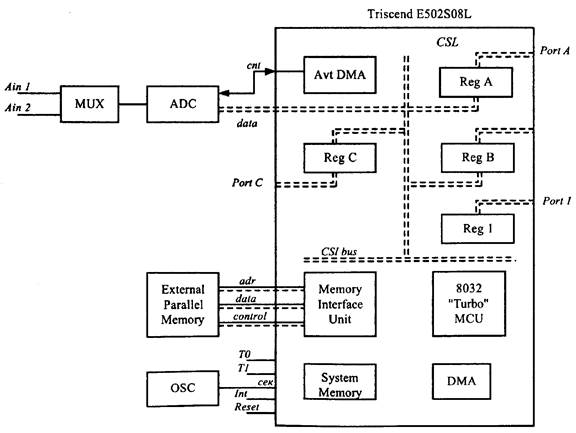

2-й вариант (рис. 8.13), опирающийс€ на продукцию фирмы "Triscend", потребует дл€ своей реализации помимо Ѕ»— семейства “≈5 четырех схем —»— (ќрганизаци€ Ѕ»— семейства “≈5 позвол€ет объединить в одной Ѕ»— ѕ«” ѕам€ть команд ћ и пам€ть конфигурации Ѕ»— ѕЋ Ч EEPROM). ¬ силу специфики организации Ѕ»— семейства “≈5 буферизацию данных от ј÷-преобразовател€ необходимо ¬џѕќЋЌя“№ непосредственно в пам€ти данных ћ и ориентироватьс€ при этом на встроенный контроллер пр€мого доступа к пам€ти. Ёта специфика приводит к необходимости модернизации ѕрограммного обеспечени€ процессорного €дра. Ѕлоки, реализуемые конфигурируемой системной Ћќ√» » (—31.) кристалла “≈5, функционально совпадают с блоками, размещенными в ¬»— ѕЋ предыдущего варианта. — экономической точки зрени€, основные затраты, по-видимому, будут касатьс€ не столько стоимости кристаллов (стоимость Ѕ»— семейства в зависимости от тактовой частоты и числа конфигурируемых €чеек системной логики может колебатьс€ от 18 до 100 дол. —Ўј), сколько стоимости покупки лицензии на —јѕ– и загрузочного оборудовани€, которое может достигать суммы пор€дка 650 дол. —Ўј (минимальные затраты около 170 дол. —Ўј).

3-й вариант реализации (рис. 8.14) €вл€етс€ самым экономичным по числу требуемых дл€ реализации числа микросхем. ќснову схемы образуют две Ѕ»— (Ѕ»— јduC812 фирмы "Analog Devices"и Ѕ»— ѕЋ ≈–’10K10 фирмы "Altera". Ѕ»— јduC812 фирмы "Anolog Devices" разработчики отнесли к классу микропреобразователей, поскольку Ѕ»— содержит на одном кристалле микроконтроллер, пам€ть, ј÷ѕ и ÷јѕ. ƒл€ реализации устройства дополнительно потребуетс€ одна Ѕ»— конфигурационного ѕ«” (EPROM) и одна »— врем€задающего генератора (ќS—). —труктура устройства, конфигурируемого в Ѕ»— ѕЋ, сохран€ет элементы предыдущих вариантов. ак и дл€ предыдущего варианта реализации, использование пр€мого доступа к пам€ти потребует модернизации программного обеспечени€ ћ . —тоимость Ѕ»— AduC812 фирмы"Anolog Devices" не превышает 12 дол.

—Ўј, но и стоимость Ѕ»— ≈–’10K10 фирмы "Altera" близка к 20 дол. —Ўј. ѕриобретение средств, сопровождающих разработку, может потребовать затрат, не превышающих 100 дол. —Ўј. ¬ариант имеет предопределенные характеристики по скорости работы ј÷ѕ и экономически проигрывает следующему варианту.

4-й вариант реализации (рис. 8.15) предполагает использование в качестве ћѕ-€дра классической микросхемы ћCS-51 (в примере Ѕ»— ј“89—51 фирмы "Atmel" и применени€ Ѕ»— ѕЋ ≈–’10K10 дл€ реализации недостающих дискретных компонентов. ќсновным достоинством варианта €вл€етс€ возможность без каких-либо переделок использовать старое программное обеспечение. »менно это и позвол€ет остановитьс€ дл€ дальнейшей работы на этом варианте. ¬ыбор дл€ реализации 2-го или 3-го вариантов целесообразен только в том случае, если разработчик готов потратить врем€ и деньги на модернизацию программного обеспечени€. ¬ св€зи с наличием целого р€да особенностей при проектировании устройства на базе Ѕ»— класса Sќ–— после подробного рассмотрени€ процедуры проектировани€ дл€ выбранного варианта реализации приведем наиболее существенные отличи€ в проектной последовательности дл€ реализации проекта на базе Ѕ»— фирмы "Triscend".

|

|

|

ѕосле выбора варианта реализации устройства в целом можно переходить к детализации технического задани€ на проектирование Ѕ»— ѕЋ.

–ис. 8.12. ¬ариант реализации проекта на Ѕ»— ѕЋ класса Sќ–— generic

–ис.8.13. ¬ариант реализации проекта на Ѕ»— ѕЋ класса Sќ–— “≈5

–ис.8.14. ¬ариант реализации проекта на Ѕ»— јDuC812 и Ѕ»— ѕЋ ≈–’10K10

–ис.8.15. ¬ариант реализаци. и проекта на Ѕ»— ј“89—51 и Ѕ»— ѕЋ ≈–X10K10

ѕ–ќ≈ “»–ќ¬јЌ»≈ Ѕ»— ѕЋ

Ётап 1. ‘ормирование требований на проектирование Ѕ»— ѕЋ

основным требовани€м следует отнести:

Х объем буферного ќ«” 256 дес€тиразр€дных слов;

Х запись в ќ«” осуществл€етс€ блоками (с чередованием данных от различных каналов) по запускающему сигналу RequstADC,формируемому внешней средой;

Х после завершении записи блока оцифрованных данных во внутренний буфер ѕЋ информирует ћ об этом, выставл€€ сигнал ReadyData;

Х сигнал ReadyData €вл€етс€ источником прерывани€ дл€ ћ ;

Х чтение данных из буферного ќ«” ѕЋ осуществл€етс€ по инициативе ћ путем последовательного считывани€ сначала восьми, а затем двух битов данных;

Х помимо работы с буферным ќ«” Ѕ»— ѕЋ должно поддерживать формирование адреса дл€ внешнего ѕ«” команд ћ (Reg_C);

Х Ѕ»— ѕЋ реализует функции двух выходных 8-разр€дных портов (Reg_A и Reg_B) и одного входного 8-разр€дного порта (Reg_C);

ѕеречисленные выше пункты “« предопредел€ют основные блоки проектируемой Ѕ»— и их взаимодействие. Ѕлочна€ схема устройства приведена на рис. 8.16. ‘ункциональное назначение блоков следует из их названий. —хема укрупненно отображает следующие процессы:

запись данных от ћ (Data[7..0] по сигналу ALE в регистр адреса ѕ«” команд;

запись данных от ћ по сигналу WR (при установленных в "1" 6-го и 7-го разр€дов порта –2 ћ ) в зависимости от адреса ј0 ј1 в порт –ј или –¬;

чтение данных в ћ по сигналу RD (при установленных в "1" 6-го и 7-го разр€дов порта –2 ћ ) при адресе не ј0 и ј1 из порта –—;

запись блока данных от аналого-цифрового преобразовател€ в буферное ќ«”; считывание данных из буферного ќ«” в ћ ;

готовность ѕЋ к передаче данных индицируетс€ сигналом ReadyData.

Ётап 2. –азработка общей структуры операционного блока

Ќетрудно видеть, что дл€ реализации рассматриваемого устройства из состава библиотеки выбранной —јѕ– можно использовать следующий набор библиотечных параметризируемых модулей (L–ћ):

Х два блока ќ«” (L–ћ_RAM_DQ) с организацией 25б х 8 и 256 х 2;

Х 8-разр€дный счетчик адреса ќ«” (L–ћ_COUNTER);

Х три модул€ триггеров типа D (L–ћ_DFF), организованных в 8-разр€дные регистры.

ѕон€тие параметризированных модулей соответствует возможности настроить выбранный библиотечный элемент на определенный режим функционировани€, на определенную разр€дность данных, их пол€рность и т. д. ¬ качестве 8-разр€дных регистров можно использовать и специально разработанные блоки на базе примеров, описанных выше.

—труктурна€ схема устройства, включающа€ эти операционные блоки и автомат, управл€ющий считыванием и записью кода из ќ«”, может приобрести вид, приведенный на рис. 8.17. роме указанных выше базовых блоков в схеме присутствует р€д дополнительных элементов. ”словные обозначени€ всех элементов схемы соответствуют стандарту, прин€тому в —јѕ– ћј’ + –LUS II. Ќеобходимость введени€ дополнительных элементов (инверторов, D-триггеров и схем ») диктуетс€ требовани€ми временной или аппаратной совместимости отдельных блоков схемы. Ѕолее подробные по€снени€ будут приведены в следующем разделе, поскольку этапы разработки операционной части и устройства управлени€ операционными элементами тесно св€заны и обычно выполн€ютс€ итерационно.

–ис. 8.16. Ѕлок-схема устройства, прин€того в качестве примера дл€ проектировани€ средствами —јѕ–

Ётап 3. ќписание работы управл€ющего автомата

|

|

|

ѕри разработке поведени€ управл€ющего автомата необходимо учесть, что функционирование устройства определ€етс€ сигналом —Lќ— и происходит асинхронно относительно внешнего устройства, управл€ющего чтением и записью в ќ«” и относительно другого внешнего устройства, запрашивающего и принимающего информацию в последовательной форме.

ѕри выборе из библиотеки —јѕ– в качестве ќ«”-модулей типа LPM_RAM_DQ (т. е. с раздельными шинами чтени€ и записи данных) и при его настройке на асинхронный режим работы исчезает целый р€д проблем. ¬о-первых, нет необходимости введени€ элементов, раздел€ющих данные дл€ записи и считывани€. ¬о-вторых, существенно упрощаетс€ организаци€ синхронизации работы управл€ющего автомата при записи данных в ќ«” с асинхронно работающим ј÷ѕ.

¬озможный алгоритм работы устройства управлени€ разрабатываемого устройства, отвечающий сформулированным выше требовани€м, может приобрести вид соответствующий граф-схеме переходов автомата, приведенной на рис. 8.18. √раф-схема переходов при помощи графического редактора программы StateCAD Version 3.2 пакета Workview Office фирмы "Viewlogic" была занесена в соответствующий диаграммный файл, что, как будет показано далее, существенно упрощает не только отладку и возможные корректировки алгоритма, но и создание соответствующих программных текстов.

ѕерейдем к анализу автомата CntRAM управл€ющего записью и считыванием данных в буферное ќ«” и поддерживающего дл€ этих обменов требуемое взаимодействие квитирующими сигналами.

ќснову алгоритма составл€ют два последовательно выполн€емых блока.

ѕервый блок по сигналу запроса на преобразование ReqADC от внешнего устройства обеспечивает циклическое выполнение следующей последовательности действий. ¬ со сто€нии автомата (StartWr) выставл€етс€ сигнал запуска преобразовател€ (StartADC), дождавшись сигнала готовности данных от ј÷ѕ (ReadyADC), считывает 10 бит данных и записывает их (в состо€нии WrData) в пам€ть (формиру€ сигнал WE).ќб окончании приема данных ј÷ѕ узнает благодар€ сбросу запроса на преобразование, затем автомат наращивает адрес ќ«” (формиру€ в состо€нии IncWr сигнал IncAdr). ѕризнаком завершени€ приема блока данных €вл€етс€ сигнал ћах, формируемый на основании анализа состо€ни€ счетчика адреса ќ«”.

ѕо завершении записи блока данных автомат в состо€нии Pause1 выставл€ет сигнал заполнении ќ«” данными ReadyData и сбрасывает счетчик адреса ќ«” (сигнал ResAdr),

подготавлива€ его тем самым к циклу считывани€ данных в ћ . Ётот цикл и составл€ет основу второго блока выполн€емых автоматом действий. ѕоскольку формирование сигналов открыти€ выходных буферов CsADCH и CsADCL выполн€етс€ внешними относительно автомата цеп€ми, основной задачей блока €вл€етс€ выполнение последовательности действий, котора€, обнаружив два последовательно выставленных внешних сигнала автомата Rd, формирует сигнал IncAdr, обеспечивающий переход к следующему адресу. „исло требуемых итераций цикла, как и в первом блоке, подсчитывает счетчик адреса. —ледует обратить внимание на петли ожидани€ в состо€ни€х WaitRd, RdByte1, Pause2, RdByte2 наличие которых обеспечивает требуемую синхронизацию.

ƒл€ правильной работы автомата асинхронные сигналы ReqADC, ReadyADC и Rd требуют их предварительного запоминани€ в дополнительно введенных в схему D-триггерах. “актирование D-триггеров сигналами nClock т. е. задним фронтом сигнала (при условии, что автомат тактируетс€ передним фронтом сигнала Clock),гарантирует четкую работу автомата. ƒл€ устранени€ паразитных врезок у выходного сигнала автомата ReadyData (которые могут вызывать ошибочные действи€ системы прерываний микроконтроллера) также используетс€ D-триггер, тактируемый сигналом nClock.

|

|

|

ƒадим некоторые по€снени€ к синтаксису VHDL-программы устройства управлени€.

ƒл€ автомата приведенного примера с помощью программы StateCAD Version 3.2 пакета Workview Office была выполнена трансл€ци€ диаграммы (дл€ разных вариантов €зыкового описани€). Ѕыл создан вариант, ориентированный на возможности €зыка описани€ аппаратуры на €зыке высокого уровн€ VHDL (листинг 1).

–ис. 8.18. √раф-схема переходов автомата управлени€

ѕри компил€ции из графической формы в текстовую программа StateCAD учитывает, дл€ компил€тора какой фирмы предполагаетс€ использовать описание автомата (соответствующим образом выбира€ используемые синтаксические конструкции). јналогичные соображени€ должны приниматьс€ во внимание и при ручном написании программ. Ёто ограничение возникает из-за того, что набор допустимых синтаксических конструкции €зыка дл€ различных фирм существенно отличаетс€ от стандартного. ƒл€ примера выбрана ориентаци€ на —јѕ– Synopsys (как имеющую меньшие ограничени€).

Ћистинг 1

Ч VHDL code created by Visual Solution's StateCAD Version 3.2

ЧThis VHDL code (for use with Synopsys) was generated using:-enumerated state assignment with structured code format.

Ч Minimization is enabled,implied else is enabled,

Чand outputs are manually optimized.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY synopsys;

USE synopsys.attributes.all;

ENTITY CntRAM IS

–ќR“ (CLK,Max,Rd,ReadyADC,Reset:IN std_logic;

IncAdr,ReadyData.ResAdr,StartADC,We:OUT std_logic);

END;

ARCHITECTURE BEHAVIOR OF CntRAM IS

“Y–≈ type_sreg IS(AdrNew,EndLoop,Idle,IncWr,Pause1, Pause2, Pause3,RdByte1,

RdByte2,StartWr,WaitWr,WrData);

SIGNAL sreg,next_sreg:type_sreg;

BEGIN

PROCESS (CLK)

BEGIN

IF CLK='1' AND CLK'event THEN

IF (Reset='1') THEN

sreg<=idle;

ELSE

sreg<=next_sreg;

END IF;

END IF;

END PROCESS;

PROCESS(sreg,Max,Rd,ReadyADC,ReqADC,Reset)

BEGIN

IncAdr<="0";ReadyData<="0";ResAdr<="0";

StartAdc<="0";We<="0";

next_sreg<=AdrNew;

IF(Reset='1') THEN

next_sreg<=Idle;

IncAdr<='0';ReadyData<='0';StartADC<='0';

We<='0';ResAdr<='1';

ELSE

CASE sreg IS

WHEN AdrNew=>

ResAdr<='0';StartADC<='0';

We<='0';

IncAdr<='1';ReadyData<='1';

next_sreg<=Pause3;

WHEN Idle=>

IncAdr<='0';ReadyData<='0';

StartADC<='0';

We<='0';ResAdr<='1';

IF (ReqADC='1') THEN

next_sreg<=StartWr;

END IF;

WHEN IncWr=>

ReadyData<='0';ResAdr<='0';

StartADC<='0';

We<='0';IncAdr<='0';

IF (Max='0') THEN

next_sreg<=StartWr;

END IF;

IF (Max='1') THEN

next_sreg<=Pause1;

END IF;

WHEN Pause1=>

IncAdr<='0';StartADC<='0';

We<='0';

ResAdr<='1';ReadyData<='1';

next_sreg<=WaitRd;

WHEN Pause2=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=Pause2;

END IF;

F(RD='1') THEN

next_sreg<=RdByte2;

END IF;

WHEN Pause3=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Max='1') THEN

next_sreg<=Idle;

END IF;

IF (Max='0') THEN

next_sreg<=WaitRd;

END IF;

WHEN RdByte1=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=Pause2;

END IF;

IF (Rd='1') THEN

next_sreg<=RdByte1;

END IF;

WHEN RdByte2=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='0') THEN

next_sreg<=AdrNew;

END IF;

IF (Rd='1') THEN

next_sreg<=RdByte2;

END IF;

WHEN StartWr=>

IncAdr<='0';ResAdr<='0';

StartADC<='1';

We<='0';ReadyData<='0';

IF (ReadyADC='1') THEN

next_sreg<=WrData;

END IF;

IF (ReadyADC='0') THEN

next_sreg<=StartWr;

END IF;

WHEN WaitRd=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='0';ReadyData<='1';

IF (Rd='1') THEN

next_sreg<=RdByte1;

END IF;

IF (Rd='0') THEN

next_sreg<=WaitRd;

END IF;

WHEN WrData=>

IncAdr<='0';ResAdr<='0';

StartADC<='0';

We<='1';ReadyData<='0';

next_sreg<=IncWr;

WHEN OTHERS=>

END CASE;

END IF;

END PROCESS;

END BEHAVIOR;

–азделы проектного модул€ типичны дл€ €зыка VHDL. ¬ самом начале перечисл€ютс€ используемые в проекте библиотеки (IEEE и Synopsys). ¬ заголовочном разделе EN“I“Y перечислены имена и типы всех сигналов: входных внешних управл€ющих сигналов Ч тактового сигнала (CLK), сигнала окончани€ блока данных (ћах), запросов на чтение и запись блока данных (Rd и ReqADC) соответственно, флага готовности ј÷ѕ (ReadyADC) и, наконец, начального сброса(Reset) и выходных управл€ющих сигналов сигнала запуска ј÷ѕ (StartADC),сигналов управлени€ счетчиком адреса (IncAdr,ResAdr), сигнала управлени€ режимом записи буферного ќ«” (We) и внешним выходным сигналом (ReadyData).

|

|

|

—ледующий раздел ЧARCHITECTURA Ч представл€ет собой описание архитектуры или поведени€ (в нашем случае поведени€) блока, интерфейс которого был описан в ENTITY.

ак и в обычных €зыках, в начале раздела даетс€ описание типов и объ€вление переменных, используемых при описании действий, выполн€емых в разделе ARCHITECTURA.

¬ данном автомате определен перечислительный тип данных type_sreg со всем списком допустимых значений (они, естественно, совпадают с именами, введенными в граф схеме переходов). ƒалее в тексте объ€влены два сигнала Ч sreg и next_sreg введенного типа tуре_sreg. ¬ведение двух сигналов св€зано с необходимостью определени€ текущего и следующего состо€ний автомата при переходе от одного состо€ни€ к другому.

√лавна€ часть архитектурного тела содержит два оператора параллельного типа (процесса). ѕервый процесс запускаетс€ на исполнение каждый раз, когда происходит изменение сигнала CLK. ќднако его основное действие назначение автомату нового состо€ни€ Ч происходит только по переднему фронту сигнала CLK. »спользование дл€ тактировани€ автомата переднего фронта синхронизирующего сигнала (предложение IF CLK='1' AND CLK'event THEN sreg<=next_sreg;END IF;) служит дл€ синхронизации выбранных библиотечных операционных узлов и обеспечит стабильность входных управл€ющих сигналов в моменты тактировани€. ѕри составлении программы автомата учитывалась необходимость его установки в исходное состо€ние при подаче сигнала сброса (выражение IF(Reset='1') THEN sreg<=Idle;).

ѕоведение управл€ющего автомата в тексте программы задано вторым процессом.

¬торой процесс запускаетс€ каждый раз, когда измен€етс€ состо€ние автомата (sreg) или измен€етс€ какой-либо входной сигнал. —одержимое этого процесса и определ€ет поведение управл€ющего автомата. онечные автоматы в €зыке VHDL удобно описывать посредством оператора выбора "CASE", использу€ в качестве ключа выбора варианта переменную состо€ни€ автомата в текущий момент времени. ¬нутри каждого варианта определ€етс€ состо€ние перехода и значени€ выходных сигналов, формируемых в соответствии с входными услови€ми. —осто€ние перехода из текущего состо€ни€ в следующее осуществл€етс€ с помощью оператора назначени€ переменной next_sreg нового значени€. ¬ тех случа€х, когда переход из текущего состо€ни€ зависит от внешних сигналов, этот оператор назначени€ входит в состав условного оператора, логическое выражение которого совпадает с последовательностью условий, встречающихс€ на соответствующих пут€х переходов на схеме алгоритма. јналогично определ€ютс€ и выходные сигналы, вырабатываемые на переходах и задающие исполн€емые в других блоках операции.

Ётап 4. омпил€ци€ проекта и основные параметры устройства

ѕосле создани€ всех фрагментов проекта и схемы проекта в целом выполн€етс€ его компил€ци€. Ќеобходимость иметь буферное ќ«” и требуемый объем ќ«” (реализаци€ ќ«” в форме совокупности отдельных D-триггеров потребовала бы значительных логических затрат) предопределила целесообразность выбора в качестве основы реализации Ѕ»— ѕЋ семейства FLEX 10K (с организацией пам€ти конфигурации в форме SRAM). ќриентаци€ пам€ти конфигурации на пам€ть типа 8 заставила ввести в состав устройства специальную Ѕ»— ѕ«”, хран€щую загружаемую при выключении питани€ пам€ть конфигурации. ѕосле успешной компил€ции был получен файл отчета (*.грt), показавший, что данный проект далеко не полностью использует возможности, предлагаемые самым младшим представителем семейства 10 Ѕ»— EPF10K10TC44. ќбщие затраты Ѕ»— (по числу логических €чеек) на реализацию проекта компил€тор определил всего как 17%. ѕравда, на реализацию модул€ ќ«” компил€тор использовал 66% имеющихс€ у Ѕ»— ресурсов. „исло задействованных контактов ввода/вывода составл€ет 62, что не позволило остановитьс€ на предыдущем типоразмере корпуса Ѕ»—.

Ётап 5. “естирование проекта

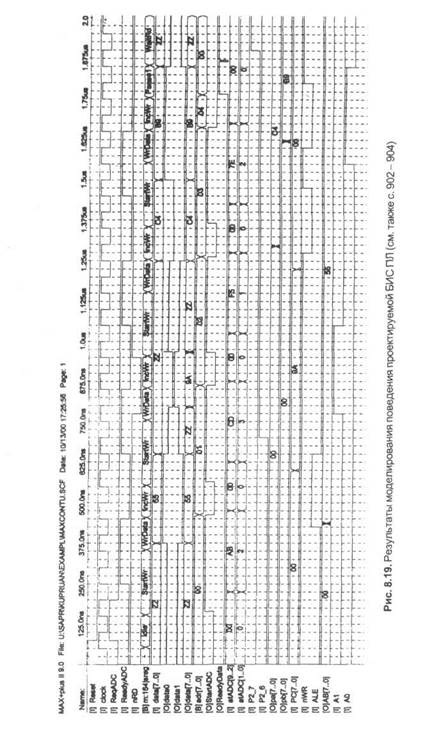

“естирование проекта также выполн€лось средствами —јѕ– ћј’ + PLUS||. —озданна€ тестова€ последовательность должна была провер€ть лишь ключевые моменты работы разработанного устройства. –езультаты моделировани€ приведены на рис. 8.19. дадим по€снени€ основным фрагментам моделировани€.

—истемное врем€ Ч в интервале от 0 до 0,075 мкс. –ежим начального сброса устройства. ѕроверка всех возможных исходных ситуаций перед сбросом весьма громоздка и в данном примере эти варианты из соображений большого объема не включены.

—истемное врем€ Ч в интервале от 0,075 до 0,2 мкс. ћоделирование по€влени€ внешнего сигнала запроса (ReqADC) на запись в ќ«” блока данных от ј÷ѕ. ƒл€ сокращени€ временной диаграммы моделирование осуществл€лось дл€ упрощенной схемы (сигнал ћах формируетс€ после записи всего четырех адресов).

¬ интервале системного времени от 0,15 до 0,45 мкс в ответ на сигнал запуска цикла аналого-цифрового преобразовани€ (StartADC) ј÷ѕ выставил сигнал готовности данных (ReadyADC), и это служит основой дл€ записи в ќ«” по адресу 00 данных, равных ј¬ и 2 (здесь, как и далее, значени€ всех адресов и данных будут даны в шестнадцатиричной системе счислени€).

ќт значени€ системного времени 0,45 до значени€ 1,75 мкс выполн€етс€ еще три записи в ќ«” данных: (CD 3), (F5 1) и (7≈ 2) по адресам ќ«” 1, 2 и 3.

¬виду аппаратной независимости записи в ќ«” и работы периферии ћ одновременно с моделированием записи блока данных в ќ«” осуществл€лось моделирование:

Х фиксации в момент системного времени 0,45 мкс старшей части адреса внешнего ѕ«” Ч по сигналу јL≈ фиксировалось на выходе 8-разр€дного регистра ј¬ значение 55, выставленное на шине данных ћ ;

Х фиксации в момент системного времени 1,3 мкс в триггерах порта –ј значени€ —4 (следствие по€влени€ сигнала nWRпри услови€х –2_б – = 1, 2_7 0, ј0 =0 и ј1 = 0);

Х фиксации в момент системного времени 1,625 мкс в триггерах порта –¬ значени€ ¬9 (следствие по€влени€ сигнала nWR при услови€х –2_6 – = 1, 2_7 = 0, ј0 = 1 и ј1 = 0).

огда системное врем€ достигло значени€ 1,75 мкс, автомат выставил сигнал о готовности данных в буфере (ReadyData) и перешел в режим ожидани€ блока сигналов считывани€ из буферного ќ«” в ћ . ¬ ответ на сигналы nRD с соответствующими значени€ми сигналов –2_6 и –2_7 в интервалы системного времени (2,0 2,325), (2,675 3,05), (3,575 3,9), (4,325 4,75), (5,15 5,575), (5,85 6,25), (6,65 6,950) и (7,275 7,675) осуществл€етс€ выдача данных, сохраненных в буферном ќ«”, на шину данных ћ .

|

|

|

|

ѕризнаком окончани€ передачи блока данных служит сброс сигнала ReadyData и переход автомата в состо€ние Idle (в примере это происходит после 7,95 мкс).

јнализ временных диаграмм позвол€ет не только проверить правильность функционировани€ устройства, но и исследовать временное поведение отдельных элементов проекта и прежде все определить и проконтролировать выполнение в реальной системе требуемого времени удержани€ некоторых сигналов.

Ётап 6. јвтоматическое определение временных параметров устройства

¬озможности —јѕ– вычисл€ть временные соотношени€ между различными фрагментами проекта существенно облегчает проектировщику задачу проверки правильности работы проекта во временной области. јвтоматизаци€ этого этапа проектировани€ избавл€ет от необходимости ручного перебора исходных данных проекта с целью обнаружени€ отклонении от допустимых временных установок.

Ётап 7. ѕрактическа€ проверка результатов проектировани€

ќсновным результатом работы компил€тора €вл€етс€ файл конфигурации Ѕ»—, соответствующий техническому заданию. —редства —јѕ– позвол€ют на заключительных этапах работы поместить содержимое этого файла в интересующую проектировщика Ѕ»—, и на этом процесс проектировани€ может быть переведен в плоскость натурных экспериментов, дл€ рассматриваемого примера натурные эксперименты производились с использованием специального отладочного стенда, содержащего две Ѕ»— ѕЋ типа 10 10. ќдна Ѕ»— использовалась дл€ загрузки конфигурации проектируемой схемы, а друга€ Чдл€ загрузки конфигурации автомата, создающего тестовые воздействи€, совпадающие с тестовыми воздействи€ми модельного эксперимента. Ѕлагодар€ соединению контактов Ѕ»— между собою возможно наблюдение за работой спроектированной Ѕ»— на экране осциллографа в режимах, отличающихс€ от реальных условий только моделированием этих условий. Ёксперименты позвол€ют убедитьс€ в правильности созданного файла конфигурации (или вернутьс€ на начальные этапы проектировани€ Ѕ»— ѕЋ) и перейти к следующему уровню проектировани€ Ч проектированию печатной платы, содержащей требуемые элементы проектируемой системы. ѕоскольку в проектируемой системе дл€ загрузки конфигурации в Ѕ»— ѕЋ ≈–’10 10 предполагаетс€ использовать специальную загрузочную Ѕ»— типа ≈–—, то практическим результатом этого этапа можно считать программирование последовательного загрузочного ѕ«” (например, типа ≈–—1 –—8 фирмы "Altera").