“аймер Ї одним з головних пристроњв, €к≥ вход€ть до складу цього блока ≥ призначений задл€ формуванн€ певних часових ≥нтервал≥в. Ќеобх≥дн≥сть введенн€ таймера до складу блока перифер≥йних пристроњв зумовлено призначенн€м ћ дл€ керуванн€ певними обТЇктами та процесами.

ƒо складу ћ ћ— 68 Ќ— 705 J 1 ј входить 15-розр€дний багатофункц≥ональний таймер MFT, структурну схему котрого подано на рис. 13.12.

–исунок 13.12 Ц —труктурна схема багатофункц≥онального таймера

Ѕагатофункц≥ональний таймер побудований на баз≥ 15-розр€дного л≥чильника, 8 молодших розр€д≥в котрого €вл€ють собою програмно-доступний рег≥стр-таймер TCR (адреса $09), а 7 старших розр€д≥в використовуютьс€ €к под≥льник частоти при формуванн≥ пер≥одичних переривань. ƒл€ контролю за роботою таймера використовуЇтьс€ вм≥ст рег≥стра-таймера, €кий може бути прочитано за будь-€кого моменту часу. ¬их≥д старшого, 7-го, б≥та може використовуватис€ задл€ перериванн€ роботи таймера через кожн≥ 1024 пер≥оди тактовоњ частоти. „астота роботи л≥чильника становить Fc = Ft / 4.

¬артовий таймер Ц —ќ– (Computer operation property), €кий входить до складу багатофункц≥онального таймера, призначено задл€ контролю за роботою програмного забезпеченн€ ≥ реал≥зац≥њ переривань через певн≥ в≥дл≥ки часу.

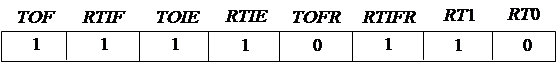

ƒо складу багатофункц≥онального таймера MFT також входить рег≥стр керуванн€-стану TSCR (адреса $08), формат котрого подано на рис. 13.13.

|

–исунок 13.13 Ц ‘ормат рег≥стра керуванн€-стану TSCR

Ѕ≥ти цього рег≥стра в≥дпов≥дають певним ознакам, використовуютьс€ дл€ керуванн€ роботою таймера ≥ мають таке призначенн€:

Ц TOIE (Timer Overflow Interrupt Enable) Ц ознака дозволу перериванн€ переповнюванн€;

Ц TOF (Timer Overflow Flag) Ц ознака переповнюванн€. «наченн€ TOF = 1 встановлюЇтьс€ при зм≥н≥ вм≥сту рег≥стра-таймера з $ FF на $00. якщо, при цьому ознака дозволу перериванн€ переповнюванн€ встановлена TOIE = 1, то в≥дбуваЇтьс€ перериванн€ роботи ћ . ќтже, перериванн€ переповнюванн€ може в≥дбуватис€ через кожн≥ 210 = 1024 пер≥оди тактовоњ частоти;

Ц RTIF (Real-Time Interrupt Flag) Ц ознака пер≥одичного перериванн€;

Ц RTIE (Real-Time Interrupt Enable) Ц ознака дозволу пер≥одичного перериванн€;

Ц TOFR (Timer Overflow Flag Reset) Ц б≥т скиданн€ ознаки переповнюванн€. «апис 1 до цього б≥та п≥сл€ перериванн€ дозвол€Ї встановленн€ ознаки TOF = 0;

Ц RTIFR (Real-Time Interrupt Flag Reset) Ц б≥т скиданн€ ознаки пер≥одичного перериванн€. «апис 1 до цього б≥та п≥сл€ перериванн€ дозвол€Ї встановленн€ ознаки RTIF = 0;

Ц RT 1-0 (Real-Time Interrupt) Ц б≥ти, що встановлюють часов≥ ≥нтервали встановленн€ ознаки пер≥одичного перериванн€. «наченн€ RTIF = 1 встановлюЇтьс€ через ≥нтервали, визначуван≥ в≥дпов≥дно до вм≥сту цих б≥т≥в:

| RT 1-0 | ѕер≥од встановленн€ ознаки RTIE |

| Tp = 2Ј14 Tt | |

| Tp = 2Ј15 Tt | |

| Tp = 2Ј16 Tt | |

| Tp = 2Ј17 Tt |

¬икористовуванн€ багатофункц≥онального таймера MFT дозвол€Ї виконувати вим≥рюванн€ часових ≥нтервал≥в пом≥ж певними под≥€ми, формуванн€ сигнал≥в з певною затримкою, пер≥одичний виклик потр≥бних п≥дпрограм, формуванн€ ≥мпульс≥в потр≥бноњ частоти та довжини, а також формувати сигнали внутр≥шн≥х переривань в≥д вартового таймера.

|

|

|

ƒо складу ≥нших ћ с≥мейства можуть входити таймерн≥ блоки з р≥зною орган≥зац≥Їю дл€ керуванн€ певними обТЇктами. Ѕ≥льш≥сть з них побудовано на баз≥ 16-розр€дного таймерного блока, котрий доповнюЇтьс€ 8-розр€дним л≥чильником-таймером та 14-розр€дним базовим таймером. ƒо складу ћ ћ— 68 Ќ— 705 ¬ 16 також вход€ть два широтно-≥мпульсних модул€тори, котр≥ можуть формувати посл≥довн≥сть ≥мпульс≥в з програмованою шпаруват≥стю.

—≥мейство ћ68Ќ—08/908

—≥мейство ћ 68 Ќ— 08/908 Ї подальшим розвиненн€м ћ ћ 68 Ќ— 05/705. ¬они збер≥гають њхн≥ арх≥тектурн≥ особливост≥, однак дозвол€ють п≥двищувати техн≥ко-економ≥чн≥ характеристики пристроњв, до складу котрих вони вход€ть. ƒо складу ћ п≥дс≥мейства ћ 68 Ќ— 908 входить Flash -памТ€ть, що дозвол€Ї широко використовувати його у пристро€х, €к≥ випускаютьс€ малими сер≥€ми. ѕрограмна сум≥сн≥сть з ћ ћ 68 Ќ— 05/705 дозвол€Ї використовувати програмне забезпеченн€, розроблене дл€ них задл€ програмного керуванн€ новими пристро€ми.

—ьогодн≥ випускаЇтьс€ ≥ рекомендовано дл€ використовуванн€ понад 30 моделей ћ цього с≥мейства, €к≥ в≥др≥знюютьс€ складом паралельних ≥ посл≥довних порт≥в, а також перифер≥йного обладнанн€.

ƒо складу ћ с≥мейства ћ 68 Ќ— 08/908 вход€ть: процесорне €дро CPU 08; внутр≥шн€ памТ€ть програм Ц ѕ«ѕ, програмований маскою, обс€гом до 32 кбайт або Flash -памТ€ть, обс€г котроњ становить 60 кбайт; ќ«ѕ даних, €кий маЇ Їмн≥сть в≥д 128 байт до 2 кбайт. ¬ де€ких модел€х Ї –ѕ«ѕ-≈— обс€гом 512 байт або 1 кбайт.

«алежно в≥д функц≥онального призначенн€ ћ , до њхнього складу може входити в≥д 5-ти до 8-ми паралельних порт≥в, посл≥довн≥ порти SCI та SPI. ƒо складу ћ де€ких сер≥й вход€ть спец≥ал≥зован≥ посл≥довн≥ порти, призначен≥ дл€ орган≥зац≥њ м≥кроконтролерних мереж. “ак≥ ћ зреал≥зовують обм≥н даними по мультиплексован≥й шин≥ J 1850, зреал≥зовують ≥нтерфейс з посл≥довною шиною USB ≥ спец≥ал≥зован≥ ≥нтерфейсн≥ модул≥ CAN та I 2 C. ћ сер≥њ EY вм≥щуЇ посл≥довний порт ESCI, €ки зреал≥зовуЇ протокол LIN задл€ обм≥ну даними однопров≥дною л≥н≥Їю звТ€зку.

ƒо складу перифер≥йних пристроњв вс≥х ћ с≥мейства ћ 68 Ќ— 08/908 вход€ть 16-розр€дн≥ таймери. Ѕ≥льш≥сть моделей вм≥щуЇ 8- або 10-розр€дн≥ ј÷ѕ.

ќкр≥м того, ћ сер≥њ LD мають спец≥альн≥ виходи сигнал≥в синхрон≥зац≥њ ≥ використовуютьс€ дл€ керуванн€ цифровими мон≥торами, а ћ сер≥њ RF мають у своЇму склад≥ рад≥опередавач.

’арактерною особлив≥стю побудови ћ цього с≥мейства Ї побудова ћ з≥ стандартним набором модул≥в (модульний принцип). ѕоЇднанн€ окремих модул≥в на одному кристал≥ надаЇ змогу формувати ћ р≥зноман≥тного функц≥онального призначенн€.

«агальну структурну схему ћ цього с≥мейства наведено на рис. 13.14. ƒо складу ц≥Їњ схеми вход€ть стандартн≥ модул≥, кожен з котрих маЇ власне функц≥ональне призначенн€.

|

–исунок 13.14 Ц «агальна структурна схема ћ с≥мейства ћ 68 Ќ— 08/908

онф≥гуруванн€ ћ визначаЇтьс€ вм≥стом рег≥стр≥в конф≥гуруванн€, котр≥ зумовлюють характеристики м≥кроконтролера. ћ п≥дс≥мейства ћ 68 Ќ— 08 у своЇму склад≥ мають рег≥стри конф≥гуруванн€ MOR, €к≥ Ї ком≥рками ѕ«ѕ ≥ њхнЇ програмуванн€ зд≥йснюЇтьс€ у переб≥гу виготовл€нн€ м≥кросхеми.

|

|

|

–ег≥стри конф≥гуруванн€ CONFIG п≥дс≥мейства ћ 68 Ќ— 908 треба програмувати при кожному запусков≥ ћ , а упродовж сеансу роботи њхн≥й вм≥ст залишаЇтьс€ незм≥нним.

‘ормат вм≥сту рег≥стр≥в CONFIG 1 та CONFIG 2 дл€ ћ сер≥й ћ 68 Ќ— 908 JK 1, JK 3 та JL 3 подано на рис. 13.15.

Ѕ≥ти рег≥стра CONFIG 1 призначено дл€ виконуванн€ таких функц≥й:

Ц COPRS Ц використовуЇтьс€ дл€ керуванн€ роботою вартового таймера ≥ визначаЇ пер≥од його роботи;

Ц LVID Ц використовуЇтьс€ дл€ дозволу роботи модул€ контролю живленн€; значенн€ LVID = 1 заборон€Ї роботу цього модул€;

Ц SSREC Ц визначаЇ час затримки Td при виход≥ ћ з режиму зупину; при значенн≥ SSREC = 1 час затримки дор≥внюЇ Td = 32Ј Tq ≥ Td = 4096Ј Tq Ц при встановленн≥ SSREC = 0;

|

–исунок 13.15 Ц ‘ормат вм≥сту рег≥стр≥в конф≥гуруванн€

Ц STOP Ц значенн€ б≥та STOP = 1 дозвол€Ї перех≥д ћ до режиму зупину при надходженн≥ команди STOP; значенн€ STOP = 0 при виконуванн≥ команди STOP зд≥йснюЇ перезавантаженн€ процесора;

Ц COPD Ц використовуЇтьс€ дл€ керуванн€ роботою вартового таймера; значенн€ COPD = 1 заборон€Ї роботу цього модул€.

Ѕ≥ти рег≥стра CONFIG 2 також використовуютьс€ дл€ конф≥гуруванн€ ≥ мають таке призначенн€:

Ц IRQPUD Ц значенн€ цього б≥та IRQPUD = 1 забезпечуЇ п≥дключенн€ до входу IRQ # резистора, €кий Уп≥дт€гуЇФ потенц≥ал цього входу до потенц≥алу напруги живленн€;

Ц LVIT 1-0 Ц визначають значенн€ ном≥нальноњ напруги живленн€; значенн€ LVIT 1-0 = 00 або 01 в≥дпов≥даЇ значенню 5,0 ¬, а значенн€ LVIT 1-0 = 10 Ц 3,0 ¬.

ћодуль формуванн€ тактових сигнал≥в CGM 08 (Clock Generator Module) призначено дл€ формуванн€ посл≥довностей ≥мпульс≥в, потр≥бних дл€ роботи процесора та перифер≥йних модул≥в.

ћодуль CGM 08 вм≥щуЇ два генератори ≥мпульс≥в: CG, котрий формуЇ посл≥довн≥сть ≥мпульс≥в, частота €ких Fq визначаЇтьс€ зовн≥шн≥м кварцовим резонатором, ≥ генератор –G Ц частота сигналу котрого Fp = NЈFq визначаЇтьс€ роботою схеми фазового автоналаштовуванн€ частоти.

—игнал з виходу одного з генератор≥в п≥сл€ д≥ленн€ його на 2 надходить на модуль системноњ ≥нтеграц≥њ SIM 08, де виконуЇтьс€ формуванн€ тактових ≥мпульс≥в. ѕотреба використовуванн€ двох генератор≥в зумовлена вимогами зменшенн€ р≥вн€ високочастотних завад при робот≥ з високими частотами. ƒл€ пристроњв, €к≥ працюють з тактовою частотою понад 1 ћ√ц, рекомендовано використовувати генератор –G. —игнал на виход≥ такого генератора формуЇтьс€ внасл≥док множенн€ в≥дносно низькочастотного сигналу Fq ≥ роботи схеми фазового автоналаштовуванн€ частоти PLL (Phase-Locked Loop).

—хема PLL маЇ два режими роботи:

Ц режим захопленн€ частоти, за роботи в €кому п≥сл€ початкового завантаженн€ забезпечуЇтьс€ перех≥д до генеруванн€ сигналу в заданому частотному д≥апазон≥;

Ц режим утримуванн€. ¬ цьому режим≥ схема п≥дтримуЇ значенн€ вих≥дноњ частоти ≥ компенсуЇ можлив≥ в≥дхиленн€ њњ значенн€ в межах робочоњ смуги частот.

еруванн€ роботою модул€ CGM 08 зд≥йснюЇтьс€ за допомогою вм≥сту рег≥стр≥в керуванн€ PCTL (адреса $001 C), PBWC (адреса $001 D), PPG (адреса $001 E). ‘ормат цих рег≥стр≥в подано на рис. 13.16.

|

–исунок 13.16 Ц ‘ормат вм≥сту рег≥стр≥в керуванн€ модул€ CGM 08

–ег≥стр PCTL Ц рег≥стр керуванн€ модулем CGM 08 Ц вм≥щуЇ так≥ б≥ти:

Ц PLLIE Ц б≥т дозволу перериванн€ за запитом в≥д модул€ CGM 08. ѕри запуску ћ набираЇ значенн€ PLLIE = 0 (перериванн€ заборонен≥) ≥ може встановлюватис€ PLLIE = 1 лише за автоматичного керуванн€ генератором –G;

Ц PLLF Ц ознака запиту перериванн€ в≥д модул€ CGM 08. ЌабираЇ значенн€ PLLF = 1 за встановленого б≥та PLLIE ≥ автоматичного керуванн€;

Ц PLLON Ц б≥т дозволу роботи (за PLLON = 1) генератора –G. ѕри запуску ћ встановлюЇтьс€ PLLON = 0;

Ц BCS Ц б≥т вибору сигналу задл€ формуванн€ тактових частот. «наченн€ BCS = 0 передбачаЇ використовуванн€ генератора CG, а значенн€ BCS = 1 Ц генератора –G. ѕри включенн≥ ћ встановлюЇтьс€ значенн€ BCS = 0, при зм≥н≥ цього значенн€ Ц б≥т PLLON =1 ≥ стаЇ доступним лише дл€ читанн€;

|

|

|

–ег≥стр PBWC Ц рег≥стр керуванн€ формуванн€м частоти маЇ в своЇму склад≥ б≥ти:

Ц AUTO Ц б≥т керуванн€ режимом роботи генератора –G. «наченн€ б≥та AUTO = 1 встановлюЇтьс€ за автоматичного режиму та AUTO = 0 Ц за програмного;

Ц LOCK Ц б≥т точного встановлюванн€ частоти за автоматичного режиму роботи. «наченн€ LOCK = 1 встановлюЇтьс€, €кщо частота сигнал≥в, €к≥ формуютьс€, перебуваЇ в межах робочоњ смуги частот, ≥ LOCK = 0 Ц €кщо частота виходить за ц≥ меж≥;

Ц ACQ # Ц б≥т керуванн€ режимом роботи генератора. «а автоматичного керуванн€ значенн€ ACQ # =0 засв≥дчуЇ, що робота в≥дбуваЇтьс€ в режим≥ захопленн€ частоти, а значенн€ ACQ # = 1 Ц в режим≥ утримуванн€. «а програмного режиму значенн€ цього б≥та зумовлюють режим роботи: ACQ # = 0 переводить генератор до режиму захопленн€ частоти, а ACQ # = 1 Ц до режиму утримуванн€;

Ц XLD Ц б≥т контролю функц≥онуванн€ кварцового резонатора. ѕри встановленн≥ XLD = 1 через 4Ј N такт≥в зчитуЇтьс€ його значенн€; €кщо значенн€ XLD = 0, то резонатор Ї активний ≥ формуЇ точне значенн€ частоти; €кщо п≥сл€ зчитуванн€ значенн€ XLD = 1, то це в≥дпов≥даЇ неактивному станов≥ резонатора.

ѕри запуску вс≥ б≥ти цього рег≥стра набирають значенн€ 0.

–ег≥стр PPG Ц рег≥стр завдаванн€ коеф≥ц≥Їнт≥в, €к≥ визначають часов≥ характеристики сигнал≥в, вм≥щуЇ так≥ б≥ти:

Ц MUL 7Ц4 визначають значенн€ коеф≥ц≥Їнта множенн€ частоти N = 1...15;

Ц VRS 7Ц 4 задають коеф≥ц≥Їнт L = 1Е15, котрий визначаЇ значенн€ центральноњ частоти в робоч≥й смуз≥ частот системи PLL.

ћодуль системноњ ≥нтеграц≥њ SIM 08 виконуЇ початкове завантаженн€ ћ при включенн≥ живленн€ та перезавантаженн€ при надходженн≥ зовн≥шнього сигналу скиданн€ RST # або сигналу в≥д модул€ контролю функц≥онуванн€ —ќ– 08 або при формуванн≥ помилкового коду команди чи зверненн€ до не≥снуючоњ адреси. ќкр≥м того, цей модуль формуЇ тактов≥ сигнали дл€ процесора й ≥нших модул≥в, керуЇ передаванн€м команд ≥ даних внутр≥шньою шиною, обслуговуЇ запити перериванн€, зреал≥зовуЇ р≥зн≥ режими роботи ћ . ƒо складу модул€ вход€ть рег≥стри, вм≥ст котрих в≥дпов≥даЇ виконуванню перел≥чених функц≥й ≥ формат €ких подано на рис. 13.17.

|

–исунок 13.17 Ц ‘ормат вм≥сту рег≥стр≥в керуванн€ модулем

системноњ ≥нтеграц≥њ

–ег≥стр SRSR (адреса $ FE 01) Ц рег≥стр стану модул€ системноњ ≥нтеграц≥њ SIM 08. …ого вм≥ст дозвол€Ї встановити причину запуску ћ . ожен з його б≥т≥в маЇ в≥дпов≥дне призначенн€ ≥ встановлюЇтьс€ в 1 в раз≥, €кщо:

Ц POR Ц в≥дпов≥даЇ запуску ћ при включенн≥ живленн€;

Ц PIN Ц запуск ћ за сигналом скиданн€ RST #;

Ц COP Ц запуск за сигналом вартового таймера COP 08;

Ц ILOD Ц перезавантаженн€ при формуванн≥ помилкового коду команди;

Ц ILAD Ц перезавантаженн€ при зверненн≥ до не≥снуючоњ адреси;

Ц LVI Ц запуск за сигналом модул€ контролю живленн€ LVI 08.

¬м≥ст рег≥стра стану Ї доступний лише дл€ зчитуванн€, й п≥сл€ його виконанн€ вс≥ б≥ти встановлюютьс€ в 0. ѕри робот≥ програми ≥н≥ц≥ал≥зац≥њ вм≥ст цього рег≥стра сл≥д зчитати ≥ програма маЇ виконати анал≥з причин, що призвели до запуску чи перезавантаженн€.

–ег≥стр SBSR (адреса $ FE 00) Ц рег≥стр коригуванн€ адреси поверненн€ з п≥дпрограми обслуговуванн€ переривань. ƒо його складу входить лише один б≥т SBSW, до €кого Ї можливе зверненн€, решту б≥т≥в зарезервовано задл€ тестуванн€ в умовах виробника. Ѕ≥т SBSW встановлюЇтьс€, €кщо перериванн€ в контрольн≥й точц≥ в≥дбулось при виконуванн≥ команд WAIT або STOP. ¬ цьому раз≥ ћ виходить з режиму оч≥куванн€ чи зупину ≥ розпочинаЇ виконуванн€ п≥дпрограми обробки перериванн€, в котр≥й до стека завантажуЇтьс€ адреса команди, €ка сл≥дуЇ за командою WAIT чи STOP. “ому при поверненн≥ до основноњ програми, п≥сл€ завершенн€ виконуванн€ п≥дпрограми обробки перериванн€ (команда RTI), ћ не повернетьс€ до режиму оч≥куванн€ чи зупину. «адл€ запоб≥ганн€ зм≥ни режиму функц≥онуванн€ п≥дпрограма обробки перериванн€ перед виконуванн€м команди RTI маЇ перев≥рити значенн€ цього б≥та ≥, в раз≥ потреби, скоригувати значенн€ адреси поверненн€. «адл€ скиданн€ цього б≥та сл≥д записати 0 до в≥дпов≥дного б≥та рег≥стра SBSR.

|

|

|

–ег≥стр SBFCR (адреса $ FE 03) Ц рег≥стр дозволу зм≥нюванн€ стану перифер≥йних модул≥в. “акож маЇ лише один активний б≥т. ¬становленн€ б≥та BCFE = 1 дозвол€Ї при обробц≥ переривань в контрольн≥й точц≥ зм≥нювати стан вс≥х перифер≥йних модул≥в. ѕри значенн≥ б≥та BCFE = 0 стан перифер≥йних модул≥в в переб≥гу налагодженн€ програми буде збер≥гатис€.

ћодуль керуванн€ зовн≥шн≥м перериванн€м IRQ 08 обслуговуЇ зовн≥шн≥ запити перериванн€, €к≥ надход€ть на вх≥д IRQ #, в≥дпов≥дно до обраного режиму. ƒо складу модул€ входить рег≥стр керуванн€ зовн≥шн≥ми перериванн€ми ISCR (адреса $001 A), формат €кого подано на рис. 13.18.

|

–исунок 13.18 Ц ‘ормат вм≥сту рег≥стр≥в керуванн€

зовн≥шн≥ми перериванн€ми ISCR

ƒо цього рег≥стра вход€ть чотири б≥ти, €к≥ мають таке призначенн€:

Ц IRQF Ц ознака зовн≥шнього запиту перериванн€ (Ї доступний лише дл€ читанн€), значенн€ IRQF = 1 встановлюЇтьс€ при надходженн≥ запиту перериванн€ на вх≥д IRQ #;

Ц ACK Ц б≥т п≥дтвердженн€ прийманн€ запиту перериванн€ (Ї доступний лише дл€ запису), при запису до нього 1 в≥дбуваЇтьс€ скиданн€ б≥та IRQF;

Ц IMASK Ц б≥т маски зовн≥шнього перериванн€. ѕри встановленн≥ IMASK = 1 надходженн€ зовн≥шнього запиту не призводить до перериванн€ виконуваноњ програми;

Ц MODE Ц б≥т визначенн€ виду сигналу перериванн€; встановленн€ значенн€ MODE = 1 спричинюЇ перериванн€ при надходженн≥ на вх≥д IRQ # низького р≥вн€ сигналу.

ћодуль перериванн€ в контрольн≥й точц≥ BREAK 08 використовуЇтьс€ при налагодженн≥ програмного забезпеченн€ дл€ реал≥зац≥њ режиму зупину у контрольн≥й точц≥.

ѕерериванн€ такого типу в≥дбуваЇтьс€, €кщо при налагодженн≥ програмного забезпеченн€ сформована процесором адреса зб≥гаЇтьс€ з 16-розр€дною адресою контрольноњ точки, записаноњ в рег≥страх BRKH-BRKL модул€ BREAK 08. ѕри цьому, зам≥сть адреси наступноњ команди, формуЇтьс€ адреса програмного перериванн€ SWI, при обслуговуванн≥ €кого зупин€Їтьс€ робота таймерних модул≥в та вартового таймера. ¬иконанн€ програмного перериванн€ SWI Ї немаскованим, тому в≥дбуваЇтьс€ незалежно в≥д значенн€ б≥та ≤ рег≥стра прапорц≥в.

ƒл€ керуванн€ модулем використовуЇтьс€ рег≥стр BRKSR, €кий входить до складу модул€. ‘ормат рег≥стра подано на рис. 13.19.

|

–исунок 13.19 Ц ‘ормат вм≥сту рег≥стра BRKSR модул€ BREAK 08

ƒо складу цього рег≥стра вход€ть два активних б≥ти Ц BRKE та BRKA, котрим притаманн≥ так≥ особливост≥ роботи:

Ц BRKE Ц ознака дозволу перериванн€ в контрольн≥й точц≥; значенн€ BRKE = 1 дозвол€Ї перериванн€, а BRKE = 0 Ц заборон€Ї;

Ц BRKA Ц ознака зб≥гу адреси поточноњ команди з вм≥стом рег≥стр≥в BRKH-BRKL $, встановленн€ значенн€ BRKA = 1 призводить до перериванн€ в контрольн≥й точц≥.

ѕри функц≥онуванн≥ модул€ також використовуютьс€ значенн€ б≥т≥в BCFE та SBSW в модул≥ системноњ ≥нтеграц≥њ.

ћодуль контролю напруги живленн€ LVI 08 використовуЇтьс€ дл€ контролю напруги живленн€. якщо при робот≥ ћ напруга живленн€ знижуЇтьс€ понад задане значенн€, то модуль контролю напруги живленн€ LVI 08 переводить ћ до початкового стану, котрий збер≥гаЇтьс€ до встановленн€ нормального р≥вн€ напруги.

” б≥льшост≥ сер≥й с≥мейства до складу модул€ LVI 08 входить рег≥стр стану LVISR, вм≥ст €кого можна лише зчитувати. ‘ормат рег≥стра подано на рис. 13.20.

|

–исунок 13.20 Ц ‘ормат вм≥сту рег≥стра стану LVISR

Ѕ≥т LVIOUT цього рег≥стра набираЇ значенн€ LVIOUT = 1, €кщо напруга живленн€ зменшуЇтьс€ понад р≥вень 4,0...4,3 ¬ за ном≥нальноњ напруги живленн€ 5 ¬ ≥ до р≥вн€ 2,4...2,7 ¬ Ц за ном≥нального значенн€ 3 ¬.

ћодуль продовжуЇ роботу в режим≥ оч≥куванн€ ≥ в≥дключаЇтьс€ в режим≥ зупину.

ћодуль контролю функц≥онуванн€ —ќ– 08 контролюЇ виконуванн€ програми за допомогою вартового таймера.

–обота вартового таймера пол€гаЇ в тому, що до рег≥стра керуванн€ COPCTL (адреса $ FFFF) пер≥одично записуЇтьс€ дов≥льне число. «апис повинен в≥дбуватис€ не р≥дше одного разу за час Tw. ÷ей час визначаЇтьс€ значенн€м б≥та COPRS у рег≥стр≥ конф≥гуруванн€ CONFIG 1 ≥ становить:

|

|

|

Tw = 262128Ј Tq Ц за значенн€ б≥та COPRS = 0;

Tw = 8176Ј Tq Ц за значенн€ б≥та COPRS = 1.

якщо такий запис не буде виконуватис€, то вартовий таймер виконаЇ перезапуск ћ . “акий запис зручно виконувати командою

STA $FFFF; запис вм≥сту акумул€тора до рег≥стра з адресою $ FFFF

÷ю команду сл≥д долучати до тексту програми задл€ пер≥одичного виконуванн€.

¬артовий таймер продовжуЇ свою роботу в режим≥ оч≥куванн€, ≥ тому, залежно в≥д його поточного стану перед надходженн€м команди WAIT, може статис€ його незаплановане спрацьовуванн€.

¬ режим≥ зупину вартовий таймер припин€Ї роботу, але збер≥гаЇ значенн€ поточного стану, тому маЇ сенс перед виконуванн€м команди STOP виконувати скиданн€ цього модул€.

ƒо складу посл≥довних ≥нтерфейсних модул≥в вход€ть:

ћодуль ≥нтерфейса з посл≥довною шиною USB 08 забезпечуЇ обм≥н даними шиною USB, €ка використовуЇтьс€ в обчислювальн≥й техн≥ц≥.

ћодуль посл≥довного ≥нтерфейса msCAN 08 забезпечуЇ обм≥н даними в стандартному та розширеному форматах в≥дпов≥дно до специф≥кац≥й CAN 2.0 ј та CAN 2.0 ¬.

ћодуль синхронного перифер≥йного ≥нтерфейса SPI 08 забезпечуЇ синхронний обм≥н даними з≥ швидк≥стю до 4 ћб≥т/с. ÷ей модуль використовуЇтьс€ дл€ орган≥зац≥њ звТ€зку пом≥ж ћ та ≥ншими пристро€ми на незначн≥й в≥дстан≥.

ћодуль асинхронного ≥нтерфейса звТ€зку SCI 08 зреал≥зовуЇ стандартний асинхронний протокол обм≥ну 8- або 9-б≥тними даними з одним стартовим та одним стоповим б≥тами з≥ швидк≥стю до 130 кб≥т/с.

Ѕлок паралельних порт≥в вм≥щуЇ в≥д 2-х до 8-ми паралельних 8-розр€дних порт≥в (–ј, –¬,..., –G, PH). ¬иводи де€ких порт≥в можуть використовуватис€ задл€ виконанн€ альтернативних функц≥й: орган≥зац≥њ посл≥довного обм≥ну даними, обм≥ну сигналами таймерних модул≥в, введенн€ аналогових сигнал≥в тощо.

ƒо блока перифер≥йних модул≥в дл€ р≥зних сер≥й можуть входити:

“аймерний модуль “≤ћ 08 призначений дл€ формуванн€ часових ≥нтервал≥в, потр≥бних дл€ керуванн€ ћ та ≥ншими пристро€ми, €к≥ вход€ть до складу системи, в ц≥лому. ¬≥н побудований на баз≥ 16-розр€дного л≥чильника, €кий, в р≥зних модел€х, може мати 2, 4 чи 6 канал≥в, €к≥ можуть працювати в режим≥ захопленн€ чи зб≥гу з наперед окресленим значенн€м часу спрацьовуванн€. анали мають входи сигнал≥в захопленн€ ≤— ≥ в≥дпов≥дн≥ рег≥стри захопленн€ та пор≥вн€нн€, а також виходи сигнал≥в зб≥ганн€. Ћ≥чильник може працювати з вх≥дними сигналами, €к≥ надход€ть в≥д тактового генератора модул€ CGM 08 Ц режим таймера (з можлив≥стю його зупину та запуску) або з сигналами в≥д зовн≥шн≥х пристроњв Ц режим л≥чби зовн≥шн≥х под≥й. ќкр≥м того, пари канал≥в таймера можуть використовуватис€ задл€ формуванн€ сигнал≥в широтно-≥мпульсноњ модул€ц≥њ (Ў≤ћ). Ѕ≥льш≥сть моделей с≥мейства вм≥щуЇ два незалежних таймерних модул€.

ћодуль базового таймера “¬ћ 08 забезпечуЇ пер≥одичне формуванн€ сигнал≥в запиту перериванн€ при переповненн≥ базового л≥чильника. ¬≥н вм≥щуЇ 15-розр€дний л≥чильник, на вх≥д €кого надход€ть сигнали кварцового резонатора. ¬ режим≥ оч≥куванн€ цей таймер продовжуЇ функц≥онувати ≥ забезпечуЇ перех≥д ћ до робочого режиму. ¬ режим≥ зупину таймер може продовжувати працювати, €кщо дозволено роботу генератора CGM 08 ≥ формуванн€ сигналу запиту перериванн€.

ћодуль таймера пер≥одичних переривань –≤“ 08 використовуЇтьс€ дл€ пер≥одичного формуванн€ сигнал≥в запиту перериванн€. ћодуль побудовано на баз≥ 16-розр€дного л≥чильника ≥ забезпечуЇ формуванн€ сигнал≥в запиту переривань в широкому д≥апазон≥ значень пер≥оду цих сигнал≥в. ¬ режим≥ оч≥куванн€ цей таймер продовжуЇ функц≥онувати ≥ забезпечуЇ перех≥д ћ до робочого режиму при переповненн≥ л≥чильника, а в режим≥ зупину цей модуль вимикаЇтьс€.

ћодуль широтно-≥мпульсного модул€тора PWM 08 вм≥щуЇ 12-розр€дний 6-канальний Ў≤ћ модул€тор.

ћодуль аналого-цифрового перетворенн€ ADC 08 використовуЇтьс€ дл€ аналого-цифрового перетворенн€ вх≥дних аналогових сигнал≥в. ¬ б≥льшост≥ моделей зреал≥зовано 8-розр€дне перетворенн€ аналогового сигналу, а в де€ких модел€х Ц 10-розр€дне. ≥льк≥сть аналогових вход≥в в р≥зних модел€х може становити в≥д 4 до 15.

ћодуль пр€мого доступу до памТ€т≥ DMA 08 забезпечуЇ роботу з≥ швидкод≥ючими зовн≥шн≥ми пристро€ми.

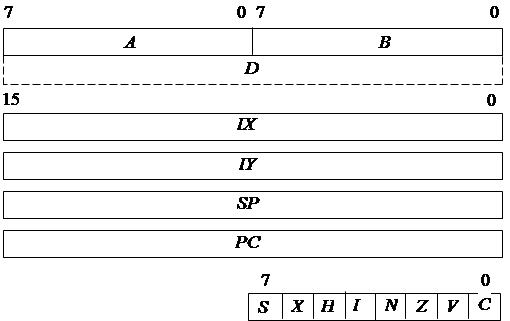

ѕроцесорний модуль CPU 08 Ї модиф≥кованим вар≥антом процесора CPU 05. ¬≥н маЇ розширений наб≥р команд та способ≥в адресуванн€ ≥ програмно ц≥лковито Ї сум≥сний з CPU 05. –ег≥строву модель процесора CPU 08 подано на рис. 13.21.

ƒо рег≥стровоњ модел≥ вход€ть:

Ц 8-розр€дний акумул€тор ј;

Ц 16-розр€дний ≥ндексний рег≥стр Ќ:—. ƒл€ забезпеченн€ програмноњ сум≥сност≥ з CPU 05 ≥ндексний рег≥стр складаЇтьс€ з двох частин, розд≥льне використовуванн€ €ких дозвол€Ї забезпечувати функц≥онуванн€ програм ћ с≥мейства ћ68 Ќ— 05/705;

Ц 16-розр€дний програмний л≥чильник –—;

Ц 16-розр€дний вказ≥вник стека SP;

Ц 8-розр€дний рег≥стр прапорц≥в CCR. ¬м≥щуЇ так≥ ознаки, €к≥ формуютьс€ у процесор≥ CPU 05. ƒо них додано ознаку V Ц ознаку переповнюванн€ при обробц≥ чисел з≥ знаком. ќзнака встановлюЇтьс€ V = 1, €кщо результат маЇ к≥льк≥сть розр€д≥в б≥льшу, н≥ж можливо розм≥стити њх в розр€дн≥й с≥тц≥ ћ .

Ц

|

–исунок 13.21 Ц –ег≥строва модель процесора CPU 08

ќбс€г адресного простору, €кий може адресувати ћ с≥мейства ћ 68 Ќ— 08/908, становить 64 кбайти. ƒе€к≥ ћ с≥мейства мають менший обс€г адресного простору, тому в њхньому адресному простор≥ Ї област≥ адрес, €к≥ не в≥дпов≥дають певним пристро€м. ѕри зверненн≥ до таких адрес зреал≥зовуЇтьс€ перериванн€, €ке в≥дпов≥даЇ на€вност≥ помилки у програм≥ Ц зверненн≥ до не≥снуючоњ ком≥рки. ¬насл≥док цього в≥дбуваЇтьс€ перезавантаженн€ ћ , до програмного л≥чильника –— автоматично завантажуЇтьс€ адреса першоњ команди обробки перериванн€ з двох останн≥х ком≥рок адресного простору ($ FFFE Ц $ FFFF).

ѕри перезавантаженн≥ ћ у вказ≥вник стека автоматично записуЇтьс€ адреса вершини стека ($00 FF), €ка забезпечуЇ використовуванн€ в €кост≥ стека ком≥рок памТ€т≥ ќ«ѕ та рег≥стр≥в, адреси €ких м≥ст€тьс€ у д≥апазон≥ ($0000...$00 FF). ѕри робот≥ користувач маЇ змогу зам≥нити цю адресу вершини стека на ≥ншу в межах адресного простору ќ«ѕ.

—≥мейство ћ—68Ќ—11/711

Ќайб≥льш досконалим с≥мейством 8-розр€дних ћ Ї ћ— 68 Ќ— 11/711. —ьогодн≥ випускаЇтьс€ близько 20 р≥зних моделей ћ цього с≥мейства. ƒо складу структурноњ схеми ћ вход€ть модул≥, €к≥ за функц≥ональним призначенн€м Ї аналог≥чн≥ до описаних вище. –≥зн≥ модел≥ с≥мейства мають однакове процесорне €дро ≥ в≥др≥знюютьс€ обс€гом та типом внутр≥шнього запамТ€товувального пристрою, складом перифер≥йного обладнанн€ й де€кими ≥ншими характеристиками. ќсоблив≥стю цього с≥мейства Ї можлив≥сть зб≥льшенн€ зовн≥шньоњ памТ€т≥ обс€гом в≥д 64 кбайт до 4 ћбайт.

ћ с≥мейства ћ— 68 Ќ— 11/711 у своЇму склад≥ мають внутр≥шню памТ€ть програм Ц ѕ«ѕ Ц у склад≥ ћ—68Ќ—11 або –ѕ«ѕ Ц у ћ— 68 Ќ— 711, обс€гом до 32 кбайт; ќ«ѕ даних обс€гом в≥д 192 до 1024 байт. ƒе€к≥ модел≥ мають внутр≥шн≥й –ѕ«ѕ-≈— обс€гом до 540 байт.

ѕри використовуванн≥ ћ цього с≥мейства можна зорган≥зовувати роботу в двох режимах Ц автономному ≥ розширеному. ѕри робот≥ в автономному режим≥ використовуЇтьс€ лише внутр≥шн€ памТ€ть ћ , а в розширеному дозвол€Їтьс€ п≥дключенн€ зовн≥шньоњ памТ€т≥, робота з €кою в≥дбуваЇтьс€ за допомогою мультиплексованоњ чи окремоњ зовн≥шньоњ шини адреси/даних. ¬ де€ких модел€х передбачено розширенн€ зовн≥шньоњ памТ€т≥ ≥ можлив≥сть зорган≥зовувати банки памТ€т≥.

¬с≥ модел≥ мають в своЇму склад≥ 16-розр€дний таймер, котрий може мати 3-4 входи сигнал≥в захопленн€ частоти (≤—) ≥ 4-5 вход≥в сигнал≥в зб≥гу частот. ÷ей таймер також використовуЇтьс€ задл€ формуванн€ сигнал≥в пер≥одичних переривань. ќкр≥м таймера, до складу ћ входить 8-розр€дний л≥чильник зовн≥шн≥х под≥й.

ƒе€к≥ ћ вм≥щують 8-розр€дн≥ широтно-≥мпульсн≥ модул€тори, €к≥ мають 4 входи, що вони можуть працювати в режим≥ 16-розр€дних широтно-≥мпульсних модул€тор≥в з двома входами.

ћ с≥мейства вм≥щують в≥д 4-х до 10-ми паралельних 8-розр€дних паралельних порт≥в, асинхронний ≥ синхронний посл≥довн≥ порти SCI (SCI +) ≥ SPI.

ƒо складу б≥льшост≥ моделей входить 8-розр€дний ј÷ѕ з 8-мома аналоговими входами.

ѕроцесорне €дро с≥мейства складаЇтьс€ з процесора 68 Ќ— 11, рег≥строву модель котрого зображено на рис. 13.22.

|

–исунок 13.22 Ц –ег≥строва модель процесора 68 Ќ— 11

ƒо складу рег≥стровоњ модел≥ процесора 68 Ќ— 11 вход€ть:

Ц два 8-розр€дн≥ акумул€тори ј ≥ ¬, котр≥ при виконуванн≥ де€ких команд обТЇднуютьс€ у 16-розр€дний рег≥стр D;

Ц два 16-розр€дн≥ ≥ндексн≥ рег≥стри IX ≥ IY, котр≥ використовуютьс€ дл€ формуванн€ адреси при ≥ндексному адресуванн≥ операнд≥в;

Ц 16-розр€дний вказ≥вник стека SP;

Ц 16-розр€дний програмний л≥чильник PC;

Ц 8-розр€дний рег≥стр прапорц≥в CCR, котрий вм≥щуЇ ознаки H, I, N, Z, V ≥ C, призначенн€ й використовуванн€ котрих Ї аналог≥чн≥ до 8-розр€дних ћ . ƒо складу цього рег≥стра до CPU 12 додатково введено ознаку ’, встановленн€ €коњ ’ = 1 заборон€Ї обслуговуванн€ зовн≥шнього запиту перериванн€ по входу ’IRQ #, ≥ ознаку S, €ка при встановленн≥ S = 1 заборон€Ї переключенн€ ћ до режиму зупину при надходженн≥ команди STOP.

ѕроцесор виконуЇ обробку 8- ≥ 16-розр€дних операнд≥в ≥ зреал≥зовуЇ 108 команд. ѕри робот≥ з операндами в≥н використовуЇ так≥ способи адресуванн€ €к с≥мейство 68 Ќ— 05/705; б≥льш≥сть команд, виконуваних ћ , Ї аналог≥чн≥ до команд с≥мейства 68 Ќ— 05/705. ¬≥дм≥нност≥ зумовлено на€вн≥стю двох акумул€тор≥в. ƒодатково до системи команд введено команди д≥ленн€ ≥ розширено можливост≥ команд б≥тових операц≥й.

ћ с≥мейства можуть працювати в чотирьох режимах, €к≥ зумовлюютьс€ зовн≥шн≥ми сигналами MODB ≥ MODA, €к≥ приймаютьс€ при початковому завантаженн≥ ћ , а також вм≥стом рег≥стра HPRIO. –ежими функц≥онуванн€ визначаютьс€ в≥дпов≥дно до табл. 13.2.

“аблиц€ 13.2 Ц –ежими функц≥онуванн€ ћ с≥мейства ћ— 68 Ќ— 11/711

| –ежим | «овн≥шн≥ сигнали | ¬м≥ст рег≥стра HPRIO | |||||

| MODB | MODA | RBOOT | SMOD | MDA | IRV | PSEL 3-0 | |

| –обочий автономний | |||||||

| –обочий розширений | |||||||

| —пец≥альний Ц завантаженн€ | |||||||

| —пец≥альний Ц тестуванн€ |

јвтономний (однокристальний) робочий режим передбачаЇ функц≥онуванн€ ћ з використанн€м лише внутр≥шньоњ памТ€т≥, а в розширеному режим≥ передбачено п≥дмиканн€ через порти ¬ та — зовн≥шнього запамТ€товувального пристрою. ѕри робот≥ у спец≥альному режим≥ в≥дбуваЇтьс€ завантажуванн€ внутр≥шнього запамТ€товувального пристрою через посл≥довний порт SPI п≥д керуванн€м спец≥альноњ програми-мон≥тора, €ку розм≥щено у службовому ѕ«ѕ, або тестуванн€ ћ заводом-виробником.

–ежим функц≥онуванн€ ≥ конф≥гурац≥€ ћ визначаютьс€ вм≥стом службових рег≥стр≥в HPRIO, CONFIG, OPTION та INIT, котр≥ вход€ть до складу процесора. ‘ормат вм≥сту цих рег≥стр≥в подано на рис. 13.23. ƒл€ р≥зних сер≥й ћ адреси цих рег≥стр≥в та њхн≥й склад не зб≥гаютьс€, але призначенн€ б≥т≥в Ї однаковим.

|

–исунок 13.23 Ц ‘ормат вм≥сту рег≥стр≥в конф≥гуруванн€

ћ ћ— 68 Ќ— 11/711

ƒо складу рег≥стра HPRIO вход€ть б≥ти:

Ц RBOOT Ц б≥т дозволу зверненн€ до програми-мон≥тора, €ка виконуЇ завантажуванн€ ќ«ѕ ≥з зовн≥шнього джерела. « табл. 13.2 видно, що при робот≥ у спец≥альному режим≥ завантаженн€ значенн€ цього б≥та встановлюЇтьс€ RBOOT = 1;

Ц SMOD разом з б≥том MDA, в≥дпов≥дно до табл. 13.2, визначають режим функц≥онуванн€ ћ п≥сл€ початкового завантаженн€;

Ц IRVNE Ц в розширеному режим≥ значенн€ IRVNE = 1 дозвол€Ї видаванн€ даних на виводи порту — при зверненн≥ до внутр≥шньоњ памТ€т≥; у автономному режим≥ та спец≥альних режимах значенн€ IRVNE = 1 заборон€Ї виведенн€ тактових сигнал≥в на вив≥д ≈ (задл€ зменшенн€ р≥вн€ завад в систем≥);

Ц PSEL 3-0 Ц визначають пр≥оритет обслуговуванн€ маскованих запит≥в переривань.

ѕри початковому завантажуванн≥ б≥ти RBOOT, SMOD, MDA, IRVNE та PSEL 3-0 набирають значень в≥дпов≥дно до табл. 13.2. ѕ≥сл€ запуску значенн€ б≥та RBOOT ≥ б≥т≥в SMOD та MDA у спец≥альному режим≥ можна зм≥нювати. «наченн€ б≥та IRVNE можна одноразово зм≥нювати у будь-€кому режим≥. ƒо б≥т≥в PSEL 3-0 можливе зверненн€ в робочому режим≥. ƒо б≥та MDA також Ї можливе одноразове зверненн€ в робочому режим≥.

–ег≥стр OPTION вм≥щуЇ б≥ти, €к≥ визначають функц≥онуванн€ окремих модул≥в ћ :

Ц ADPU Ц значенн€ ADPU =1 вмикаЇ живленн€ модул€ ј÷ѕ;

Ц CSEL Ц значенн€ б≥та CSEL = 1 дозвол€Ї використовуванн€ внутр≥шнього RC -генератора задл€ формуванн€ синхросигнал≥в забезпеченн€ програмуванн€ –ѕ«ѕ-≈— та роботу ј÷ѕ; значенн€ CSEL = 0 в≥дпов≥даЇ використовуванню задл€ синхрон≥зац≥њ тактових ≥мпульс≥в ћ ;

Ц IRQE Ц визначаЇ вид зовн≥шнього сигналу запиту переривань IRQ #; при значенн≥ IRQE = 0 за активний вважаЇтьс€ низький р≥вень вх≥дного сигналу IRQ#; IRQE = 1 визначаЇ, що запит перериванн€ зд≥йснюЇтьс€ в≥д зр≥зу сигналу IRQ #;

Ц DLU Ц значенн€ DLU = 1 визначаЇ затримку початку функц≥онуванн€ п≥сл€ виходу ћ з режиму зупину на час близько 4000 такт≥в, при значенн≥ б≥та DLU = 0 затримка становить 4 такти;

Ц CME Ц дозвол€Ї функц≥онуванн€, за CME = 1, схеми контролю тактовоњ частоти;

Ц FCME Ц дозвол€Ї функц≥онуванн€, за FCME = 1, схеми контролю тактовоњ частоти, за будь-€кого значенн€ б≥та CME; за значенн€ FCME = 0 функц≥онуванн€ блока контролю тактовоњ частоти визначаЇтьс€ вм≥стом б≥та CME;

Ц CR 1-0 Ц б≥ти визначають значенн€ Kw Ц коеф≥ц≥Їнта задл€ задаванн€ можливих ≥нтервал≥в часу контролю дл€ вартового таймера. ¬изначаЇтьс€ в≥дпов≥дно до табл. 13.1.

ѕри початковому завантаженн≥ вс≥ б≥ти рег≥стра OPTION скидаютьс€ ≥ набирають значенн€ 0, окр≥м б≥та DLU, €кий встановлюЇтьс€ в 1. «а подальшоњ роботи у спец≥альних режимах вс≥ б≥ти Ї доступними ≥ в них може проводитис€ запис ≥ в≥дбуватис€ зчитуванн€ њхнього вм≥сту. ¬ робочих режимах значенн€ б≥т≥в ADPU, CSEL, CME може зм≥нюватис€, а значенн€ ≥нших б≥т≥в можна одноразово зм≥нювати упродовж 64 такт≥в п≥сл€ запуску ћ .

¬м≥ст рег≥стра INIT визначаЇ розм≥щенн€ в адресному простор≥ ќ«ѕ даних ≥ внутр≥шн≥х рег≥стр≥в перифер≥йних модул≥в. «а початкового завантаженн€ б≥ти RAM 3-0, котр≥ визначають адресу ќ«ѕ, набирають значенн€ 0000, що забезпечуЇ зверненн€ до стор≥нки з адресою 0. Ѕ≥ти REG 3-0 набирають значенн€ 0001 ≥ адресують стор≥нку з адресою 1, в €к≥й розм≥щено адреси вс≥х внутр≥шн≥х рег≥стр≥в перифер≥йних модул≥в. «а роботи в одному з робочих режим≥в дозвол€Їтьс€ одноразовий запис до цього рег≥стра упродовж 64-х такт≥в п≥сл€ запуску.

–ег≥стр CONFIG визначаЇ конф≥гурац≥ю ћ , ≥ його б≥ти мають таке призначенн€:

Ц NOSEC Ц захист внутр≥шн≥х ќ«ѕ та –ѕ«ѕ-≈— в≥д зовн≥шнього зчитуванн€; значенн€ б≥та NOSEC = 0 вказуЇ на на€вн≥сть такого захисту (встановлюЇтьс€ виробником, за замовленн€м користувача), значенн€ б≥та NOSEC = 1 визначаЇ в≥дсутн≥сть такого захисту;

Ц NOCOP Ц керуванн€ роботою модул€ контролю функц≥онуванн€; значенн€ NOCOP = 0 дозвол€Ї функц≥онуванн€ цього модул€;

Ц ROMON Ц керуванн€ роботою внутр≥шнього ѕ«ѕ; значенн€ б≥та ROMON = 1 дозвол€Ї функц≥онуванн€ ѕ«ѕ, а значенн€ ROMON = 0 спричинюЇ зверненн€ до зовн≥шньоњ памТ€т≥;

Ц EEON Ц керуванн€ роботою внутр≥шнього –ѕ«ѕ-≈—; значенн€ б≥та EEON = 1 дозвол€Ї функц≥онуванн€ –ѕ«ѕ-≈—, а значенн€ EEON = 0 спричинюЇ зверненн€ до ќ«ѕ або до зовн≥шньоњ памТ€т≥.

–ег≥стр CONFIG програмуЇтьс€ користувачем €к –ѕ«ѕ-≈—, ≥ тому в≥н збер≥гаЇ значенн€ власних б≥т≥в до перепрограмуванн€.

13.1.2 16-розр€дн≥ м≥кроконтролери

—≥мейство 68Ќ—12/912

16-розр€дн≥ ћ с≥мейства 68 Ќ— 12/912 Ї основним промисловим стандартом 16-розр€дних ћ ф≥рми Motorola. « 2002 року ф≥рма розпочала випуск нового покол≥нн€ цього с≥мейства Ц 68 Ќ—S 12/912. ÷≥ ћ схарактеризовуютьс€ значним п≥двищенн€м продуктивност≥ (тактову частоту зб≥льшено до 40 ћ√ц) ≥ зб≥льшенн€м обс€гу внутр≥шньоњ Flash -памТ€т≥ (до 512 кбайт).

ƒо складу с≥мейства 68 Ќ—S 12/912 входить низка ћ , €к≥ в≥др≥знюютьс€ один в≥д одного типом та обс€гом внутр≥шньоњ памТ€т≥, к≥льк≥стю та типами перифер≥йних пристроњв, €к≥ розм≥щено у м≥кросхем≥.

¬ системах та пристро€х ц≥ ћ можуть працювати в автономному та розширеному режимах. ѕри робот≥ в автономному режим≥ (Single Chip) ћ використовуЇ лише внутр≥шню памТ€ть задл€ збер≥ганн€ програм ≥ даних, а в розширеному режим≥ передбачено п≥дключенн€ зовн≥шнього запамТ€товувального пристрою ≥ орган≥зац≥€ 8- або 16-розр€дноњ системноњ шини (в б≥льшост≥ моделей Ц мультиплексованоњ).

ћ с≥мейства 68 Ќ— 12 мають модульну структуру, €ка складаЇтьс€ з низки стандартних функц≥ональних блок≥в, взаЇмод≥€ пом≥ж €кими зреал≥зовуЇтьс€ по стандартизован≥й м≥жмодульн≥й шин≥. «агалом до складу ћ вход€ть: 16-розр€дний процесор CPU 12, внутр≥шн≥й оперативний запамТ€товувальний пристр≥й (ќ«ѕ даних), –ѕ«ѕ-≈—, Flash-памТ€ть або ѕ«ѕ, програмований маскою, модуль ≥нтеграц≥њ LIM та наб≥р перифер≥йних модул≥в. ѕроцесор CPU 12 взаЇмод≥Ї з цими модул€ми через њхн≥ рег≥стри, адреси котрих п≥сл€ запуску розм≥щуютьс€ у перших 512-ти ком≥рках адресного простору.

ћодуль ≥нтеграц≥њ LIM використовуЇтьс€ дл€ реал≥зац≥њ службових функц≥й, до котрих належать:

Ц генеруванн€ потр≥бних тактових сигнал≥в;

Ц початковий запуск ≥ конф≥гуруванн€ ћ ;

Ц реал≥зац≥€ переривань при надходженн≥ запит≥в в≥д зовн≥шн≥х пристроњв, внутр≥шн≥х переривань процесора, пер≥одичних переривань, а також зовн≥шн≥х запит≥в;

Ц реал≥зац≥€ ≥нтерфейса ≥з зовн≥шньою системною шиною у розширеному режим≥;

Ц контроль функц≥онуванн€ ћ за допомогою вартового таймера ≥ мон≥торингу тактових ≥мпульс≥в;

Ц налагодженн€ програм за допомогою режиму BDM (Back-ground Debug Mode) ≥ апаратного встановлюванн€ контрольних точок.

ƒо складу блока перифер≥йних модул≥в можуть входити:

Ц 8 Ц 12 паралельних порт≥в задл€ обм≥ну 8-розр€дними даними. ¬иводи б≥льшост≥ порт≥в можуть використовуватис€ дл€ виконуванн€ ≥нших функц≥й, наприклад, дл€ передаванн€ адреси та даних при робот≥ ≥з зовн≥шньою памТ€ттю, орган≥зац≥њ посл≥довних порт≥в SCI, SPI таймера, ј÷ѕ, контролер≥в шин тощо;

Ц таймерн≥ модул≥ “≤ћ та ≈—“, котр≥ побудовано на баз≥ 16-розр€дного л≥чильника, а також 16-розр€дний л≥чильник под≥й, €кий входить до складу де€ких моделей;

Ц модул≥ аналого-цифрового перетворюванн€ вход€ть до складу вс≥х ћ с≥мейства, мають 8 вход≥в дл€ прийманн€ аналогових сигнал≥в. ¬ б≥льшост≥ моделей зреал≥зовано 10-б≥тове перетворюванн€ аналогового сигналу;

Ц модуль формуванн€ сигнал≥в широтно-≥мпульсноњ модул€ц≥њ маЇ чотири вих≥дних канали, значенн€ парност≥ дл€ кожного з котрих можуть визначатис€ окремо;

Ц модул≥ посл≥довного асинхронного та синхронного ≥нтерфейс≥в SCI та SPI, котр≥ працюють аналог≥чно до в≥дпов≥дних пристроњв 8-розр€дних ћ ;

Ц спец≥ал≥зован≥ ≥нтерфейсн≥ модул≥ BDLC, CAN, I 2 C вход€ть до складу р≥зних моделей ≥ зреал≥зовують обм≥н даними в≥дпов≥дно до мережних протокол≥в J 1850, CAN 2.0 A / B, I 2 C.

16-розр€дний процесор CPU 12, €кий входить до складу ћ с≥мейства дозвол€Ї виконувати обробку 8- ≥ 16-розр€дних операнд≥в. –ег≥строва модель цього процесора Ї аналог≥чна до процесора CPU 11, €ку подано на рис. 13.22.

ѕрограмний код CPU 12 Ї сум≥щеним з кодом 68 Ќ— 11 на р≥вн≥ вх≥дного тексту.

ѕроцесор CPU 12 виконуЇ вс≥ способи адресуванн€, €к≥ використовуютьс€ с≥мейством 68 Ќ— 11/711 ≥, окр≥м того, може додатково зреал≥зовувати ще 7 додаткових вар≥ант≥в ≥ндексного адресуванн€.

—истема команд процесора CPU 12 вм≥щуЇ 208 команд над операндами, €к≥ розм≥щуютьс€ у ком≥рках памТ€т≥ та рег≥страх, ≥ Ї розширеним набором команд с≥мейства 68 Ќ— 11/711.

—≥мейство 68Ќ—16/916

ћ с≥мейства 68 Ќ— 16/916 Ї подальшим розвиненн€м тенденц≥й, €к≥ було зреал≥зовано в 8- та 16-розр€дних контролерах. —≥мейство вм≥щуЇ низку моделей, котр≥ в≥др≥знюютьс€ типом та обс€гом внутр≥шньоњ памТ€т≥ та номенклатурою перифер≥йного обладнанн€, €к≥ вход€ть до складу ћ . ” пор≥вн€нн≥ з с≥мейством 68 Ќ— 11/711 ц≥ ћ схарактеризовуютьс€ такими перевагами:

Ц розширений наб≥р команд та способ≥в адресуванн€;

Ц введенн€ спец≥альних рег≥стр≥в та команд задл€ зреал≥зовуванн€ операц≥й цифровоњ обробки сигнал≥в;

Ц п≥двищена продуктивн≥сть за рахунок зб≥льшенн€ тактовоњ частоти до 25 ћ√ц;

Ц зб≥льшенн€ до одного ћбайта обс€гу адресного простору (через те що Ї дозволено розд≥льне зверненн€ до памТ€т≥ команд та памТ€т≥ даних, то сумарний обс€г памТ€т≥ може с€гати 2 ћбайти);

Ц використовуванн€ перифер≥йних пристроњв з розширеними функц≥ональними можливост€ми;

Ц на€вн≥сть вбудованих засоб≥в налагодженн€ програмного забезпеченн€.

ћ с≥мейства 68 Ќ— 16/916 мають модульну структуру ≥ будуютьс€ з≥ стандартних функц≥ональних модул≥в, до складу €ких вход€ть: процесор CPU 16, модуль внутр≥шньоњ памТ€т≥, модуль системноњ ≥нтеграц≥њ SIM або SCIM, модуль посл≥довного ≥нтерфейсу QSM, багатоканальний комун≥кац≥йний ≥нтерфейс MCCI, процесор часових ≥нтервал≥в TPU, таймерн≥ модул≥ GPT або CTM, аналого-цифровий перетворювач ADC. ƒе€к≥ з цих модул≥в використовуютьс€ також у 32-розр€дних ћ ф≥рми. ”загальнена структурна схема ћ с≥мейства 68 Ќ— 16/916 подана на рис. 13.24.

|

–исунок 13.24 Ц ”загальнена структурна схема ћ с≥мейства 68 Ќ— 16/916

ƒо складу ц≥Їњ схеми вход€ть:

Ц модуль системноњ ≥нтеграц≥њ SIM або SCIM, €кий призначено дл€ забезпеченн€ функц≥онуванн€ процесора ≥ його сум≥сноњ роботи з ≥ншими пристро€ми системи. ¬≥н генеруЇ ≥мпульси тактовоњ синхрон≥зац≥њ; контролюЇ за допомогою вартового таймера функц≥онуванн€ системи; зреал≥зовуЇ ≥нтерфейс з перифер≥йним устаткуванн€м; формуЇ пер≥одичн≥ запити перериванн€;

Ц таймерний модуль GPT або CTM. …ого побудова ≥ функц≥ональне призначенн€ Ї аналог≥чн≥ до таймерних модул≥вм с≥мейства 68 Ќ— 11/711 та 68 Ќ— 12/912. ƒо складу модул€ GPT входить пристр≥й дл€ формуванн€ сигнал≥в з широтно-≥мпульсною модул€ц≥Їю;

Ц процесор часових ≥нтервал≥в TPU, €кий входить до складу де€ких моделей, призначений дл€ виконуванн€ низки функц≥й формуванн€ часових ≥нтервал≥в, вм≥щуЇ 16 таймерних канал≥в, котр≥ можуть програмуватис€ ≥ працювати без участ≥ процесора;

Ц модуль багатоканального посл≥довного ≥нтерфейсу MCCI, вм≥щуЇ синхронний порт SPI та два асинхронних порти SCI. ѓхнЇ функц≥онуванн€ Ї аналог≥чне до однойменних порт≥в ћ с≥мейства 68 Ќ— 05/705 та 68 Ќ— 11/711;

Ц модуль посл≥довного ≥нтерфейсу QSM використовуЇтьс€ в де€ких модел€х с≥мейства ≥ вм≥щуЇ один асинхронний порт SCI ≥ модиф≥кований вар≥ант синхронного порту QSPI, котрий маЇ в своЇму склад≥ буферну памТ€ть, що надаЇ змогу зорган≥зовувати передаванн€ блок≥в даних обс€гом до 32-х байт без участ≥ процесора;

Ц модуль аналого-цифрового перетворювача виконуЇ 8- або 10-б≥тне перетворюванн€ сигнал≥в, €к≥ надход€ть з 8-ми аналогових вход≥в.

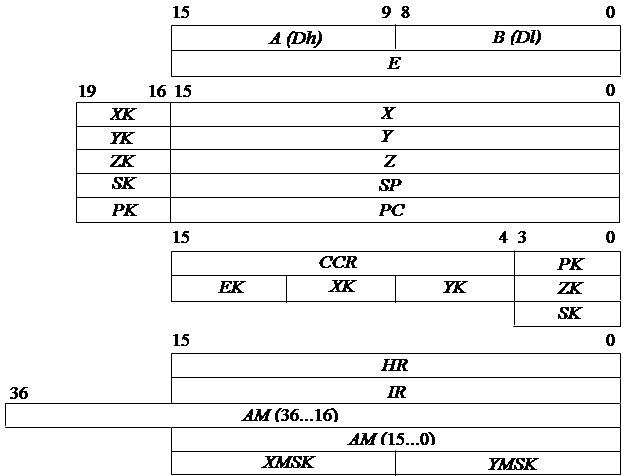

ѕроцесор CPU 16 виконуЇ обробку 8-, 16- та 32-розр€дних операнд≥в ≥ маЇ систему команд, до складу €коњ входить 264 команди. –ег≥строву модель процесора наведено на рис. 13.25.

|

–исунок 13.25 Ц –ег≥строва модель процесора CPU 16

ƒо рег≥стровоњ модел≥ вход€ть:

Ц два 8-розр€дних акумул€тора Ц ј та ¬, котр≥ при обробц≥ 16- та 32-розр€дних операнд≥в використовуютьс€ €к один 16-розр€дний акумул€тор D;

Ц додатковий 16-розр€дний акумул€тор ≈;

Ц три 16-розр€дних ≥ндексних рег≥стри Ц X, Y, Z, котр≥ використовуютьс€ дл€ адресуванн€ операнд≥в;

Ц 16-розр€дний вказ≥вник стека SP;

Ц 16-розр€дний л≥чильник команд –—.

¬с≥ ≥ндексн≥ рег≥стри, вказ≥вник стека ≥ л≥чильник команд мають 4-розр€дне розширенн€, в≥дпов≥дно XK, YK, ZK, SK, PK. ÷≥ розширенн€ використовуютьс€ дл€ адресуванн€ 16-ти банк≥в памТ€т≥, на котр≥ под≥лено адресний прост≥р ћ . ¬иб≥р банку зд≥йснюЇтьс€ за допомогою 4-розр€дного розширенн€ адреси ≈ ≥ значень в≥дпов≥дних розширень. –озширенн€ ≈ , XK, YK, ZK поЇднано в один 16-розр€дний рег≥стр . –озширенн€ л≥чильника команд – розм≥щено у молодших розр€дах рег≥стра ознак CCR, а розширенн€ вказ≥вника стека SP Ц в окремому 4-розр€дному рег≥стр≥ SK.

ƒо рег≥стровоњ модел≥ також вход€ть спец≥ал≥зован≥ рег≥стри HR, IR, AM, MR, котр≥ використовуютьс€ при виконуванн≥ посл≥довного множенн€-додаванн€ дробових чисел при виконуванн≥ цифровоњ обробки сигнал≥в ≥ два 8-розр€дних рег≥стри Ц XMSK та YMSK Ц задл€ збер≥ганн€ масок, котр≥ визначають обс€г буферного модул€ памТ€т≥ при виконуванн≥ команд множенн€ з накопиченн€м ћј—.

¬м≥ст рег≥стра умов CCR подано на рис. 13.26.

|

–исунок 13.26 Ц ¬м≥ст рег≥стра умов CCR

ƒо складу рег≥стра умов вход€ть:

- – Ц 4 розр€ди розширенн€ програмного л≥чильника;

- SM Ц ознака Унасиченн€Ф результату в акумул€тор≥ јћ;

- IP Ц маска запиту перериванн€;

- EV Ц ознака поширенн€ результату в акумул€тор≥ јћ;

- MV Ц ознака переповнюванн€ результату в акумул€тор≥ јћ.

≤нш≥ б≥ти Ц S, H, N, Z, V, C Ц мають призначенн€, аналог≥чне до таких самих ознак процесора CPU 11, 12.

Ѕ≥ти SM, EV, MV використовуютьс€ при виконуванн≥ операц≥й цифровоњ обробки сигнал≥в.

ћ с≥мейства 68 Ќ— 16/916 забезпечують конвеЇризац≥ю при виконуванн≥ програм, ≥ черга з 6-ти команд збер≥гаЇтьс€ у пристроњ керуванн€ процесора. “ому поточне значенн€ вм≥сту програмного л≥чильника разом з розширенн€м – :–—, що визначаЇ адресу наступноњ команди, маЇ значенн€ на 6 б≥льше за значенн€ старшого байта поточноњ команди.

13.1.3 32-розр€дн≥ м≥кроконтролери

¬с≥ ћ с≥мейства 683 хх побудовано з використанн€м 32-розр€дного процесорного €дра CPU 32 ≥ перифер≥йних модул≥в. ÷≥ пристроњ поЇднуютьс€ за допомогою стандартноњ м≥жмодульноњ шини. Ѕ≥льш≥сть перифер≥йних модул≥в Ї аналог≥чн≥ до перифер≥йних модул≥в ћ с≥мейства 68 Ќ— 16/916.

јрх≥тектура ћ 683 хх базуЇтьс€ на принципах, що њх було закладено в с≥мейство м≥кропроцесор≥в ћ— 68000, що дозвол€Ї мати обс€г адресного простору до 16 ћбайт ≥ використовувати програмне забезпеченн€, €ке розроблено дл€ процесор≥в цього с≥мейства. ¬≥дпов≥дно до особливостей арх≥тектури, Ї певна р≥зниц€ при виконуванн≥ програм операц≥йноњ системи ≥ програм користувача. “обто ћ може функц≥онувати у двох режимах: режим≥ суперв≥зора (виконуванн€ програм операц≥йноњ системи) ≥ режим≥ користувача (виконуванн€ програм користувача). «а роботи в режим≥ суперв≥зора при виконуванн≥ програм дозвол€Їтьс€ доступ до вс≥х ресурс≥в системи; команди, €к≥ виконуютьс€ лише в цьому режим≥, називають прив≥лейованими. ¬ режим≥ суперв≥зора користувач маЇ можлив≥сть звертатис€ до рег≥стр≥в ≥ ком≥рок памТ€т≥, €к≥ вход€ть до складу перифер≥йних модул≥в. ѕри включенн≥ ћ розпочинаЇ функц≥онувати в режим≥ суперв≥зора, ≥ за ≥н≥ц≥ал≥зац≥њ операц≥йна система визначаЇ режим подальшоњ роботи. ѕереведенн€ до режиму суперв≥зора зд≥йснюЇтьс€ при встановленн≥ в≥дпов≥дного б≥та в рег≥стр≥ ознак процесора ≥ при подальш≥й робот≥ режим не зм≥нюЇтьс€. ѕоверненн€ до режиму користувача виконуЇтьс€ лише при обробц≥ виключних ситуац≥й або повторному перезапуску. ÷≥ особливост≥ в≥дображено в рег≥стров≥й модел≥ процесора CPU 32.

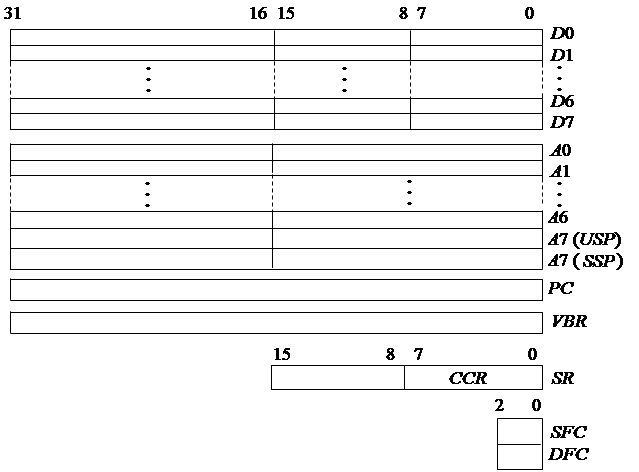

–ег≥строву модель процесора CPU 32 наведено на рис. 13.27.

ƒо складу рег≥стровоњ модел≥ вход€ть:

Ц 2 групи 32-розр€дних рег≥стр≥в:

8 рег≥стр≥в даних, €к≥ можуть працювати з даними, що Ї байтами, словами та довгими словами;

8 рег≥стр≥в адреси, в котрих рег≥стр ј 7 Ї дубльованим; в≥н використовуЇтьс€ в €кост≥ вказ≥вника стека, дл€ роботи в режим≥ суперв≥зора маЇ назву SSP, а при робот≥ в режим≥ користувача Ц USP.

Ц –— Ц 32-розр€дний програмний л≥чильник; в процесор≥ CPU 32 використовуютьс€ лише 24 розр€ди, в≥дпов≥дно до розр€дност≥ шини даних ≥ обс€гу адресного простору;

Ц SR Ц 16-розр€дний рег≥стр стану; складаЇтьс€ з двох частин, кожна з котрих маЇ розр€дн≥сть: системного байта ≥ байта користувача (рег≥стру ознак Ц CCR). –ег≥стр SR Ї повн≥стю доступним в режим≥ суперв≥зора. ¬ режим≥ користувача доступ Ї можливий лише до байта користувача. ¬м≥ст рег≥стра SR подано на рис. 13.28;

Ц рег≥стри VBR, SFC, DFC Ї доступними лише в режим≥ суперв≥зора. 32-розр€дний рег≥стр VBR вм≥щуЇ базову адресу таблиц≥ вектор≥в виключень, завантаженн€ цього рег≥стра проводитьс€ прив≥лейованою командою MOVEC. –ег≥стри SFC, DFC використовуютьс€ при виконуванн≥ процесором прив≥лейованоњ команди MOVEC, котра зреал≥зовуЇ пересиланн€ даних пом≥ж рег≥страми D 7...0 або ј 7...0 ≥ зовн≥шньою памТ€ттю. ѕ≥д час записуванн€ даних до памТ€т≥ вм≥ст рег≥стра DFC використовуЇтьс€ в €кост≥ функц≥онального коду FC 2...0, а при завантажуванн≥ рег≥стр≥в в €кост≥ функц≥онального коду FC 2...0 використовуЇтьс€ вм≥ст SFC. ¬ такий спос≥б в≥дбуваЇтьс€ орган≥зац≥€ додаткових банк≥в памТ€т≥ ≥ розширюЇтьс€ загальний адресний прост≥р.

|

–исунок 13.27 Ц –ег≥строва модель процесора CPU 32

|

–исунок 13.28 Ц ‘ормат вм≥сту рег≥стра стану SR

ƒо рег≥стра стану SR вход€ть б≥ти:

системн≥ ознаки:

Ц “ 1 Ц ознака трасуванн€ по програмних переходах; значенн€ “ 1 = 1 зупин€Ї виконуванн€ п≥сл€ кожноњ команди передаванн€ керуванн€ (умовних, безумовних переход≥в);

Ц “ 0 Ц ознака трасуванн€; встановленн€ б≥та “ 0 = 1 переключаЇ процесор до покрокового режиму, програма зупин€Їтьс€ п≥сл€ виконанн€ кожноњ команди;

Ц S Ц ознака суперв≥зора, значенн€ ц≥Їњ ознаки S = 1 в≥дпов≥даЇ функц≥онуванню процесора в режим≥ суперв≥зора;

Ц ≤– 2-0 Ц маска запит≥в перериванн€, визначаЇ р≥вень пр≥оритету обслуговуванн€ поточного запиту перериванн€;

ознаки користувача:

Ц ’ Ц ознака розширенн€ результату, при виконуванн≥ б≥льшост≥ операц≥й коп≥юЇ значенн€ б≥та —; у де€ких випадках значенн€ цього б≥та формуЇтьс€ в залежност≥ в≥д виконуваноњ операц≥њ;

Ц N Ц ознака знаку; збер≥гаЇ коп≥ю знакового розр€ду результату операц≥њ; значенн€ ознаки N = 1 в≥дпов≥даЇ в≥дТЇмному результатов≥;

Ц Z Ц ознака нульового результату; при виниканн≥ результату, €кий дор≥внюЇ 0, ознака набираЇ значенн€ 1;

Ц V Ц ознака переповнюванн€; набираЇ значенн€ V = 1 в раз≥ переповнюванн€ розр€дноњ с≥тки при обробц≥ операнд≥в з≥ знаком;

Ц C Ц ознака перенесенн€; зд≥йснюЇ перенесенн€ з≥ старшого розр€ду при виконуванн≥ арифметичних операц≥й та збер≥гаЇ вм≥ст розр€ду, €кий було висунуто, при виконуванн≥ операц≥й зсув≥в; набираЇ значенн€ — = 1 при виниканн≥ перенесенн€ з≥ старшого розр€ду результату виконуваноњ операц≥њ.

онтрольн≥ питанн€:

1 „им в≥др≥знюютьс€ м≥кроконтролери р≥зних моделей ф≥рми Motorola?

2 як≥ пристроњ можуть входити до складу м≥кроконтролер≥в?

3 як≥ рег≥стри вход€ть до складу процесорного €дра CPU 05 ≥ €ке Ї функц≥ональне призначенн€ кожного з них?

4 як≥ ознаки результату формуютьс€ при робот≥ ћ с≥мейства ћ 68 Ќ— 05/705?

5 як≥ посл≥довн≥ ≥ паралельн≥ порти вход€ть до складу ћ с≥мейства ћ 68 Ќ— 05/705?

6 який обс€г маЇ стек в ћ с≥мейства ћ 68 Ќ— 05/705 ≥ €ку адресу маЇ вказ≥вник вершини при початковому завантаженн≥?

7 яке призначенн€ маЇ блок конф≥гурац≥њ ≥ €к≥ рег≥стри до нього вход€ть в ћ с≥мейства ћ 68 Ќ— 05/705?

8 ¬ чому пол€гаЇ функц≥ональне призначенн€ б≥т≥в рег≥стра MOR ћ ћ— 68 Ќ— 705 J 1 ј ≥ в €кий спос≥б в≥дбуваЇтьс€ зм≥нюванн€ њхнього вм≥сту?

9 як≥ рег≥стри вход€ть до складу блока конф≥гуруванн€ ћ ћ— 68 Ќ— 705 — 8 ј?

10 яке призначенн€ маЇ блок контролю функц≥онуванн€ћ с≥мейства ћ 68 Ќ— 05/705?

11 ¬ чому пол€гаЇ виконанн€ процедури непрограмованого скиданн€ ћ с≥мейства ћ 68 Ќ— 05/705?

12 ” €кий спос≥б в≥дбуваЇтьс€ керуванн€ процесом обм≥ну даними через асинхронний порт ћ с≥мейства ћ 68 Ќ— 05/705?

13 ” €кий спос≥б в≥дбуваЇтьс€ керуванн€ процесом обм≥ну даними через синхронний порт ћ с≥мейства ћ 68 Ќ— 05/705?

14 як≥ сигнали формуютьс€ при орган≥зац≥њ синхронного обм≥ну через порт SPI ћ с≥мейства ћ 68 Ќ— 05/705?

15 ” €кий спос≥б побудовано багатофункц≥ональний таймер в ћ с≥мейства ћ 68 Ќ— 05/705?

16 ѕризначенн€ б≥т≥в рег≥стра керуванн€-стану блока MFT?

17 ” €кий спос≥б визначаютьс€ часов≥ ≥нтервали встановленн€ ознаки пер≥одичного перериванн€ в блоц≥ MFT?

18 ƒе збер≥гаЇтьс€ адреса поверненн€ до головноњ програми в пер≥од виконуванн€ п≥дпрограми?

19 „им в≥др≥знюютьс€ системи синхронного та асинхронного посл≥довного обм≥ну?

20 як≥ сигнали використовуютьс€ дл€ орган≥зац≥њ синхронного обм≥ну даними через порт SPI?

21 як≥ два генератори ≥мпульс≥в вход€ть до складу модул€ формуванн€ тактових сигнал≥в CGM 08?

22 яке призначенн€ маЇ модуль системноњ ≥нтеграц≥њ SIM 08?

23 „им в≥др≥знюютьс€ рег≥стров≥ модел≥ процесор≥в CPU 05 та 68 HC 11?

24 як≥ особливост≥ побудови властив≥ 16-розр€дним ћ ?

25 як≥ пристроњ вход€ть до складу ћ с≥мейства 68 Ќ— 16/916 ≥ €ке вони мають призначенн€?

26 як≥ рег≥стри вход€ть до складу рег≥стровоњ модел≥ процесора CPU 16?

27 як≥ рег≥стри вход€ть до складу рег≥стровоњ модел≥ процесора CPU 32?

28 як≥ ћ можуть виконувати операц≥њ цифровоњ обробки сигнал≥в?

онтрольн≥ питанн€ п≥двищеноњ складност≥:

1 ” €кий спос≥б можна запрограмувати ћ ћ— 68 Ќ— 705 J 1 A дл€ роботи ≥з зовн≥шним генератором тактових ≥мпульс≥в?

2 «апрограмуйте ћ ћ— 68 Ќ— 705 J 1 A на прийманн€ зовн≥шн≥х запит≥в на перериванн€ по каналах –ј 3... –ј 0.

3 «апрограмуйте режим непрограмного скиданн€ у ћ с≥мейства ћ68Ќ—05/705.

4 —формуйте керувальне слово, €ке сл≥д записати до рег≥стра SCCR 1 MK MC 68 HC 705 C 8 A задл€ вмиканн€ приймача при надходженн≥ даних довжиною 1 байт з≥ значенн€м одиниц≥ в старшому розр€д≥ ≥ дл€ запису значенн€ б≥та контролю з прийн€того сигналу.

5 ўо станетьс€ з прийн€тою ≥нформац≥Їю, €кщо в рег≥стр≥ стану SCSR MK MC 68 HC 705 C 8 A буде записано:

6 ” €кий спос≥б в≥дбувалас€ робота вартового таймера ћ ћ— 68 Ќ— 705 J 1 ј, €кщо в рег≥стр≥ керуванн€-стану TSCR буде записано:

7 Ќазв≥ть причину перезавантаженн€ ћ с≥мейства M 68 HC 08/908, €кщо у рег≥стр≥ стану LVISR буде записано:

|

8 —формуйте керувальне слово дл€ ћ ћ—68Ќ—11/711 задл€ забезпеченн€:

Ц включенн€ модул€ ј÷ѕ та його синхрон≥зац≥њ в≥д генератора тактових ≥мпульс≥в ћ ;

Ц перериванн€ при надходженн≥ зр≥зу ≥мпульса на вход≥ IR