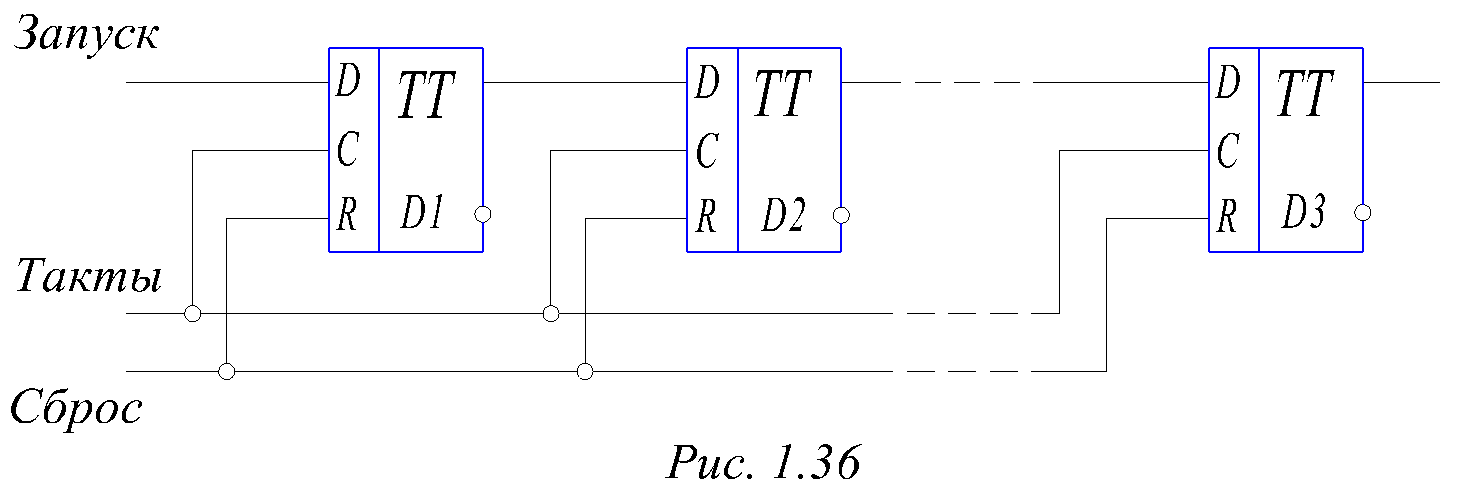

Ѕолее целесообразна тактируема€ задержка. ќна реализуетс€ последовательно включенной цепочкой D Ц триггеров, как показано на рис. 1.36. оличество триггеров S определ€ет врем€ задержки “« = ST, где “ Ц период следовани€ тактовых импульсов.

–исунок 1.36. Ц —хема задержки на S тактов

ќсобенностью рассмотренной схемы €вл€етс€ то, что длительность управл€ющих импульсов может быть произвольной; длительность выходных импульсов пропорциональна входным, но кратна “. роме того, путем незначительного усложнени€ схемы врем€ задержки можно регулировать. ƒл€ этого выходы триггеров подключаютс€ через управл€емый мультиплексор.

–егистры

–егистры в цифровой технике нос€т исключительный характер вследствие многообрази€ выполн€емых ими функций. ќни могут быть просто элементами пам€ти, могут выполн€ть функции преобразователей кода. ќни используютс€ как составна€ часть более сложных устройств, например, микропроцессоров, сложных систем управлени€, в том числе программируемых.

ќбычно прин€то выдел€ть последовательные и параллельные регистры. ќни отличаютс€ методами занесени€, хранени€ и выдачи кодов. ¬озможны универсальные, последовательно Ц параллельные регистры.

јппаратна€ реализаци€ регистров может быть различной, включа€ из физическую природу. ћы основной упор сделаем на D Ц триггерах, поскольку они наиболее благопри€тны дл€ ѕЋ»—.

”ниверсальный последовательно Ц параллельный регистр на 4 разр€да изображен на рис. 1.37. –егистр состоит из 4 D Ц триггеров D1 Ц D4. ¬ход первого триггера (¬х 1) может служить дл€ ввода последовательного кода. ƒл€ этого одновременно с кодом на управл€ющий вход подаютс€ 4 продвигающих импульса. “ребование к ним: они должны подаватьс€ с частотой импульсов последовательного кода, причем желательно, чтобы фронты продвигающих импульсов приходились на средины импульсов входного кода. Ёто позволит снизить зависимость от дрожани€ фронтов.

ѕеред началом работы регистра его нужно очистить, т.е. привести все триггеры в 0, дл€ чего на все их входы R подаетс€ импульс Ђ—бросї.

ѕосле занесени€ кода в регистр и прекращени€ подачи продвигающих импульсов информаци€ в нем может хранитьс€ любое врем€. ≈е можно убрать двум€ способами: или обычным сбросом (тогда она стираетс€), или подачей на управл€ющий вход продвигающих импульсов. “огда на выходе последовательного кода (¬ых 1) по€вл€етс€ код дл€ его приема другими устройствами. ≈сли код в регистр занесен, а продвигающих импульсов нет, регистр по сути выполнил функцию преобразовател€ последовательного кода в параллельный.

–исунок 1.37. Ц ”ниверсальный регистр

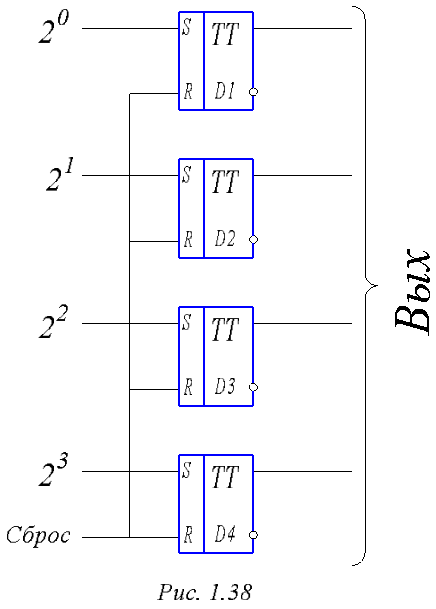

≈сли ¬х 1 не задействовать, а подавать параллельный код на входы безусловной установки S, то регистр просто сохранит эту информацию. ѕри этом она может быть считана в любое врем€, т.е. асинхронно по вых 2 или считаетс€ в последовательном коде с ¬ых 2. ѕри этом регистр очищаетс€. Ёто и есть преобразование параллельного кода в последовательный.

¬озможен и такой вариант включени€. Ќа входе устанавливаетс€ схема »Ћ» (показана штриховой линией). ≈сли в регистр занести код по последовательному или параллельному входу, а потом подавать на управл€ющий вход тактовые импульсы, образуетс€ динамический регистр, в котором этот код циркулирует до сброса.

|

|

|

ѕри использовании ѕЋ»— легко можно увеличить емкость такого регистра до любого нужного числа разр€дов.

Ќа электрических схемах регистры часто изображаютс€ в виде, приведенном на рис. 1.39. ¬ особых комментари€х это изображение не нуждаетс€.

–исунок 1.38. - ѕараллельный регистр

–исунок 1. 39 - »зображение регистра

—четчики

—реди множества различных типов счетчиков рассмотрим простейший Ц счетчик двоичного кода на D Ц триггерах. —хема четырехразр€дного двоичного счетчика приведена на рис. 1.40. D Цтриггеры D1Е. D4 работают в счетном режиме за счет обратных св€зей на D Ц входы. “риггеры включены последовательно, в результате чего каждый последующий триггер образует как бы старший разр€д относительно предыдущего. ќбща€ шина Ђ—бросї заводитс€ на все R - входы триггеров. —четчик легко можно синтезировать на любое число разр€дов.

–исунок 1.40. - „етырехразр€дный двоичный счетчик

Ќа рис. 1.41 показано изображение счетчика на принципиальных схемах.

–исунок 1.41. Ц »зображение счетчика

–аспределители импульсов

Ёто специализированные устройства с одним тактовым входом и несколькими выходами, причем в каждый момент времени единица присутствует только на одном из входов, а переключение выходов делаетс€ поочередно. –аспределители (–) предназначены дл€ управлени€ сложными системами путем разнесени€ очередности выполнени€ ими операций во времени.

¬озможны два варианта реализации распределителей: на D Ц триггерах и на счетчиках с дешифраторами. ѕервый вариант, на D Ц триггерах, приведен на рис. 1.42. “риггеры D1 Ц D3 образуют последовательную сдвиговую цепочку, а элементы D4 и D5 реализуют обратную св€зь дл€ автоматического продолжени€ работы. ѕри подаче импульса Ђ«апускї единица последовательно перемещаетс€ по цепочке триггеров. огда единица проходит последний триггер, на выходе D4 по€вл€етс€ 1, повторно запускающа€ схему. ќб€зательное условие при этом Ц ограничение на длительность запускающих импульсов. ≈сли она превышает период тактовой частоты. ¬ыходные импульсы распределител€ взаимно перекрываютс€.

–исунок 1.42. - –аспределитель импульсов на D - триггерах

¬торой вариант распределител€ приведен на рис.1.43. ѕри подаче тактовых импульсов на вход — счетчика коды на его выходах последовательно возрастают, в результате чего на выходах дешифратора последовательно по€вл€ютс€ импульсы. —хема сложнее предыдущей, но работает более надежно.

–исунок 1.43. - –аспределитель, 2 вар.

√енераторы псевдослучайных последовательностей

√енераторы псевдослучайных последовательностей (далее ѕ—ѕ) €вл€ютс€ очень важной составл€ющей инженерной практики. ќни используютс€ в множестве практических приложений, в том числе при испытании новой техники, моделировании внешних воздействий, отказов элементов и т.д.

√енераторы ѕ—ѕ объективно сравниваютс€ по следующим характеристикам.

1. ѕериод повторени€ “ѕ. ак правило, после некоторого цикла работы выходные коды генератора повтор€ютс€. „ем длиннее период, тем качественнее генератор. ≈сли генератор вырабатывает кодовые последовательности размером в R разр€дов, максимальный период повторени€ составл€ет 2R слов.

2. –авномерное распределение значений в выделенном диапазоне. „аще всего это диапазон от 0 до 1; в противном случае его нормируют.

|

|

|

3. —оседние члены ѕ—ѕ не должны быть св€занными друг с другом. Ёто выражаетс€ в том, что коррел€ционна€ функци€ ѕ—ѕ должна быть близкой к δ - функции, а ее спектральна€ плотность должна быть равномерной в достаточно большом диапазоне.

Ќа рис. 1.44 приведен классификатор шумовых последовательностей

–исунок 1.44. - лассификатор шумовых последовательностей

ак видно из классификатора, существует два типа генераторов. ѕерва€ группа, собственно генераторы шума, используют естественные источники и не применимы дл€ ѕЋ»—. ќстановимс€ более подробно на второй составл€ющей классификатора. —реди множества линейных генераторов ѕ—ѕ наиболее применимы генераторы последней группы.

»сторически первые генераторы ѕ—ѕ использовали деление двух чисел по рекурсивной процедуре, заключающейс€ в следующих шагах.

1. ¬ыбираютс€ два числа, ј и ¬. „исла должны быть взаимно простыми, т.е. не иметь общих сомножителей. ѕроизводитс€ деление ј на ¬ с получением частного —.

2. ¬ыбираетс€ часть частного и делитс€ на ¬.

ƒалее процедура 2 повтор€етс€ до получени€ результата, совпадающего с первым частным. ќчевидно, что следующие делени€ приведут к повторению последовательности.

Ќедостатком этого метода €вл€етс€ трудность подбора делимого и делител€, так как от этого зависит период повторени€. роме того, сама операци€ делени€ достаточно продолжительна€, что ограничивает производительность генератора.

ћодификаци€ этого метода - целочисленное деление в кольце по модулю 2. ѕри этом используетс€ деление полубесконечного кода 1000000... на образующий полином []. ѕроцедура и схемотехника делени€ будут показаны в разделе "корректирующие коды". ¬ данном разделе отметим следующие особенности метода.

а) —ильна€ зависимость от выбора образующего полинома. ѕоиск неприводимых полиномов высоких степеней €вл€лс€ ранее достаточно сложной задачей. —ейчас она разрешима в св€зи с заметно возросшей производительностью современных микропроцессорных и компьютерных систем.

б) ∆елательно производить поиск дл€ полиномов нечетных степеней, так как при нечетных степен€х количество неприводимых полиномов больше.

в) —ледует учитывать один недостаток метода: если текущий остаток начинаетс€ с 0, следующий определитс€ обычным сдвигом кода на разр€д влево, т.е. неслучаен. “о же наблюдаетс€ дл€ двух и более 0 в начале остатка. Ёто вли€ет на коррел€ционную функцию потока случайных кодов.

ƒл€ автоматизации поиска неприводимых полиномов следует использовать следующие особенности неприводимых полиномов.

1. од неприводимого полинома степени s начинаетс€ и оканчиваетс€ 1. Ёто сокращает врем€ поиска, так как количество претендентов снижаетс€ вчетверо.

2. Ќеприводимый полином €вл€етс€ нерегул€рным и несимметричным. Ќапример, коды типа 10000...1 или 10101...01 можно не рассматривать при поиске.

3. ≈сли некоторый полином оказалс€ неприводимым, то неприводим и полином с инверсией его разр€дов. ѕростой пример: полином 1011 неприводим; тогда и полином 1101 также неприводим

јлгоритм поиска неприводимых полиномов выгл€дит достаточно просто. »з множества претендентов на неприводимость составл€етс€ список претендентов с учетом предыдущих ограничений. ¬ыбираетс€ первый элемент из списка, после чего проводитс€ деление на него кода 10000000... с вычислением количества полученных остатков. ≈сли оно составл€ет дл€ полинома степени S значение 2S - 1, полином неприводим, как и его зеркальное отображение. ѕосле этого провер€етс€ следующий претендент из списка. ќтметим, что при возрастании S количество неприводимых полиномов возрастает в показательной зависимости, причем дл€ четной и нечетной степеней показатели различны.

ѕредложенную методику вычислени€ неприводимых полиномов можно вз€ть за основу построени€ генераторов ѕ—ѕ более высоких степеней. ѕриведем некоторые, €вл€ющиес€ оригинальными творени€ми авторов.

1. ѕусть задано некоторое множество неприводимых полиномов степени S. ѕроизведение двух и более таких полиномов может быть вз€то за основу генератора ѕ—ѕ. ѕусть полученный при этом полином степени 2S приводим, в качестве генератора ѕ—ѕ он будет иметь более высокие характеристики, чем исходный.

|

|

|

2. ѕсевдослучайна€ последовательность существенно зависит от выбора начального значени€. ѕри этом возможен следующий вариант ее удлинени€. ѕри первоначальном задании кода начального значени€ генератор вырабатывает последовательность случайных чисел из R значений, после чего задаетс€ другой код. ≈го можно вз€ть, например, изменив предыдущий на 1 или на другое оговоренной число. ћожно использовать принцип автоключа, выбрав в качестве очередного начального значени€ последнюю кодовую комбинацию с выхода генератора. ≈ще один вариант - циклический сдвиг влево или вправо предыдущего начального значени€.

3. ќсновной признак окончани€ ѕ—ѕ - по€вление не его выходе кода 1000000.... ƒальше коды ѕ—ѕ повтор€ютс€. ѕоэтому в любом случае по€вление такого кода на выходе автоматически должно приводить к изменению режима работы генератора одним из описанных выше способов.

3 Ћабораторный практикум на базе ѕЋ»— XC9572XL

3.1. ќписание стенда

ћикросхема XC9572XL была выбрана из-за р€да преимуществ, таких как:

1) ѕЋ»— с архитектурой CPLD;

2) самое большое количество циклов запись/стирание (не менее 10 тыс.);

3) доступность и относительна€ дешевизна;

4) большой срок хранени€ конфигурации;

5) поддержка JTAG;

6) простота программировани€;

7) бесплатное программное обеспечение дл€ разработок;

8) наличие большой библиотеки элементов.

ћикросхема XC9572XL Ц высокопроизводительна€ ѕЋ»— семейства XC9500XL, емкостью 1600 логических вентилей и минимальной задержкой распространени€ сигнала контакт Ц контакт (5 нс). —остоит из четырех 54V18 функциональных блоков. [7] Ќа рис. 3.1 изображена структурна€ схема стенда.

–исунок 3.1 Ц —труктурна€ схема стенда

Ќа рис.3.2 изображен внешний вид стенда

–исунок 3.2 - ¬нешний вид стенда

«десь (дальше описание всех элементов стенда)

3.2. ѕринципиальна€ схема платы ѕЋ»—

Ќа рисунке 3.3 изображена принципиальна€ схема ѕЋ»—.

–исунок 3.3 Ц ѕринципиальна€ схема ѕЋ»—

ѕлата ѕЋ»— состоит из:

-ћикросхемы ѕЋ»— (D1);

- варцевого генератора на 50 ћ√ц (D2, L1, C1);

- —ветодиодного индикатора подачи напр€жени€ на плату (VD1, R1);

- ѕреобразовател€ напр€жени€ (C2,C3,C4,C5,D3);

- ѕользовательских разъемов (’1, ’2, ’3, ’4).

3.2. ѕринципиальна€ схема стенда

Ќа рисунке 3.4 изображена принципиальна€ схема стенда

–исунок 3.4. Ц ѕринципиальна€ схема стенда

ѕлата учебного стенда имеет в своем составе разъемы:

- X1 Ц дл€ подключени€ к компьютеру;

- X2 Ц дл€ подключени€ к плате ѕЋ»— (разъем программировани€);

- X3, X4 Ц пользовательские разъемы.

“акже на плате расположены:

- ѕрограмматор, состо€щий из блока X1, резисторов R1 - R14, диодов VD1, VD2, конденсаторов C1 Ц C5, блока X2, D1,D2;

- „етырехсимвольный семисегментный индикатор (VT1, VT2,VT3, VT4);

- Ѕлок светодиодов (VD3, VD4, VD5, VD6, VD7, VD8, VD9, VD10);

- Ѕлок переключателей (SW1, SW2, SW3, SW4, SW5, SW6, SW7, SW8);

- Ѕлок кнопок (BTN1, BTN2, BTN3, BTN4, BTN5, BTN6).

3.3. —оставл€ющие элементы стенда

—ветодиоды

¬осемь отдельных светодиодов подключены к выходам ѕЋ»— (LD1- P27, LD2- P28, LD3- P29, LD4- P30, LD5- P31, LD6- P32, LD7- P33, LD8- P34.

Ќа рис. 3.5 изображена схема подключени€ светодиодов.

–исунок 3.5. Ц —хема подключени€ светодиодов

нопки

ѕ€ть кнопок подключены к выходам ѕЋ»— (BTN1- P44, BTN2- P43, BTN3- P42, BTN4- P40, BTN5- P41,). нопки присоединены к VCC3.3 через резистор 47кќм. огда кнопка нажата, ее контакты подключаютс€ к Ђземлеї через резистор 4.7кќм. Ќа делителе напр€жени€ 47кќм - 4.7кќм (1/10 от VCC3.3) возникает сигнал логического нул€ и держитс€ все врем€ пока кнопка нажата. ѕодавление дребезга обеспечивают RC - фильтр и триггер Ўмитта D1. Ёта схема создает высокий логический сигнал, когда кнопка нажата.

|

|

|

Ќа рис. 3.6 изображена схема подключени€ кнопок.

–исунок 3.6. Ц —хема подключени€ кнопок

ѕереключатель

¬осемь переключателей подключены к выходам ѕЋ»— (SW1- P19, SW2- P18, SW3- P16, SW4- P14, SW5- P36, SW6- P37, SW7- P38, SW8-P39). ѕереключатели используют 4.7 кќм резистор дл€ токовой защиты входов ѕЋ»—.

Ќа рис.3.7 изображена схема подключени€ переключателей.

–исунок 3.7. Ц —хема подключени€ переключателей

—ветодиодный дисплей

—емисегментный светодиодный дисплей подключен к выходам ѕЋ»— (a- P13, b- P22, c- P23, d- P5, e- P12, f- P8, g- P6, dp-P7, A1- P20, A2- P21, A3- P3, A4- P2).

атоды всех 32 сегментов (см. рис. 3.8) на дисплее собраны в 8 групп (—ј, —¬, ——, CD, CE, CF, CG, DP). јноды всех 32 сегментов на дисплее собраны в 4 группы.

.

–исунок 3.8. Ц —хема подключени€ светодиодного диспле€

—хема создает мультиплексированный дисплей и организована по принципу динамической индикации.

Ћабораторна€ работа є1

»зучение системы проектировани€ Xilinx ISE Design Suite 14.4.

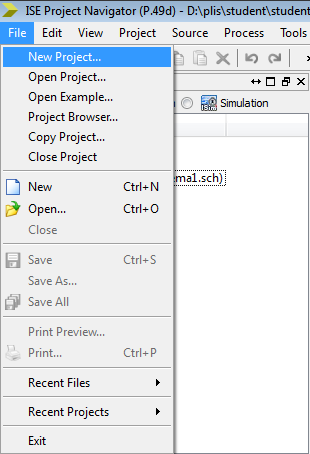

1. —оздание нового проекта.

1.1.ƒл€ запуска программы находим на рабочем столе ISE Design Suite 14.4.

Ќа рис. 3.9 изображен €рлык программыISEDesignSuite 14.4.

–исунок 3.9 -ярлык программы ISE Design Suite 14.4.

1.2.¬ верхнем левом углу панели управлени€ программы (см. рис. 3.10) выберите: Project Setting Project.

.

–исунок 3.10. - ѕанель NewProject

1.3. Ќа экране по€витс€ окно дл€ указани€ места \

Ќа рис. 3.11 изображена панель Create New Project.

–исунок 3.11 - ѕанель Create New Project

1.¬ведите им€ проекта: Name

2. ”кажите место расположени€: Location

3.¬ыберите основной тип проекта: Schematic

4.«атем нажмите: Next

1.4.ќкно настройки проекта: Project Setting

Ќа рис. 3.12 изображено окно Project Setting

–исунок 3.12 - ќкно Project Setting

1.¬ строке (Family) выберите семейство ѕЋ»—:XC9500XLCPLDs.

2.¬ строке (Device) выберите ѕЋ»— ƒанного устройства:XC957XL.

3.”кажите (VQ44) комплектацию XC957XL (ѕЋ»—).

4.¬ыберите (Speed) скорость работы.

5. ¬ыберите (PreferredLanguage) подход€щий €зык перевода вашей схемы.

6. Ќажмите (Next).

2. –абота с проектом

ќписание созданного проекта: Project Summary

Ќа рис. 3.13 изображена панель Project Summary

–исунок 3.13. - ќкно Project Summary

ƒл€ завершени€ создани€ проекта нажмите:Finish

¬ыберите на панели управлени€:NewSource

Ќа рис. 3.13 изображено окно New Source

–исунок 3.13 - ќкно New Source

Ќа рис. 3.14 изображено окно Select Source Type

–исунок 3.14 - ќкно Select Source Type

¬ данном окне выберите основной тип создани€ проекта ЂSchematicї затем ЂFile Nameї после чего нажните ЂNext→Finishї.

3. –абота со схемами.

3.1 ѕанель управлени€

Ќа рис.3.15 изображена панель управлени€

–исунок 3.15 - ѕанель управлени€

«десь обозначено:

1-ƒобавить проводник.

2-»зменение имени компонентов схемы.

3-ƒобавление шин.

4-«адание выходов(входов).

5-¬ыбор элементов. 6-¬ыбор размера рабочей области.

3.2 ¬ыбор элементов

ƒл€ выбора элемента в панели инструментов нажмите на значок ЂAdd Symbolї. Ёлементы расположены по категори€м. ¬ыберите элемент и переместите курсор в рабочую область. «атем в нужном вам месте двойным нажатием левой кнопки мыши поставьте элемент

Ќа рис.3.16 изображена панель выбора элементов.

–исунок 3.16 - ѕанель выбора элементов

Ќа рис. 3.17 приведен пример выбранного элемента and2.

–исунок 3/17/ - ѕример выбора элемента

ƒл€ того, чтобы соединить элементы в панели инструментов, нажмите ЂAddWireї затем соедините необходимые вам элементы.

Ќа рис. 3.18 изображен пример схемы.

–исунок 3.18 - ѕример схемы

«атем, использу€ ЂAddI/OMarkerї, задайте дл€ вашей схемы входы и выходы.

Ќа рис.3.19 изображен пример использовани€ AddI/OMarker

–исунок 3.19. - ѕример AddI/OMarker

1.‘ункци€ ЂAddNameї используетс€ дл€ определени€ названий цепей и шин.

2. —трока определени€ имени.

онфигураци€ входов (выходов).

Ќа рисунке 3.20 приведен пример конфигурации входов.

ƒл€ того, чтобы св€зать схему с устройством, необходимо соотнести ее входы (выходы) с входами (выходами) ѕЋ»—. Ёто делаетс€ следующим образом.

1. ¬ыберите вход (выход) вашей схемы; двойным нажатием вызываетс€ окно ЂObject Properties-Net Attributesї.

2. ¬ разделе ЂNetsї выбираем нужный вход (выход).

3. ¬ правом верхнем углу окна нажимаем ЂNewї.

4. ¬ строке ЂAttribute valueї задаем нужный вход (выход). (Ќазвание входов и выходов начинаетс€ с английской буквы Ђ–ї, что означает Pin (вывод), далее идет его номер).

|

|

|

5. Ќажимаем ЂOkї.

–исунок 3.20 - онфигураци€ входов.

ѕеренос схемы на устройство

Ќа рисунке 3.21 изображен перенос схемы на устройство. ƒл€ этого нужно выполнить следующие действи€.

1. ¬ левом нижнем углу программы нажимаем ЂDesignї

2., 3. ƒвум€ нажати€ми левой кнопки мыши выберите ЂImplementDesignї старт проверки схем.

4. ЂSynthesize-XSIї программа осуществл€ет синтез вашей схемы.

5. ЂTranslateї эта операци€ переводит созданный проект (схему) на €зык VHDL.

6. ЂFitї определение ресурсов, зан€тых вашей схемой на ѕЋ»—(XC9572XL).

7. ЂGenerateProgrammingї - генераци€ файла проекта.

8. ƒвойным щелчком запустите ЂManage Configuration Project (IMPACKT)ї - средство переноса программного кода ѕЋ»—.

–исунок 3.21 - ѕеренос схемы на устройство

6. ѕеренос программного кода на ѕЋ»—.

Ќа рисунке 3.22 изображен перенос программного кода.

–исунок 3.22 - ѕеренос программного кода

1. ѕрограмма переноса кода ЂISEIMPACTї.

2. ƒвойным щелчком выберитеЂBoundary Scanї.

3. ¬ыберете ЂInitializeChainї - инициализацию цепи.

4. ќпределение файла с вашим проектом.

5. Ќажмите ЂOkї.

Ќа рисунке 3. 23 изображено окно выбора схемы

–исунок 3.23 - ¬ыбор схемы

1. ƒвойным нажатием откройте ЂAssign New Configuration Fileї.

2. Ќайдите свою схему.

3. Ќажмите Ђќткрытьї.

Ќа рисунке 3.24 изображено окно программировани€.

–исунок 3.24 - ѕрограммирование

ѕроделайте все пункты программировани€ дл€ заданного вам варианта схемы.

Ћабораторна€ работа є2

Ёлементы стандартной логики

÷ель работы: ознакомление с элементами стандартной логики. »зучитьэлементыAND2, AND3, AND3B1, NAND2, OR2, NOR2, NOR3, XOR2, XOR4, INV.

ќбщие указани€

1. Ёлемент AND2. Ќазначение выводов: I0, I1-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=I0&I1. “аблица истинности элемента AND2 приведена в таблице 1.

“аблица 1- таблица истинности элемента AND2

| ¬ходы | ¬ыход | |

| I0 | I1 | O |

| X | ||

| X | ||

2. Ёлемент AND3.Ќазначение выводов: I0, I1, I2-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=I0&I1&I2.“аблица истинности элемента AND3приведена в таблице 2.

“аблица 2- таблица истинности элемента AND3

| ¬ходы | ¬ыход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||

3. Ёлемент AND3B1.Ќазначение выводов: I0, I1, I2-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=~I0&I1&I2. “аблица истинности элемента AND3B1 приведена в таблице 3.

“аблица 3-таблица истинности элемента AND3B1

| ¬ходы | ¬ыход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||

4. Ёлемент NAND2. Ќазначение выводов: I0, I1- входы, ќ- выход. ¬ыполн€ема€ функци€ ќ=~(I0&I1).таблица истинности элемента NAND2 приведена в таблице 4.

“аблица 4-таблица истинности элемента NAND2

| ¬ходы | ¬ыход | |

| I0 | I1 | O |

| X | ||

| X | ||

5. Ёлемент OR2. Ќазначение выводов: I0, I1-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=I0│I1. “аблица истинности элемента OR2 приведена в таблице 5.

“аблица 5- таблица истинности элемента OR2

| ¬ходы | ¬ыход | |

| I0 | I1 | O |

| X | ||

| X | ||

6. Ёлемент NOR2.Ќазначение выводов: I0, I1-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=~(I0│I1). “аблица истинности элемента NOR2 приведена в таблицу 6.

“аблица 6- таблица истинности элемента NOR2

| ¬ходы | ¬ыход | |

| I0 | I1 | O |

| X | ||

| X | ||

7. Ёлемент NOR3. Ќазначение выводов: I0, I1,I2-входы, ќ-выход. ¬ыполн€ема€ функци€ ќ=~(I0│I1│I2). “аблица истинностиэлемента NOR3 приведена в таблице 7.

“аблица 7- таблица истинностиэлемента NOR3

| ¬ходы | ¬ыход | ||

| I0 | I1 | I2 | O |

| X | X | ||

| X | X | ||

| X | X | ||