Когда микропроцессор с рассмотренной шинной архитектурой выполняет, например, команду чтения из памяти, воздействие (адрес и сигналы управления) с локальной L шины попадает на системную S шину, а только затем на шину памяти M. После этого данные, считанные из памяти, опять-таки попадают на системную шину, а с нее - на локальную. Очевидно, что каждый перенос информации через тот или иной буферный элемент сопровождается определенной задержкой. И пусть одна задержка невелика (не более 10 наносекунд), но суммарно их набирается довольно много, что и определяет ту довольно низкую тактовую частоту, на которой работали первые IBM PC - 12, или даже 8 Мгц.

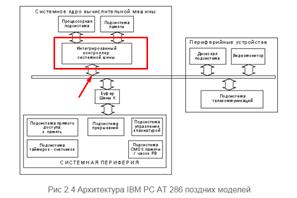

Для устранения таких потерь в более поздних моделях IBM PC AT 286 основная оперативная память выделяется в особую подсистему и доступ к ней осуществляется не через системную шину, а параллельно с доступом к системной шине. Как правило, это связано с наличием интегрированного контроллера шины данных. Суммарная задержка передачи данных в этом случае сокращается примерно до 20 нс, а тактовая частота повышается до 25 МГц.

Дальнейшее совершенствование систем в этом направлении привело к тому, что переход от шины данных LD локальной шины к шине MD шины памяти упростился до предела. Функцию контроллера шины данных в этом случае выполняет обычный шинный формирователь. На первый взгляд, в нем нет необходимости и можно было бы просто объединить шины LD и MD. Но по соображениям согласования электрических сигналов этого нельзя делать.

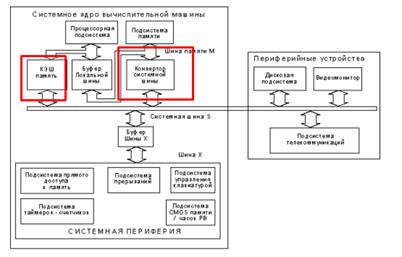

Дальнейшие возможности повышения производительности процессора связаны с поисками решений в области архитектуры РС АТ. Введение кэш- памяти позволило ослабить требования по времени доступа к основной оперативной памяти (кэш-память - это статическая память с малым временем доступа, которая не “видна” для программного обеспечения. Объем ее колеблется от 128Кбайт до 1 Мбайт). При этом на локальной шине, кроме микропроцессора и сопроцессора, появляется контроллер управления кэш- памятью.

21. Понятие архитектуры компьютера. Структура компьютера. Понятие о CISC и RISC.

Термин "архитектура системы" часто употребляется как в узком, так и в широком смысле этого слова.

· В узком смысле под архитектурой понимается архитектура набора команд. Архитектура набора команд служит границей между аппаратурой и программным обеспечением и представляет ту часть системы, которая видна программисту или разработчику компиляторов. Следует отметить, что это наиболее частое употребление этого термина.

· В широком смысле архитектура охватывает понятие организации системы, включающее такие высокоуровневые аспекты разработки компьютера как систему памяти, структуру системной шины, организацию ввода/вывода и т.п.

Применительно к вычислительным системам термин "архитектура" может быть определен как распределение функций, реализуемых системой, между ее уровнями, точнее как определение границ между этими уровнями. Таким образом, архитектура вычислительной системы предполагает многоуровневую организацию.

1) Архитектура первого уровня определяет, какие функции по обработке данных выполняются системой в целом, а какие возлагаются на внешний мир (пользователей, операторов, администраторов баз данных и т.д.).

Система взаимодействует с внешним миром через набор интерфейсов: языки (язык оператора, языки программирования, языки описания и манипулирования базой данных, язык управления заданиями) и системные программы (программы-утилиты, программы редактирования, сортировки, сохранения и восстановления информации).

2) Интерфейсы следующих уровней могут разграничивать определенные уровни внутри программного обеспечения.

- Например, уровень управления логическими ресурсами может включать реализацию таких функций, как управление базой данных, файлами, виртуальной памятью, сетевой телеобработкой. - К уровню управления физическими ресурсами относятся функции управления внешней и оперативной памятью, управления процессами, выполняющимися в системе.

3) Следующий уровень отражает основную линию разграничения системы, а именно границу между системным программным обеспечением и аппаратурой.

4) Эту идею можно развить и дальше и говорить о распределении функций между отдельными частями физической системы. Например, некоторый интерфейс определяет, какие функции реализуют центральные процессоры, а какие - процессоры ввода/вывода.

5) Архитектура следующего уровня определяет разграничение функций между процессорами ввода/вывода и контроллерами внешних устройств. В свою очередь можно разграничить функции, реализуемые контроллерами и самими устройствами ввода/вывода (терминалами, модемами, накопителями на магнитных дисках и лентах). Архитектура таких уровней часто называется архитектурой физического ввода/вывода.

Основоположником CISC-архитектуры можно считать компанию IBM

В конце 70-х годов все очень увлекались сложными наборами команд, разработчики хотели, чтобы процессор по максимуму умел все то, что нужно языкам высокого уровня.

CISC — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

· сравнительно небольшое число регистров общего назначения;

· большое количество машинных команд, некоторые из которых нагружены семантически аналогично операторам высокоуровневых языков программирования и выполняются за много тактов;

· большое количество методов адресации;

· большое количество форматов команд различной разрядности;

· преобладание двухадресного формата команд;

· наличие команд обработки типа регистр-память.

Типичными представителями являются процессоры на основе команд x86 (исключая современные Intel Pentium 4, Pentium D, Core, AMD Athlon, Phenom, которые являются гибридными) и процессорыMotorola MC680x0. Эти процессоры работали с упором на интерпретацию.

Недостатки CISC архитектуры:

· высокая стоимость аппаратной части;

· сложности с распараллеливанием вычислений.

В 80-х годах некоторым программистам это надоело, и они начали разработку других систем - RISC. Разработчики осознали, что количество запускаемых команд в секунду гораздо важнее скорости выполнения отдельной команды. В результате сконструировали компьютеры с ограниченным набором команд (50-100). Этим компьютерам для выполнения одной операции ЦИСК машины нужно сделать 4-5 маленьких операций, но они делают их так быстро, что в итоге все равно получалось быстрее.

RISC (англ. restricted (reduced) instruction set computer— компьютер с сокращённым набором команд) — архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Первые RISC-процессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Начались баталии.

Но РИСК архитектура не оказалась сильно распространенной изза-

· несовместимости (новые системы были совсем несовместимы со старыми)

· ИНТЕЛ быстро сообразили, что к чему и ввели элементы риск архитектуры в свои процессоры: внутри ЦИСК процессоров теперь есть РИСК ядро, которое выполняет самые простые и часто встречающиеся команды, а все остальное выполняется в ЦИСК режиме.

В итоге ИНТЕЛ рулит.