По последней цифре номера зачетной книжки (053402) выбран образующий полином:

Определим образующий полином по коду БЧХ:

тогда по формуле:

(6)

(6)

найдем h:

l – степень минимальных многочленов (столбец).

тогда разрешенный код БЧХ имеет вид:

е) построить схему кодера для выбранного g(x) и пояснить его работу.

Кодер и декодер построены на основе циклического кода.

Работа кодера на его выходе характеризуется следующими режимами:

1.Формирование k элементов информационной группы и одновременно деление полинома, отображающего информационную часть xrm(х), на порождающий (образующий) полином g(х) с целью получения остатка от деления r(х).

2. Формирование проверочных r элементов путем считывания их с ячеек схемы деления xr m(х) на выход кодера.

Цикл работы кодера для передачи n = 31 единичных элементов составляет n тактов. Тактовые сигналы формируются передающим распределителем, который на схеме не указан.

Первый режим работы кодера длится k = 20 тактов. От первого тактового импульса триггер Т занимает положение, при котором на его прямом выходе появляется сигнал "1", а на инверсном - сигнал "0". Сигналом "1" открываются ключи (логические схемы И) 1 и 3. Сигналом "0" ключ 2 закрыт. В таком состоянии триггер и ключи находятся k+1тактов, т.е. 21 тактов. За это время на выход кодера через открытый ключ 1 поступят 21 единичных элементов информационной группы k =20.

Одновременно через открытый ключ 3 информационные элементы поступают на устройство деления многочлена xr m(х) на g(х).

Деление осуществляется многотактным фильтром с числом ячеек, равным числу проверочных разрядов (степени порождающего полинома). В рассматриваемом случае число ячеек г=11. Число сумматоров в устройстве равно числу ненулевых членов g(х) минус единица. В нашем случае число сумматоров равно четырем. Сумматоры устанавливаются после ячеек, соответствующих ненулевым членам g(х). Поскольку все неприводимые полиномы имеют член х°=1, то соответствующий этому члену сумматор установлен перед ключом 3 (логической схемой И).

После k=20 тактов в ячейках устройства деления окажется записанным остаток от деления г(х).

При воздействии k+1= 21 тактового импульса триггер Т изменяет свое состояние: на инверсном выходе появляется сигнал "1", а на прямом - "0". Ключи 1 и 3 закрываются, а ключ 2 открывается. За оставшиеся r=13 тактов элементы остатка от деления (проверочная группа) через ключ 2 поступают на выход кодера, также начиная со старшего разряда.

Рисунок 3 – Структурная схема кодера

ж) построить схему декодера для выбранного g(x) и пояснить его работу.

Функционирование схемы декодера сводится к следующему. Принятая кодовая комбинация, которая отображается полиномом Р(х) поступает в декодирующий регистр и одновременно в ячейки буферного регистра, который содержит k ячеек. Ячейки буферного регистра связаны через логические схемы "нет", пропускающие сигналы только при наличии "1" на первом входе и "0" - на втором (этот вход отмечен кружочком). На вход буферного регистра кодовая комбинация поступит через схему И1. Этот ключ открывается с выхода триггера Т первым тактовым импульсом и закрывается k+1 тактовым импульсом (полностью аналогично работе триггера Т в схеме кодера). Таким образом, после k=20 тактов информационная группа элементов будет записана в буферный регистр. Схемы НЕТ в режиме заполнения регистра открыты, ибо на вторые входы напряжение со стороны ключа И2 не поступает.

Одновременно в декодирующем регистре происходит в продолжение всех n=31 тактов деление кодовой комбинации (полином Р(х) на порождающий полином g(х)). Схема декодирующего регистра полностью аналогична схеме деления кодера, которая подробно рассматривалась выше. Если в результате деления получится нулевой остаток - синдром S(х) = 0, то последующие тактовые импульсы спишут информационные элементы на выход декодера.

При наличии ошибок в принятой комбинации синдром S(х) не равен 0. Это означает, что после n - го (31) такта хотя бы в одной ячейке декодирующего регистра будет записана “1”.Тогда на выходе схемы ИЛИ появится сигнал. Ключ 2 (схема И2) сработает, схемы НЕТ буферного регистра закроются, а очередной тактовый импульс переведет все ячейки регистра в состояние "0". Неправильно принятая информация будет стерта. Одновременно сигнал стирания используется как команда на блокировку приемника и переспрос.

Рисунок 4 - Структурная схема декодера

з) получить схему кодирующего и декодирующего устройства циклического кода с модуляцией и демодуляцией данного варианта, а также собрать схему с применением пакета «System View».

Модуляция – это процесс изменения одного или нескольких параметров несущей в соответствии с изменением параметров модулирующего сигнала. При амплитудной модуляции амплитуда несущего колебания изменяется пропорционально мгновенным значениям модулирующего сигнала. Амплитуда называется информационным параметром при АМ, частота – при ЧМ, фаза – при ФМ.

Главная особенность любой модуляции – преобразование спектра модулирующего сигнала. При гармонической несущей происходит перенос спектра в область около частоты несущей.

Модуляцию, отвечающую соотношению  , называют фазовой модуляцией (ФМ).

, называют фазовой модуляцией (ФМ).

Аналитическое выражение ФМК:

, где

, где  ;

;

Рисунок 5 – График ФМК

При прочих равных условиях спектр колебания со сложной угловой модуляцией гораздо богаче спектра аналогичного АМ-сигнала.

Кодер циклического кода

Рисунок 6 - Структурная схема кодера на SystemView

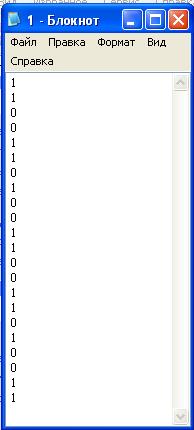

Рисунок 7 – Выход кодера

Рисунок 8 – Вход кодера

Рисунок 9 – Сигнал управления

Декодер циклического кода

Рисунок 10 - Структурная схема декодера на SystemView

Рисунок 11 - Вход декодера

Рисунок 12 – Внесение ошибки

Рисунок 13 – Выход декодера

Рисунок 14 – Входные данные

и) определить объем передаваемой информации W при заданном темпе TПЕР и критерии отказа tОТК.

Объем передаваемой информации W определяется формулой:

(7)

(7)

откуда:

бит

бит

к) определить емкость накопителя М.

Емкость накопителя определяется по формуле:

(8)

(8)

где  - время распространения сигнала по каналу связи, с;

- время распространения сигнала по каналу связи, с;

- длительность кодовой комбинации из n разрядов, с.

- длительность кодовой комбинации из n разрядов, с.

Откуда:

л) рассчитать надежностные показатели основного и обходного каналов ПД

Для прямого канала:

Максимальная скорость работы по каналу:

Бод;

Бод;

Распределение вероятности возникновения хотя бы одной ошибки на длине n:

, где

, где  - показатель группирования ошибок.

- показатель группирования ошибок.

.

.

Распределение вероятности возникновения ошибок, кратностью t и более, на длине n, вероятностью P:

;

;

Для

,

,

для

.

.

Для обратного канала:

Максимальная скорость работы по каналу:

Бод;

Бод;

Распределение вероятности возникновения хотя бы одной ошибки на длине n:

, где

, где  - показатель группирования ошибок.

- показатель группирования ошибок.

.

.

Распределение вероятности возникновения ошибок, кратностью t и более, на длине n, вероятностью P:

;

;

Для

,

,

для

.

.

Для прямого и обратного канала:

1. Избыточность кода:

(9)

(9)

2. Скорость кода:

(10)

(10)

3. Вероятность необнаруживаемой кодом ошибки:

(11)

(11)

4. Вероятность обнаруживаемой кодом ошибки:

(12)

(12)

5. Средняя относительная скорость передачи в РОСнпбл:

(13)

(13)

(14)

(14)

(15)

(15)

- по прямому каналу;

- по прямому каналу;

- по обратному каналу;

- по обратному каналу;

- по прямому каналу;

- по прямому каналу;

- по обратному каналу;

- по обратному каналу;

- анализ прямого канала;

- анализ прямого канала;

;

;

(с) – для прямого канала;

(с) – для прямого канала;

(16)

(16)

Для прямого канала:

;

;

(бит/с).

(бит/с).

Для обратного канала:

(с) – для обратного канала;

(с) – для обратного канала;

;

;

(бит/с).

(бит/с).

Вероятность правильного приема

.

.

Избыточность, необходимая для обеспечения заданной вероятности необнаруживающего кодом ошибки в дискретном канале.

(бит) – для прямого канала;

(бит) – для прямого канала;

(бит) – для обратного канала.

(бит) – для обратного канала.

м) По географической карте РК выбираем два пункта, отстоящие на 5500 км, затем разбиваем ее на ряд участков длинной 500 – 1000 км. Пункты переприема привязываем к крупным населенным пунктам.

1. Алматы - 0 км.

2. Алматы - Усть-Каменогорск - 885,5 км

3. Усть-Каменогорск – Астана - 787,5 км

4. Астана – Костанай – 560 км

5. Костанай – Кызылорда – 910 км

6. Кызылорда – Актобе - 847 км

7. Актобе – Уральск – 500,5 км

8. Уральск – Атырау – 509,5 км

9. Атырау – Уральск – 500 км

н) построить временную диаграмму работы системы.

Рисунок 15 – Временная диаграмма работы системы (h=4)

- по прямому каналу;

- по прямому каналу;

- по обратному каналу;

- по обратному каналу;

- по прямому каналу;

- по прямому каналу;

- по обратному каналу;

- по обратному каналу;

- анализ прямого канала;

- анализ прямого канала;

;

;

ЗАКЛЮЧЕНИЕ

Курсовой проект посвящен проектированию тракта передачи данных между источником информации и получателем информации.

В результате выполнения курсовой работы я более подробно ознакомилась с построением систем передачи и обработки цифровых сигналов, аппаратным и программным методами повышения помехоустойчивости и скорости передачи цифровых систем связи, методами повышения эффективного использования каналов связи. Так же приобрела навыки расчетов основных функциональных узлов, и научилась осуществлять анализ влияния внешних факторов на работоспособность средств связи, и применения средств компьютерной техники для расчетов и проектирования программно-аппаратных средств связи.

В ходе работы были выявлены некоторые особенности построения тракта передачи данных. Они заключаются в следующем - пропускная способность тракта должна быть максимальной. Длина кодовой комбинации должна быть оптимальной вследствие обеспечения необходимой емкости накопителя. (M > h).

СПИСОК ЛИТЕРАТУРЫ

1 Скляр Б. Цифровая связь. Теоретические основы и практическое применение: 2-е изд. /Пер. с англ.- М.: Издательский дом «Вильямс», 2003. - 1104 с.

2 Прокис Дж. Цифровая связь. Радио и связь, 2000.-797с.

3 Сергиенко А.Б. Цифровая обработка сигналов: Учебник для вузов. - М.:-2002.

4 Фирменный стандарт. Работы учебные. Общие требования к построению, изложению, оформлению и содержанию. ФС РК 10352-1910-У-е-001-2002. – Алматы: АИЭС, 2002.

5 1 Шварцман В.О., Емельянов Г.А. Теория передачи дискретной информации. – М.: Связь, 1979. - 424 с.

6 Передача дискретных сообщений / Под ред. В. П. Шувалова. - М.: Радио и связь, 1990. - 464 с.

7 Емельянов Г. А., Шварцман В. О. Передача дискретной информации. - М.: Радио и связь, 1982. - 240 с.

8 Пуртов Л.П. и др. Элементы теории передачи дискретной информации. – М.: Связь, 1972. – 232 с.

9 Колесник В.Д., Мирончиков Е.Т.. Декодирование циклических кодов.- М.: Связь, 1968.