8.1.1. Ќазначение, параметры и классификаци€ микропроцессоров

ћикропроцессором называетс€ программно-управл€емое устройство дл€ обработки цифровой информации и управлени€ процессом обработки, реализованное в виде большой (Ѕ»—) или сверхбольшой (—Ѕ»—) интегральной микросхемы.

ћикро≠процессор обрабатывает информацию в компьютерах, системах управлени€ объектами и процессами, в информационно-измерительных системах, используемых в промышленности, бытовой технике, аппаратуре св€зи и многих других област€х применени€.

ћикропроцессор описываетс€ множеством параметров, присущих как электронным приборам: быстродействие, потребл€ема€ мощность, габариты и масса, количество уровней питани€, надежность, стоимость, тип корпуса, температурный диапазон и др., так и вычислительным средствам: разр€дность, цикл выполнени€ команд или микрокоманд, число внутренних регистров, наличие микропрограммного управлени€, тип стековой пам€ти, состав программного обеспечени€ и др.

ћикропроцессорный комплект (ћѕ ) содержит набор Ѕ»— дл€ построени€ микропроцессорных систем, в который вход€т микросхемы центрального процессора, микросхемы дл€ организации св€зи с внешними устройствами, тактовый генератор и др.

ѕо числу Ѕ»— в микропроцессорном комплекте различают однокристальные, многокристальные (логическа€ структура процессора разделена на функционально законченные части) и многокристальные секционные ћѕ.

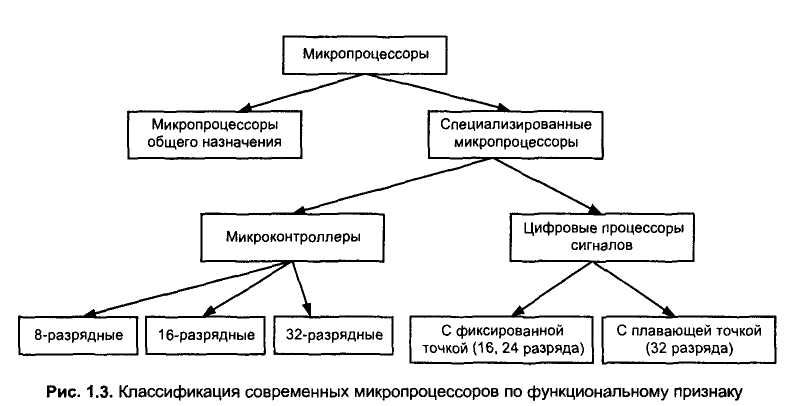

ѕо функциональному признаку выдел€ютс€ два класса: микропроцессоры общего назначени€ и специализированные микропроцессоры (рисунок 8.1.1.1).

–исунок 8.1.1.1. лассификаци€ ћѕ

ћикропроцессоры общего назначени€ предназначены дл€ решени€ широкого круга задач обработки разнообразной информации. »х основной областью использовани€ €вл€ютс€ персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применени€.

—реди специализированных микропроцессоров наиболее широкое распространение получили микроконтроллеры, предназначенные дл€ выполнени€ функций управлени€ различными объектами. ’арактерной особенностью структуры микроконтроллеров €вл€етс€ размещение на одном кристалле с центральным процессором внутренней пам€ти и большого набора периферийных устройств. ¬ состав периферийных устройств обычно вход€т несколько 8-разр€дных параллельных портов ввода-вывода данных (от 1 до 8), один или два последовательных порта, таймерный блок, аналого-цифровой преобразователь. ћикроконтроллеры прин€то подраздел€ть на 8-, 16- и 32-разр€дные. ќсновными област€ми применени€ 8-разр€дных микроконтроллеров €вл€ютс€ бытова€ и измерительна€ техника, промышленна€ автоматика, автомобильна€ электроника, теле-, видео- и аудиоаппаратура, средства св€зи. ќсновна€ сфера применени€ 16 - разр€дных микроконтроллеров - сложна€ промышленна€ автоматика, телекоммуникационна€ аппаратура, медицинска€ и измерительна€ техника. ћикроконтроллеры, обрабатывающие 32 разр€дные данные наход€т широкое применение в системах управлени€ сложными объектами промышленной автоматики (двигатели, робототехнические устройства, средства комплексной автоматизации производства), в контрольно-измерительной аппаратуре и телекоммуникационном оборудовании

|

|

|

÷ифровые процессоры сигналов (DSP Ц Digital Signal Processor) ориентированы на реализацию процедур, обеспечивающих необходимое преобразование аналоговых сигналов, представленных в цифровой форме (в виде последовательности числовых значений). —пецифической особенностью алгоритмов обработки аналоговых сигналов €вл€етс€ необходимость последовательного выполнени€ р€да команд умножени€-сложени€ с накоплением промежуточного результата в регистре-аккумул€торе. ѕоэтому архитектура ÷ѕ— ориентирована на реализацию быстрого выполнени€ операций такого рода. Ќабор команд этих процессоров содержит специальные команды MAC (Multiplication with Accumlation), реализующие эти операции.

ѕо виду обрабатываемых входных сигналов различают аналоговые и цифровые ћѕ.

ѕо разр€дности различают ћѕ с фиксированной и с измен€емой разр€дностью слова.

ѕо характеру временной организации работы ћѕ дел€т на синхронные и асинхронные.

ѕо количеству выполн€емых программ различают однопрограммные и мультипрограммные ћѕ.

ѕо способу управлени€ ћѕ подраздел€ютс€ на микропрограммируемые и с жестким управлением.

ќсновными направлени€ми развити€ микропроцессоров €вл€етс€ увеличение их производительности и расширение функциональных возможностей, что достигаетс€ как повышением уровн€ микроэлектронной технологии, используемой дл€ производства микропроцессоров, так и применением новых архитектурных и структурных вариантов их реализации. –азвитие микроэлектронной технологии обеспечивает непрерывное уменьшение размеров полупроводниковых компонентов, размещаемых на кристалле микропроцессора. ѕри этом уменьшаютс€ паразитные емкости, определ€ющие задержку переключени€ логических элементов, и увеличиваетс€ число элементов, размещаемых на кристалле. ¬ насто€щее врем€ разрешающа€ способность промышленной технологии изготовлени€ микросхем обеспечивает создание компонентов с минимальными размерами 0,13 Ц 0,18 мкм. ѕри этом обеспечиваетс€ создание микропроцессоров, работающих с тактовой частотой до 1 Ц 2 √√ц и содержащих на кристалле дес€тки миллионов транзисторов

8.1.2. ќсновные варианты архитектуры и структуры микропроцессоров

јрхитектурой процессора называетс€ комплекс его аппаратных и программных средств, предоставл€емых пользователю. ¬ это общее пон€тие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой пам€ти, виды и способы обработки прерываний.

—труктура микропроцессора определ€ет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. ¬ эту структуру вход€т:

Ј центральный процессор (процессорное €дро), состо€щее из устройства управлени€ (””), одного или нескольких операционных устройств (ќ”);

Ј внутренн€€ пам€ть (–«”, кэш-пам€ть, блоки оперативной и посто€нной пам€ти);

Ј интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода/вывода;

Ј периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры);

Ј различные вспомогательные схемы (генератор тактовых импульсов, схемы дл€ выполнени€ отладки и тестировани€, сторожевой таймер и р€д других).

|

|

|

јрхитектура и структура микропроцессора тесно взаимосв€заны. –еализаци€ тех или иных архитектурных особенностей требует введени€ в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечени€ соответствующих механизмов их совместного функционировани€.

¬ современных микропроцессорах реализуютс€ следующие варианты архитектур.

ѕо набору выполн€емых команд и способов адресации различают CISC и RISC архитектуры.

CISC (Complex Instruction Set Computer) - архитектура реализована во многих типах микропроцессоров, выполн€ющих большой набор разноформатных команд с использованием многочисленных способов адресации. ѕримером CISC-процессоров €вл€ютс€ микропроцессоры семейства Pentium. ќни выполн€ют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. “акое большое многообразие выполн€емых команд и способов адресации позвол€ет программисту реализовать наиболее эффективные алгоритмы решени€ различных задач. ќднако при этом существенно усложн€етс€ структура микропроцессора, особенно его устройства управлени€, что приводит к увеличению размеров и стоимости кристалла, снижению производительности.

RISC (Reduced Instruction Set Computer) Ц архитектура отличаетс€ использованием ограниченного набора команд фиксированного формата. —овременные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. “акже значительно сокращаетс€ число используемых способов адресации. ќбычно в RISC-процессорах все команды обработки данных выполн€ютс€ только с регистровой или непосредственной адресацией. ѕри этом дл€ сокращени€ количества обращений к пам€ти RISC-процессоры имеют увеличенный объем внутреннего –«”- от 32 до нескольких сотен регистров, тогда как в CISC-процессорах число регистров общего назначени€ обычно составл€ет 8-16.

ѕо способу реализации пам€ти и организации

выборки команд и данных различаютс€ процессоры с ѕринстонской и √арвардской архитектурой.

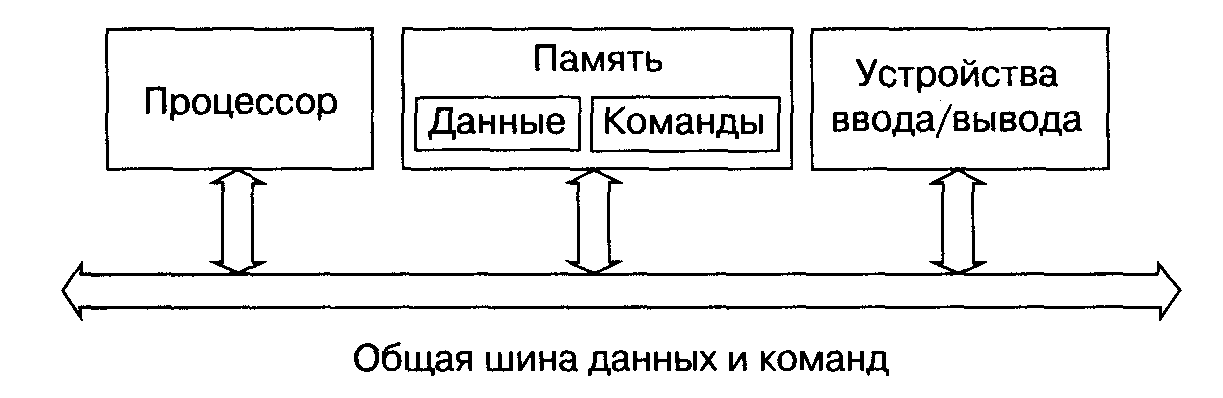

ѕринстонска€ архитектура (архитектура ‘он-Ќеймана) представлена на рисунке 8.1.2.1.

–исунок 8.1.2.1. ѕринстонска€ архитектура

ѕринстонска€ архитектура характеризуетс€ использованием общей оперативной пам€ти дл€ хранени€ программ, данных, а также дл€ организации стека. ƒл€ обращени€ к этой пам€ти используетс€ обща€ системна€ шина, по которой в процессор поступают и команды, и данные. Ёта архитектура имеет р€д важных достоинств. Ќаличие общей пам€ти позвол€ет оперативно перераспредел€ть ее объем дл€ хранени€ отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач. “аким образом, обеспечиваетс€ возможность более эффективного использовани€ имеющегос€ объема оперативной пам€ти в каждом конкретном случае применени€ микропроцессора. »спользование общей шины дл€ передачи команд и данных значительно упрощает отладку, тестирование и текущий контроль функционировани€ системы, повышает ее надежность. ќднако ей присущи и существенные недостатки. ќсновным из них €вл€етс€ необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. ѕри этом обща€ шина становитс€ Ђузким местомї (bottleneck - Ђбутылочное горлої), которое ограничивает производительность цифровой системы.

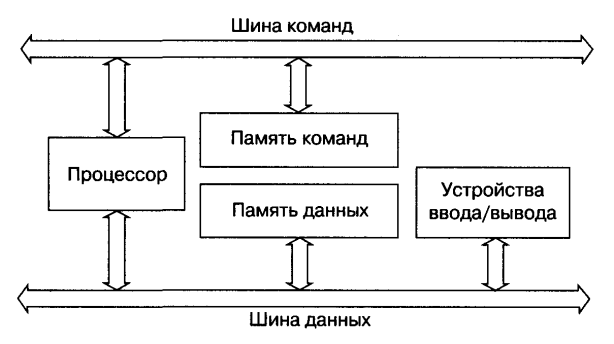

√арвардска€ архитектура представлена на рисунке 8.1.2.2.

–исунок 8.1.2.2. √арвардска€ архитектура

√арвардска€ архитектура характеризуетс€ физическим разделением пам€ти команд (программ) и пам€ти данных. ¬ ее оригинальном варианте использовалс€ также отдельный стек дл€ хранени€ содержимого программного счетчика, который обеспечивал возможности выполнени€ вложенных подпрограмм. ажда€ пам€ть соедин€етс€ с процессором отдельной шиной, что позвол€ет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Ѕлагодар€ такому разделению потоков команд и данных и совмещению операций их выборки реализуетс€ более высока€ производительность, чем при использовании ѕринстонской архитектуры. Ќедостатки √арвардской архитектуры св€заны с необходимостью проведени€ большего числа шин, а также с фиксированным объемом пам€ти, выделенной дл€ команд и данных, назначение которой не может оперативно перераспредел€тьс€ в соответствии с требовани€ми решаемой задачи. ѕоэтому приходитс€ использовать пам€ть большего объема, коэффициент использовани€ которой при решении разнообразных задач оказываетс€ более низким, чем в системах с ѕринстонской архитектурой. ќднако развитие микроэлектронной тех≠нологии позволило в значительной степени преодолеть указанные недостатки, поэтому √арвардска€ архитектура широко примен€етс€ во внутренней структуре современных высокопроизводительных микропроцессоров, а во внешней структуре большинства микропроцессорных систем реализуютс€ принципы ѕринстонской архитектуры.

|

|

|

8.1.3 ќрганизаци€ конвейера команд

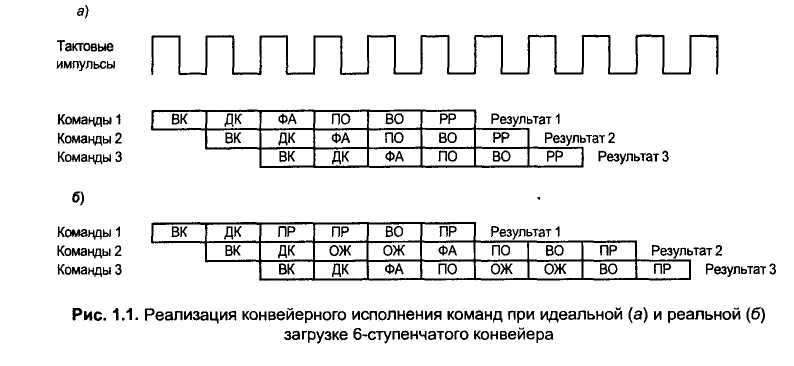

¬о внутренней структуре современных высокопроизводительных микропроцессоров реализуетс€ конвейерный принцип выполнени€ команд. ѕри этом процесс выполнени€ команды разбиваетс€ на р€д этапов. Ќа рисунке 3.1.3.1 а) приведен пример разбиени€ команды на шесть этапов ее выполнени€:

1) выборка очередной команды (¬ );

2) декодирование выбранной команды (ƒ );

3) формирование адреса операнда (‘ј);

4) прием операнда из пам€ти (ѕќ);

5) выполнение операции (¬ќ);

6) размещение результата в пам€ти (––).

–еализаци€ каждого этапа занимает один такт машинного времени и производитс€ устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполн€етс€ соответствующа€ микроопераци€. ѕри последовательной загрузке в конвейер выбираемых команд кажда€ его ступень реализует определенный этап выполнени€ очередной команды. “аким образом, в конвейере одновременно наход€тс€ несколько команд, наход€щихс€ на разных этапах выполнени€. ¬ идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнени€ очередной команды (рисунок 8.1.3.1 а) ¬ этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с).

ќднако така€ эффективна€ работа конвейера обеспечиваетс€ только при его равномерной загрузке однотипными командами. –еально отдельные ступени конвейера могут оказатьс€ незагруженными, наход€сь в состо€нии ожидани€ или просто€.

–исунок 8.1.3.1 –азбиение команды на шесть этапов ее выполнени€

Ќа рисунке 8.1.3.1 б) показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываютс€ в состо€нии ожидани€ (ќ∆) или просто€ (ѕ–).

Ќаибольша€ эффективность использовани€ конвейера обеспечиваетс€ при поступлении однородных команд. ѕричиной снижени€ эффективности конвейера €вл€ютс€ команды условного ветвлени€. ≈сли выполн€етс€ условие ветвлени€, то приходитс€ производить перезагрузку конвейера командами из другой ветви программы, что требует выполнени€ дополнительных рабочих тактов и вызывает значительное снижение производительности.

¬ современных высокопроизводительных микропроцессорах эффективность конвейера обеспечиваетс€ увеличением числа его ступеней (достигает 10 и более), а также сокращением числа его перезагрузок при выполнении условных переходов с помощью реализации механизмов предсказани€ направлени€ ветвлени€.

8.1.4 —труктурна€ схема ћѕ—

Ѕольшинство микропроцессорных систем имеет магистрально-модульную структуру (рисунок 8.1.4.1), в которой отдельные устройства (модули), вход€щие в состав системы, обмениваютс€ информацией по общей системной шине - магистрали.

|

|

|

–исунок 8.1.4.1 “ипова€ структура ћѕ—

ќсновным модулем системы €вл€етс€ микропроцессор, который содержит устройство управлени€ (””), операционное устройство (ќ”) и регистровое запоминающее устройство (–«”) - внутреннюю пам€ть, реализованную в виде набора регистров. ќперативное запоминающее устройство (ќ«”) служит дл€ хранени€ выполн€емой программы (или ее фрагментов) и данных, подлежащих обработке. “ак как обращение к ќ«” по системной шине требует значительных затрат времени, в большинстве современных высокопроизводительных микропроцессоров дополнительно вводитс€ быстродействующа€ промежуточна€ пам€ть (кэш-пам€ть) ограниченного объема (от нескольких байт до сотен байт).

ѕосто€нное запоминающее устройство (ѕ«”) служит дл€ хранени€ констант и стандартных (неизмен€емых) программ. ¬ ѕ«” обычно записываютс€ программы начальной инициализации (загрузки) систем, тестовые и диагностические программы и другое служебное программное обеспечение. ¬ микропроцессорных системах, управл€ющих определенными объектами с использованием фиксированных или редко измен€емых программ, дл€ их хранени€ также обычно используетс€ ѕ«” (пам€ть ROM - Read-Only Memory) или репрограммируемое ѕ«” (пам€ть EEPROM - Electrically Erased Programmable Read-Only Memory или флэш-пам€ть).

ќстальные устройства €вл€ютс€ внешними и подключаютс€ к системе с помощью интерфейсных устройств (»”), реализующих определенные протоколы параллельного или последовательного обмена. “акими внешними устройствами могут быть клавиатура, монитор, внешние запоминающие устройства (¬«”), использующие гибкие или жесткие магнитные диски, оптические диски (CD-ROM), магнитные ленты и другие виды носителей информации, датчики и преобразователи информации (аналого-цифровые или цифроаналоговые), разнообразные исполнительные устройства (индикаторы, принтеры, электродвигатели, реле и другие). ƒл€ реализации различных режимов работы к системе могут подключатьс€ дополнительные устройства - контроллеры прерываний, пр€мого доступа к пам€ти и другие, реализующие необходимые специальные функции управлени€.

ƒанна€ структура соответствует архитектуре ‘он-Ќеймана.

—истемна€ шина содержит несколько дес€тков (в сложных системах более 100) проводников, которые в соответствии с их функциональным назначением подраздел€ютс€ на отдельные шины - адреса ј, данных D и управлени€ —.

Ўина ј служит дл€ передачи адреса, который формируетс€ микропроцессором и позвол€ет выбрать необходимую €чейку пам€ти ќ«” (ѕ«”) или требуемое »” при обращении к внешнему устройству. –азр€дность шины адреса определ€ет максимальный объем адресуемой процессором внешней пам€ти. Ќапример, 32-разр€дна€ шина ј обеспечивает адресацию пам€ти объемом до 4 √байт. ¬о многих микропроцессорных системах передача адреса и данных сопровождаетс€ посылкой контрольных битов четности, которые обеспечивают вы€вление возможных ошибок, возникающих в процессе обмена.

Ўина D служит дл€ выборки команд, поступающих из ќ«” или ѕ«” в ”” микропроцессора, и дл€ пересылки обрабатываемых данных (операндов) между микропроцессором и ќ«” или »” (внешним устройством). –азр€дность шины данных обычно соответствует разр€дности операндов, обрабатываемых микропроцессором. ѕоэтому чаще всего шина D содержит 8, 16 или 32 линии.

¬ некоторых системах дл€ уменьшени€ числа необходимых линий св€зи и соответствующих выводов и контактов используетс€ мультиплексирование линий адреса и данных. ¬ таких системах дл€ передачи адреса и данных используютс€ одни и те же линии св€зи, на которые сначала выдаетс€ адрес, а затем поступают данные.

ѕо шине — передаютс€ разнообразные управл€ющие сигналы, определ€ющие режимы работы пам€ти (запись или считывание), интерфейсных устройств (ввод или вывод информации) и микропроцессора (запуск, запросы внешних устройств на обслуживание, информаци€ о текущем режиме работы и другие сигналы). –азр€дность шины управлени€ — определ€етс€ организацией работы системы, возможност€ми реализации различных режимов ее функционировани€, используемыми методами контрол€ микропроцессора и других устройств. ѕоэтому набор передаваемых по шине — управл€ющих сигналов €вл€етс€ индивидуальным дл€ каждой модели микропроцессора. »меетс€ р€д управл€ющих сигналов, которые используютс€ в большинстве микропроцессорных систем. ним относ€тс€ сигналы начального запуска (RESET), сигналы, задающие режим работы пам€ти (чтение - RD, запись - WR), сигналы, необходимые дл€ реализации прерываний и р€д других.

8.1.5 ‘ункционирование ћѕ— при выполнении основной программы. ѕроцедура выполнени€ команд. –абочий цикл микропроцессора.

¬ процессе функционировани€ микропроцессорной системы реализуютс€ следующие основные режимы ее работы:

|

|

|

Х выполнение основной программы;

Х вызов подпрограммы;

Х обслуживание прерываний и исключений;

Х пр€мой доступ к пам€ти.

—труктура команд. оманды микропроцессора могут быть безадресными, одноадресными и двух≠адресными.

Ѕезадресными €вл€ютс€ команды, дл€ выполнени€ которых не требуетс€ операнд (например, команда останова HALT) или размещение операнда определ€етс€ структурой микропроцессора и задаетс€ непосредственно кодом операции. Ќапример, в микропроцессорах, использующих регистр-аккумул€тор, выполнение р€да команд над одним операндом предполагает, что он размещаетс€ в этом регистре.

ќдноадресные команды содержат адрес одного операнда. Ёти команды используютс€ дл€ выполнени€ операций над одним операндом, например, сдвигов, логической инверсии, изменени€ знака и р€да других. ¬ микропроцессорах с аккумул€торной организацией обработки данных такие команды служат также дл€ выполнени€ операций над двум€ операндами, один из которых находитс€ в аккумул€торе.

¬ двухадресных командах содержатс€ адреса двух операндов. ≈сли при этом один из операндов выбираетс€ из пам€ти, то другой операнд хранитс€ в регистре (регистрова€ адресаци€) или содержитс€ непосредственно в команде (непосредственна€ адресаци€) –езультат операции записываетс€ на место одного из операндов, значение которого при этом тер€етс€.

—ледует отметить, что в некоторых типах микропроцессоров реализуютс€ также трехадресные команды, где задаютс€ отдельные адреса размещени€ двух операндов и результата операции. “акие команды используют только регистровую адресацию и выполн€ютс€ в микропроцессорах с RISC-архитектурой, имеющих значительный объем –«”, например, в PowerPC.

¬ыполнение основной программы. ¬ этом режиме процессор выбирает из ќ«” очередную команду программы и выполн€ет соответствующую операцию. оманда представл€ет собой многоразр€дное двоичное число (рисунок 8.1.5.1), которое состоит из двух частей (полей) Ц кода операции ( ќѕ) и кода адресации операндов ( јƒ).

| од операции ( ќѕ) | од адресации операнда ( јƒ) |

–исунок 8.1.5.1. ‘ормат типовой команды микропроцессора.

од операции ќѕ задает вид операции, выполн€емой данной командой, а код адресации јƒ определ€ет выбор операндов (способ адресации), над которыми производитс€ заданна€ операци€.

ƒл€ хранени€ адреса очередной команды служит специальный регистр процессора - программный счетчик PC (Program Counter), содержимое которого автоматически увели≠чиваетс€ на 1 после выборки следующего байта команды. “аким образом, обеспечиваетс€ последовательна€ выборка команд в процессе выполнени€ программы. ѕри выборке очередной команды содержимое PC поступает на шину адреса, обеспечива€ считывание из ќ«” следующей команды выполн€емой программы. ѕри реализации ветвлений или других изменений последовательности выполнени€ команд выполн€етс€ загрузка в PC нового содержимого, в результате чего производитс€ переход к другой ветви программы или подпрограмме.

ѕрин€та€ из ќ«” команда поступает в регистр команд, вход€щий в состав ”” процессора. «атем производитс€ дешифраци€ команды, в процессе которой определ€етс€ вид выполн€емой операции (расшифровка ќѕ) и формируетс€ адрес необходимых операндов (расшифровка јƒ). ¬ соответствии с кодом поступившей команды ”” процессора генерирует последовательность микрокоманд, обеспечивающих выполнение заданной операции.

–абочий цикл микропроцессора. ажда€ микрокоманда выполн€етс€ в течение одного машинного такта - периода тактовых импульсов, задающих рабочую частоту всех внутренних узлов и блоков микропроцессора. “аким образом, тактова€ частота микропроцессора (1√√ц и более) определ€ет врем€ выполнени€ отдельных микрокоманд, последовательность которых обеспечивает получение необходимого результата операции (поступившей команды).

ѕри выполнении команды может потребоватьс€ обращение к ќ«” или внешнему устройству. ƒл€ выполнени€ такой команды требуетс€ определенное количество командных циклов и тактов. омандным циклом называетс€ промежуток времени, требуемый дл€ выполнени€ обращени€ к ќ«” или внешнему устройству с помощью системной шины. ќбычно реализаци€ такого цикла занимает от 2 до 4 системных тактов (периодов синхросигналов шины), которые требуютс€ дл€:

Ц установки требуемого адреса,

Ц выдачи сигналов, определ€ющих вид цикла - чтение или запись,

Ц получени€ сигнала готовности к обмену (от пам€ти или внешних устройств),

Ц собственно передачи данных или команд.

ѕри современной технологии изготовлени€ системных плат частота синхросигналов шины обычно составл€ет дес€тки мегагерц (типичные значени€ 25, 33, 50, 66, 75, 100, 133 ћ√ц).

“аким образом, при выполнении каждой команды в первых циклах производитс€ ее выборка из ќ«”, а последующа€ дешифраци€ команды определ€ет необходимое число циклов дл€ ее выполнени€ (если дл€ выполнени€ команды не требуетс€ обращение к пам€ти или ”¬¬, то така€ команда выполн€етс€ за один цикл, если требуетс€ обращение к пам€ти или ”¬¬ то потребуютс€ дополнительные циклы чтени€ (ввода) или записи (вывода).

»зЦза различного быстродействи€ ћѕ и системной шины в ћѕ— включаетс€ промежуточна€ буферна€ пам€ть, в которой хран€тс€ данные, посылаемые микропроцессором на системную шину.

“екущее состо€ние процессора при выполнении программы определ€етс€ содержимым регистра состо€ни€ SR (State Register), в микропроцессорах Pentium данный регистр называетс€ EFLAGS). Ётот регистр содержит биты управлени€, задающие режим работы процессора, и биты признаков (флаги), указывающие характеристики результата выполненной операции:

N Ц признак знака (старший бит результата), N = 0 - при положительном результате, N = 1 -при отрицательном результате;

— Ц признак перенос, — = 1, если при выполнении операции образовалс€ перенос из старшего разр€да результата;

V Ц признак переполнени€, V = 1, если при выполнении операций над числами со знаком произошло переполнение разр€дной сетки процессора;

Z Ц признак нул€, Z = 1, если результат операции равен нулю;

P Ц признак четности результата и др.

8.1.6 ‘ункционирование ћѕ— при выполнении подпрограммы

ќбращение к подпрограмме реализуетс€ при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR Ц Jump-to-SubRoutine), котора€ указывает адрес первой команды вызываемой подпрограммы. Ётот адрес загружаетс€ в PC, обеспечива€ в следующем командном цикле выборку первой команды подпрограммы. ѕредварительно выполн€етс€ процедура сохранени€ в специальном регистре или €чейке пам€ти текущего содержимого PC, где хранитс€ адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнени€ подпрограммы. ¬озврат к основной программе реализуетс€ при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. ѕо этой команде сохран€вшеес€ содержимое PC снова загружаетс€ в программный счетчик, обеспечива€ выполнение команды, котора€ в исходной программе следовала за командой CALL.

ќсобенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложени€ подпрограмм, т. е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (рисунок8.1.6.1). ѕри вложении нескольких подпрограмм требуетс€ сохранение несколь≠ких промежуточных значений содержимого PC и последовательна€ загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

ƒл€ реализации этой процедуры используетс€ стек Ц специальна€ пам€ть магазинно≠го типа, работающа€ по принципу Ђпоследний пришел Ц первый ушелї (стек типа LIFO Ц ЂLast In-First Outї). —уществуют различные варианты реализации стека.

–исунок8.1.6.1 ќрганизаци€ вложенных подпрограмм

–егистровый стек (рисунок8.1.6.2, а) реализуетс€ с помощью реверсивных сдвиговых регистров. ажда€ команда CALL вызывает ввод в стек очередного содержимого PC. ѕо команде RETURN направление сдвига измен€етс€ и производитс€ извлечение из стека последнего поступившего содержимого PC. “аким образом, обеспечиваетс€ выполнение вложенных подпрограмм. ¬озможное число вложенных подпрограмм определ€етс€ глубиной стека, т. е. разр€дностью используемых регистров сдвига. ≈сли число вложений превышает глубину стека, первые из введенных в стек значений PC тер€ютс€, т. е. возврат к основной программе не будет обеспечен. ѕоэтому при использовании регистрового стека необходим строгий контроль за числом вложений. “ака€ реализаци€ стека примен€етс€ в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20).

«начительно более широкие возможности вложени€ подпрограмм обеспечивает реализаци€ стека в ќ«” (рисунок8.1.6.2, б). ¬ этом случае часть ќ«” выдел€етс€ дл€ работы в качестве стека. јдресаци€ к €чейкам стека производитс€ с помощью специального регистра Ц указател€ стека SP (Stack Pointer), который вводитс€ в состав ”” процессора. –егистр SP содержит адрес верхней заполненной €чейки стека, в которой хранитс€ значение PC, записанное при выполнении команды CALL. ѕри поступлении новой команды CALL содержимое SP ав≠оматически уменьшаетс€ на 1, адресу€ следующую, еще незаполненную €чейку стека ѕолученный адрес SP-1 выдаетс€ на шину ј, а на шину D поступает содержимое PC, которое должно сохран€тьс€ в стеке. “аким образом, производитс€ последовательное заполнение €чеек стека Ђснизу-вверхї, при этом SP всегда адресует вершину стека. ѕо команде RETURN текущее содержимое SP выдаетс€ на шину ј, и по шине D производитс€ считывание с вершины стека последнего записанного значени€ PC. ѕосле этого содержимое SP увеличиваетс€ на 1, адресу€ предыдущее значение PC, хран€щеес€ в стеке. “ак как ќ«” обычно имеет значительный объем, то дл€ размещени€ стека можно выделить достаточно большое количество €чеек пам€ти, обеспечива€ необходимый уровень вложени€ подпрограмм.

–исунок8.1.6.2 ¬арианты реализации стека: регистровый стек (а) и стек, реализуемый в ќ«” (б).

8.1.7 ‘ункционирование ћѕ— при обслуживании прерываний и исключений

ѕри работе микропроцессорной системы часто возникают ситуации, когда требуетс€ прервать выполнение текущей программы и перейти к подпрограмме, обеспечивающей необходимую реакцию системы на создавшиес€ обсто€тельства. “акие ситуации называютс€ прерывани€ми или исключени€ми в зависимости от причин, вызывающих их возникновение.

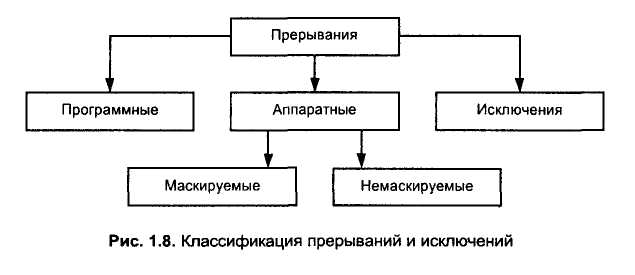

ѕрерывани€ми (interruption) €вл€ютс€ ситуации, возникающие при поступлении соответствующих команд (программные прерывани€) или сигналов от внешних устройств (аппаратные прерывани€). »сключени€ми (exception) €вл€ютс€ нештатные ситуации (ошибки), возникающие при работе процессора. ѕри вы€влении таких ошибок соответствующие блоки, контролирующие работу процессора, вырабатывают внутренние сигналы запроса, обеспечивающие вызов необходимой подпрограммы обслуживани€. лассификаци€ прерываний и исключений приведена на рисунке 8.1.7.1.

–исунок 8.1.7.1. лассифика≠ци€ прерываний и исключений

¬о всех этих ситуаци€х микропроцессор завершает выполнение очередной команды и заносит в стек текущее содержимое программного счетчика PC, которое €вл€етс€ адресом возврата к прерванной программе после реализации подпрограммы обслуживани€, и содержимое регистра состо€ний SR. ≈сли запрос прерывани€ поступает от внешнего устройства, то процессор формирует сигнал подтверждени€ прерывани€, который информирует это устройство, что начато обслуживание данного запроса. «атем в PC загружаетс€ из пам€ти вектор прерывани€ Ve Ц начальный адрес соответствующей подпрограммы обслуживани€. Ёти вектора €вл€ютс€ входами в подпрограммы обслуживани€ и хран€тс€ в таблице векторов прерываний, котора€ обычно записываетс€ в ќ«”. –азмер таблицы зависит от числа типов обслуживаемых прерываний и исключений. ¬ простейших микропроцессорах это число составл€ет несколько единиц, а дл€ микропроцессоров семейства Pentium или MC68000 обеспечиваетс€ возможность реализации до 256 различных подпрограмм обслуживани€.

«авершаетс€ подпрограмма обслуживани€ специальной командой возврата из прерывани€ IRET, котора€ выбирает из стека хранившеес€ содержимое PC и SR и загружает его обратно в эти регистры, обеспечива€ возвращение к выполнению прерванной программы.

ѕрограммные прерывани€ реализуютс€ при поступлении специальных команд (INTn, INT3, INTO дл€ микропроцессоров Pentium). Ёти команды вызывают переход к выполнению стандартных подпрограмм обслуживани€, дл€ размещени€ которых выдел€ютс€ определенные позиции в ќ«”. “аким образом, при вызове подпрограмм обслуживани€ реализуетс€ обращение к фиксированным адресам.

ѕричинами аппаратных прерываний €вл€ютс€ запросы от различных внешних (периферийных) устройств системы. Ёти запросы поступают на внешние выводы микропроцессора или формируютс€ периферийными устройствами, размещенными на одном кристалле с процессором. јппаратные прерывани€ могут быть маскируемые или немаскируемые.

«апросы маскируемых прерываний обслуживаютс€ только в том случае, если соответствующий бит управлени€ I в регистре состо€ни€ SR, который называетс€ маской преры≠ваний, имеет значение 1. ¬ процессорах Pentium это бит IF в регистре EFLAGS. — помощью специальных команд значение этого бита может быть установлено в 1 или сброшено в 0. “аким образом, можно разрешить или запретить обслуживание поступивших аппаратных прерываний при выполнении определенных программ или их фрагментов. ѕри одно≠временном поступлении нескольких запросов обслуживание реализуетс€ в соответствии с их приоритетом. ¬ р€де микропроцессорных систем дл€ обеспечени€ приоритетного обслуживани€ запросов от многих внешних устройств включаютс€ специальные микросхемы Ц контроллеры прерываний. Ќекоторые типы микропроцессоров имеют внутренние контроллеры дл€ организации приоритетных прерываний.

Ќемаскируемые запросы прерывани€ обслуживаютс€ в первоочередном пор€дке и не могут быть маскированы. ќбычно микропроцессор имеет один вход дл€ подачи немаскируемых запросов, которые формируютс€ при возникновении каких-либо аварийных ситуаций. „аще всего этот вход используетс€ дл€ контрол€ напр€жени€ питани€. ≈сли напр€жение питани€ выходит за допустимые пределы, то специальный датчик вырабатывает немаскируемый запрос прерывани€, поступающий в микропроцессор. ѕри этом источник питани€ должен некоторое врем€ (пор€дка 10 мс) сохран€ть необходимый уровень напр€жени€ питани€, в течение которого микропроцессор выполн€ет подпрог≠рамму перезаписи на магнитный диск информации, достаточной дл€ продолжени€ прерванной программы после восстановлени€ нормального режима питани€.

ƒл€ передачи сигналов запроса и подтверждени€ прерывани€ между микропроцес≠сором и внешними устройствами или контроллером прерываний используютс€ соответствующие линии шины управлени€ —.

ѕричинами исключений могут быть различные ошибки и нештатные ситуации, возникающие при работе системы. –азличные типы микропроцессоров контролируют разные варианты такого рода ситуаций. “ипичными причинами исключений €вл€ютс€, например, использование нулевого делител€ при выполнении команды делени€ (деление на 0), выборка неправильного кода команды, выход за границы разрешенного фрагмента пам€ти; поступление команд, выполнение которых запрещено при данном режиме функционировани€ микропроцессора и р€д других.

8.1.8 ‘ункционирование ћѕ— в режиме пр€мого доступа к пам€ти

–ежим пр€мого доступа к пам€ти DMA (Direct Memory Access) используетс€, если необходимо произвести пересылку значительного массива информации между ќ«” и каким-либо внешним устройством, которое подает в систему соответствующий запрос. –еализаци€ такой пересылки с помощью соответствующей программы обмена требует выполнени€ отдельной команды пересылки дл€ передачи каждого байта или слова. ѕри этом необходим определенный объем пам€ти дл€ хранени€ программы и требуетс€ значительное врем€ дл€ ее выполнени€.

¬ большинстве современных микропроцессорных систем пересылка массивов информации обеспечиваетс€ с помощью специальных устройств - контроллеров DMA, которые реализуют режим пр€мого доступа к пам€ти. ѕри поступлении запроса от внешнего устройства контроллер выдает соответствующий сигнал микропроцессору. ѕолучив этот сигнал, микропроцессор завершает очередной цикл обмена по системной шине и отключаетс€ от нее, то есть переводит свои выводы, подключенные к шинам A, D и лини≠€м управлени€ ќ«” и внешними устройствами, в отключенное (высокоимпедансное) состо€ние. ѕри этом микропроцессор выдает контроллеру DMA сигнал разрешени€ на реализацию пр€мого доступа. ѕолучив этот сигнал, контроллер принимает на себ€ управление системой. ќн выдает на шину ј адреса €чеек ќ«”, с которыми выполн€етс€ текущий цикл обмена, формирует необходимые сигналы, определ€ющие режим работы ќ«” (запись или считывание) и интерфейсного устройства, через которое производитс€ пе≠ресылка информации (ввод или вывод).

ѕередача сигналов запроса и подтверждени€ пр€мого доступа к пам€ти между мик≠ропроцессором и контроллером DMA производитс€ по соответствующим лини€м шины управлени€ —.

ѕредварительно контроллер DMA программируетс€ дл€ выполнени€ указанных функций. ¬ него ввод€тс€ начальные адреса массивов пам€ти в ќ«”, с которых начинаетс€ процесс обмена, и размеры массивов, подлежащего пересылке. ќбычно контроллер DMA обслуживает запросы от нескольких внешних устройств, поэтому он программируетс€ на реализацию определенного приоритета их обслуживани€ в случае одновременного поступлени€ нескольких запросов. ѕрограммирование контроллера производитс€ путем посылки ему необходимых управл€ющих сообщений. Ёти сообщени€ обычно предвари≠тельно ввод€тс€ в контроллер от микропроцессора, когда он выполн€ет специальную программу инициализации контроллера DMA.